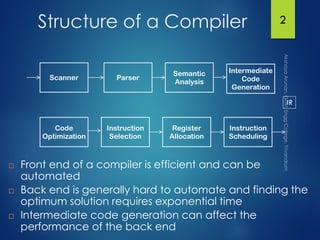

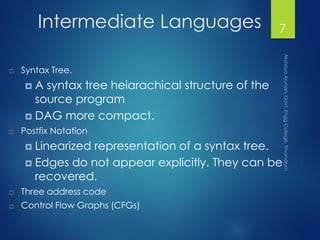

The document discusses intermediate code generation in compilers. It aims to generate a machine-independent intermediate form (IR) that is suitable for optimization and portability. The IR facilitates retargeting compilers to new machines and enables machine-independent code optimization. Common IR representations include abstract syntax trees, directed acyclic graphs, control flow graphs, postfix notation, and three-address code. Three-address code is a simple representation where instructions have at most three operands. It allows efficient code manipulation and optimization.

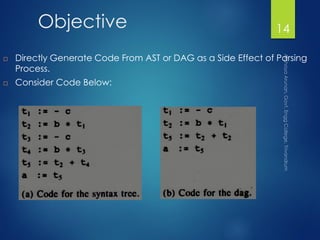

![Types of Three Address

Statements

Indexed Assignments of Form:

X := Y[i] (Set X to i-th memory location of Y)

X[i] := Y (Set i-th memory location of X to Y)

Note the limit of 3 Addresses (X, Y, i)

Cannot do: x[i] := y[j]; (4 addresses!)

Address and Pointer Assignments of Form:

X := & Y (X set to the Address of Y)

X := * Y (X set to the contents pointed to by Y)

* X := Y (Contents of X set to Value of Y)

21](https://image.slidesharecdn.com/intermediatecodegeneration-160604185209/85/Intermediate-code-generation-21-320.jpg)

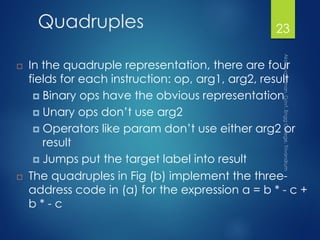

![Triples

A triple has only three fields for each instruction:op,arg1,

arg2

The result of an operation x op y is referred to by its

position.

Triples are equivalent to signatures of nodes in DAG or

syntax trees.

Triples and DAGs are equivalent representations only for

expressions; they are not equivalent for control flow.

Ternary operations like x[i] = y requires two entries in the

triple structure, similarly for x = y[i].

Moving around an instruction during optimization is a

problem

25](https://image.slidesharecdn.com/intermediatecodegeneration-160604185209/85/Intermediate-code-generation-25-320.jpg)