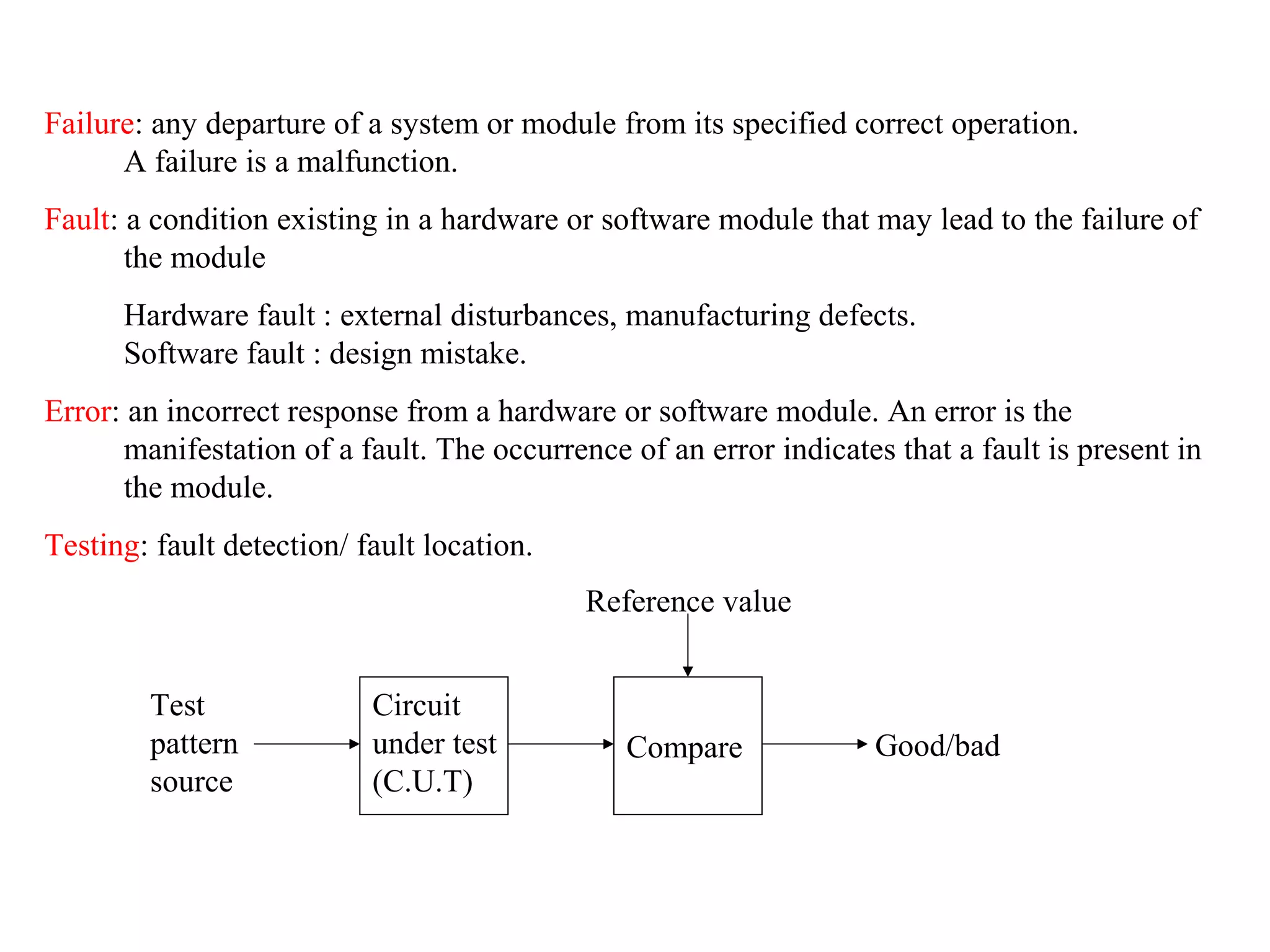

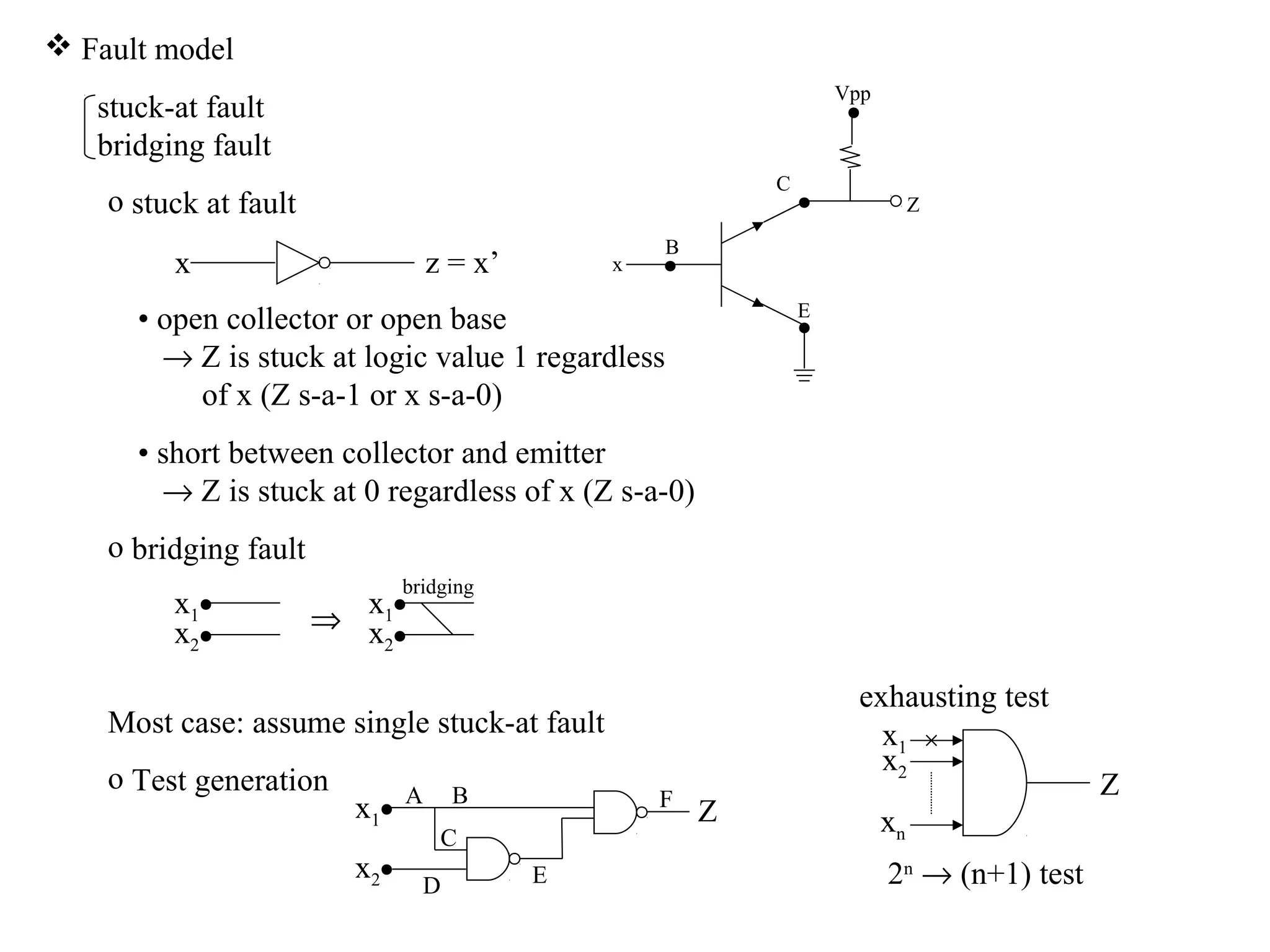

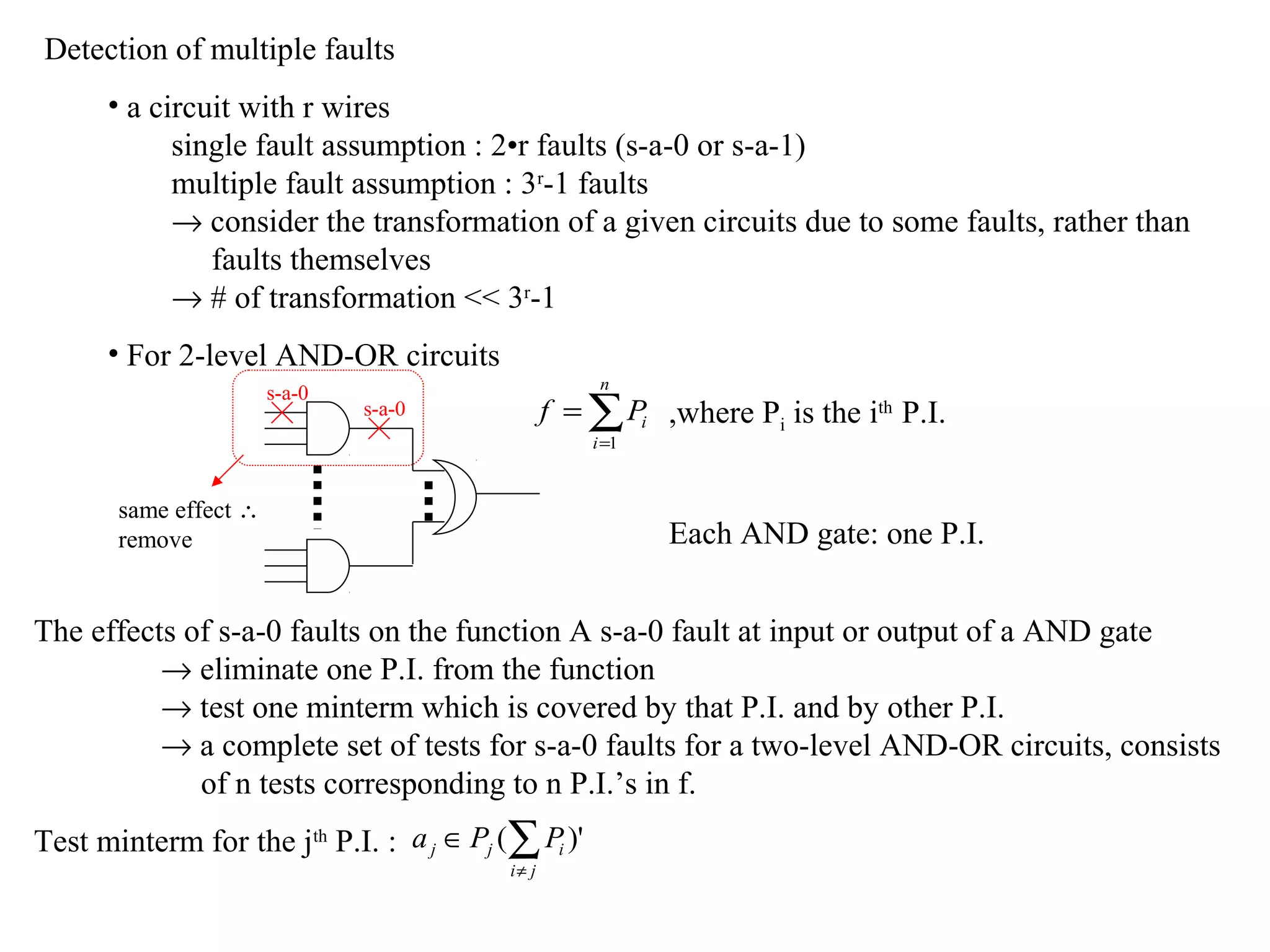

1) Testing digital circuits involves detecting faults that could lead to failures or errors. Common faults include stuck-at faults where a line is stuck at logic 0 or 1.

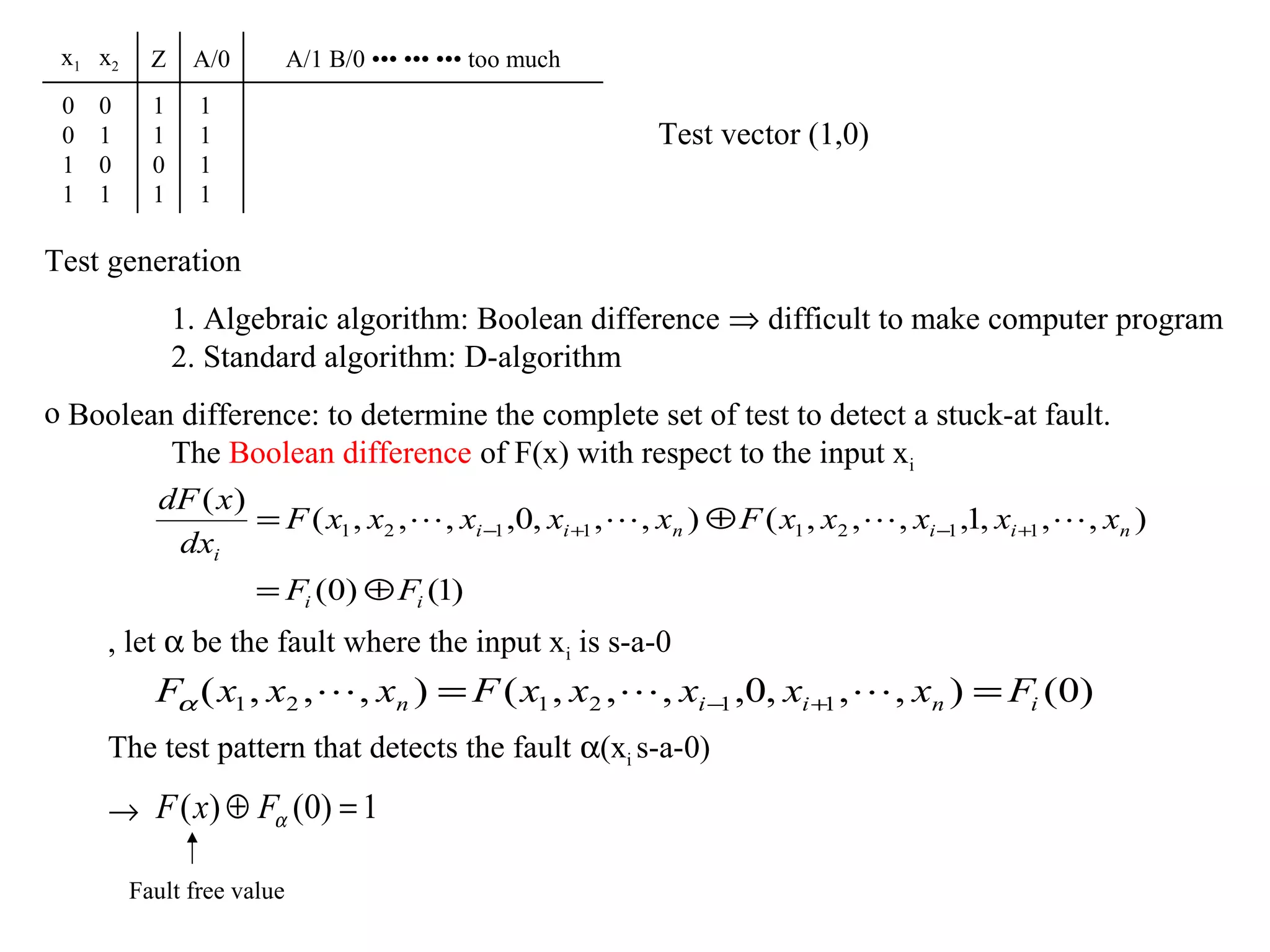

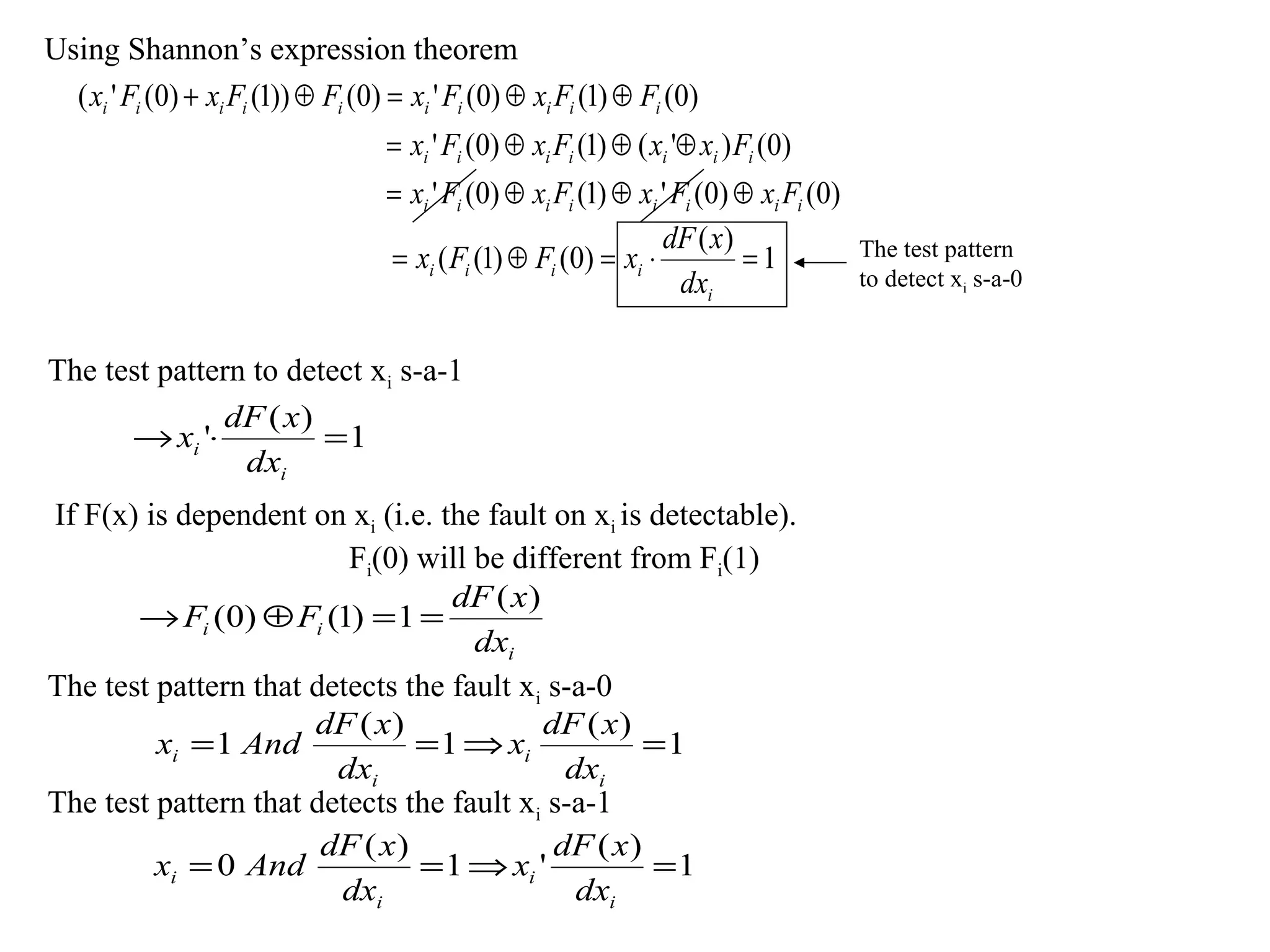

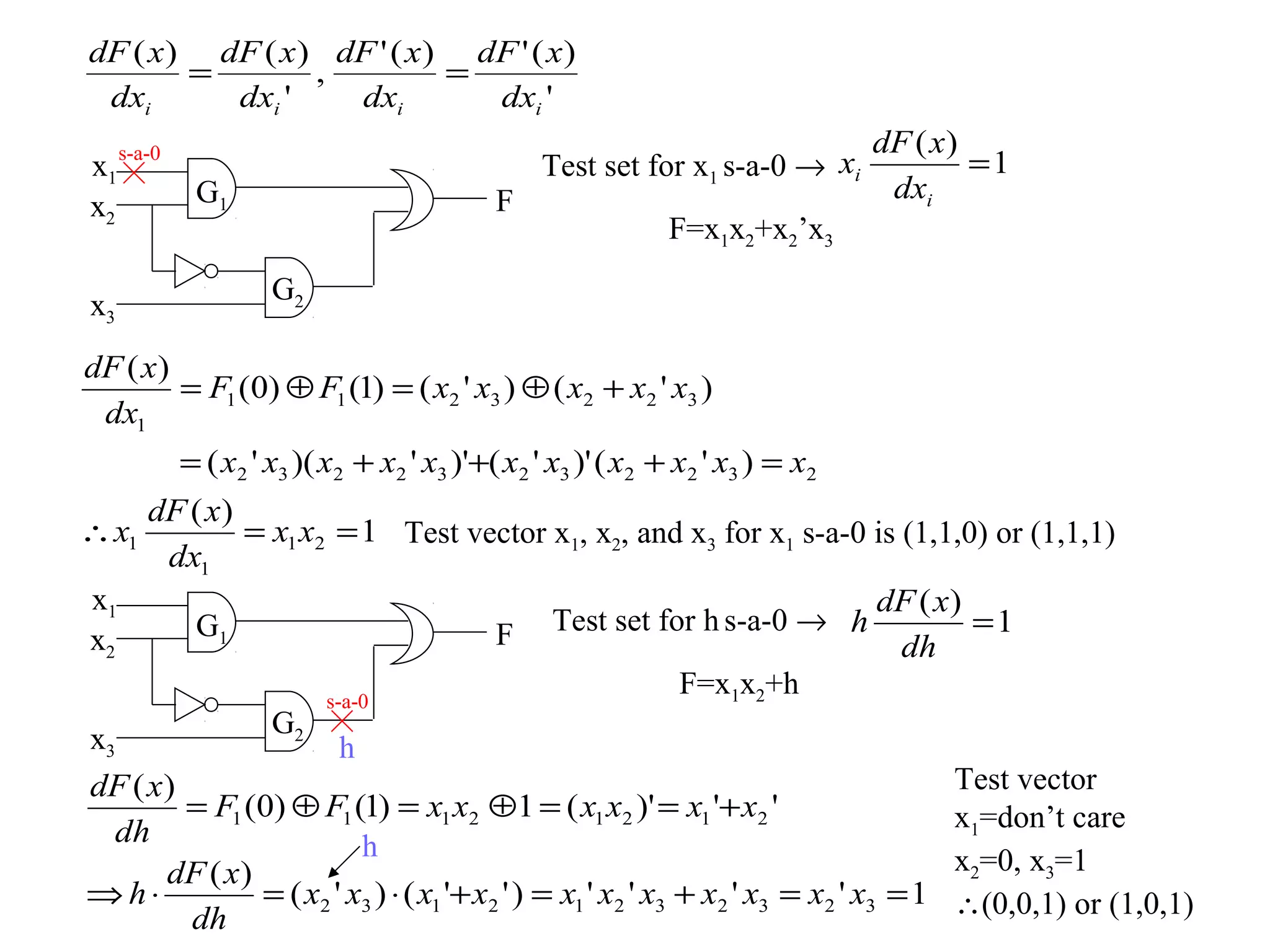

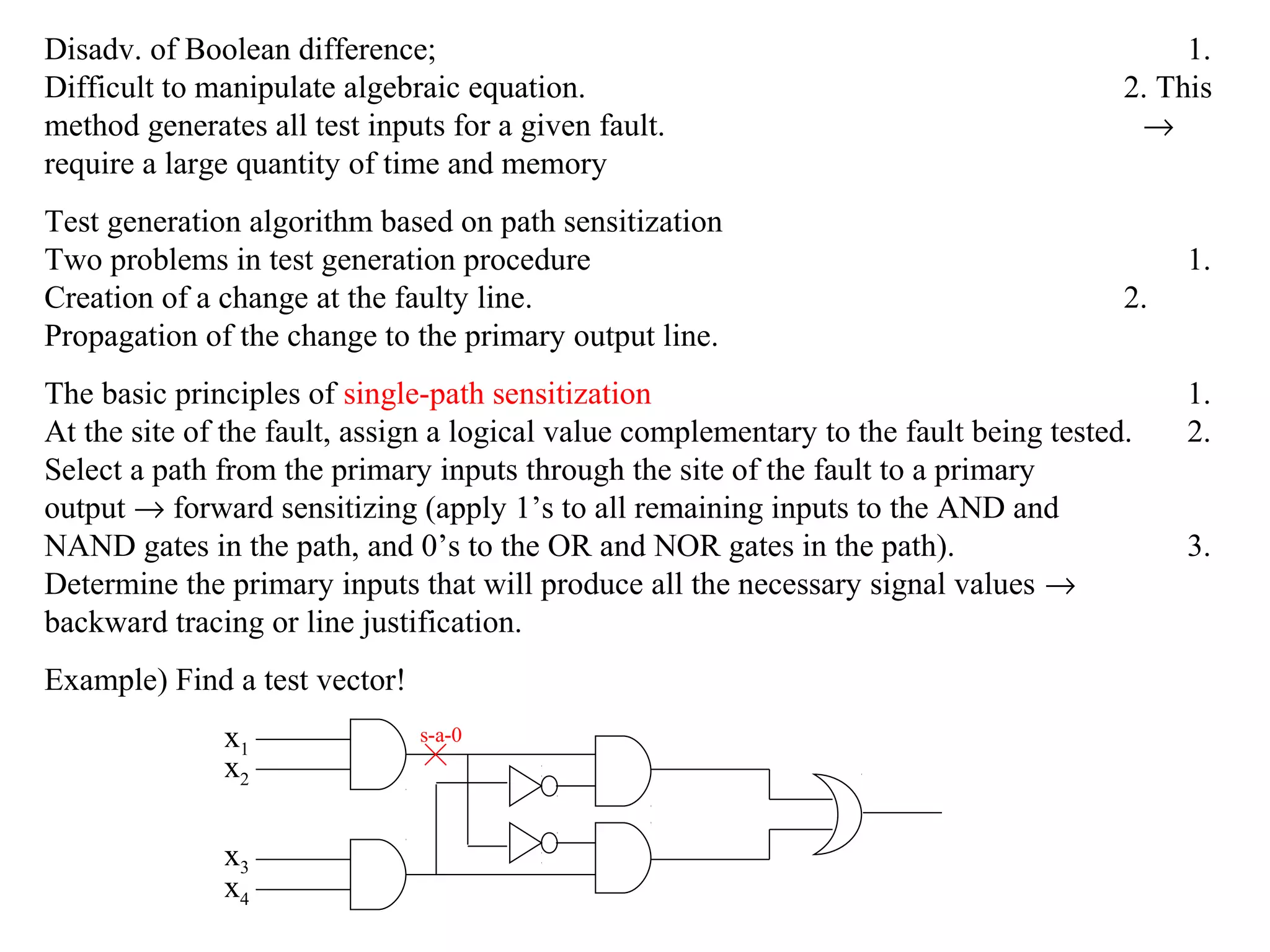

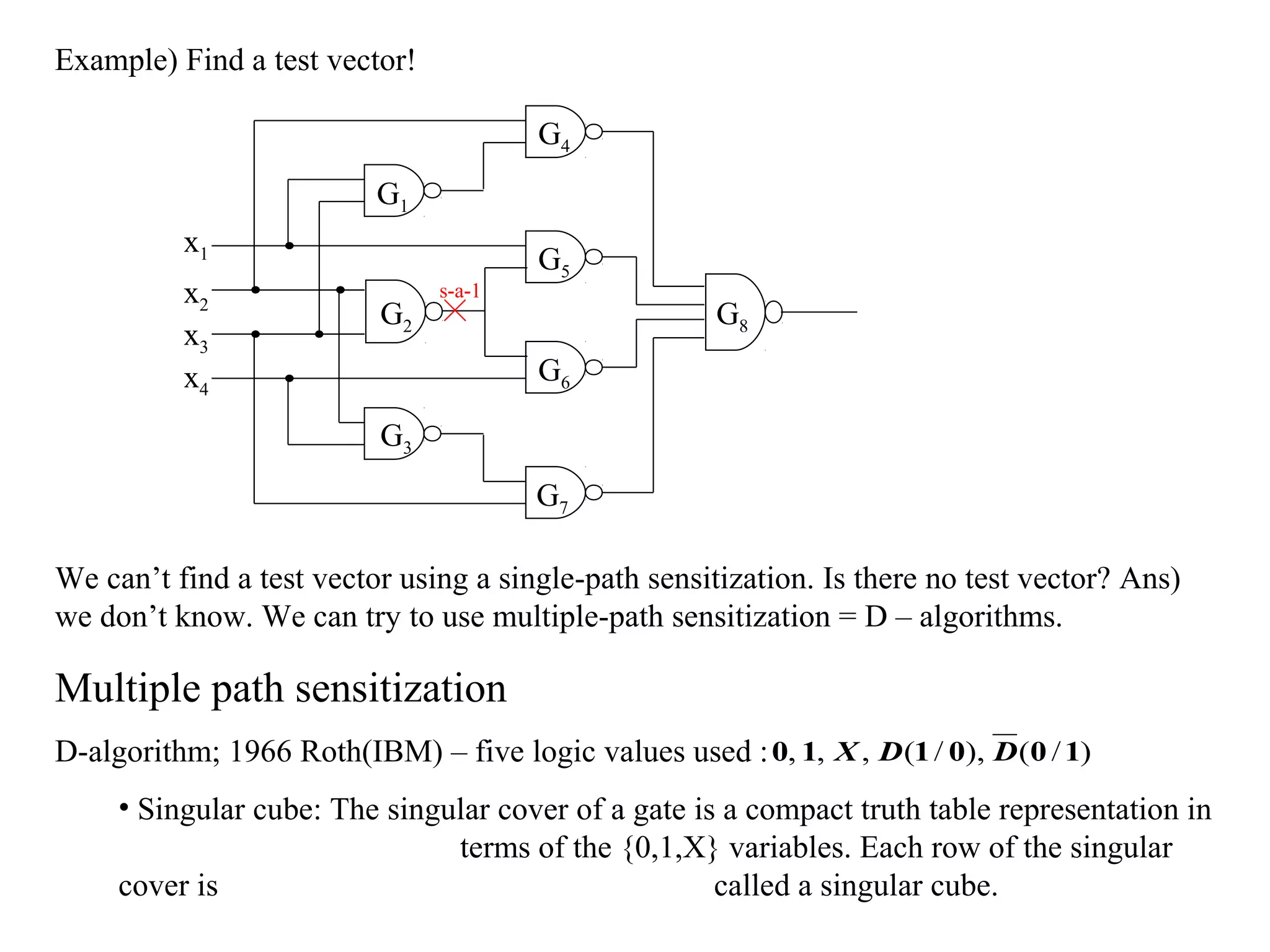

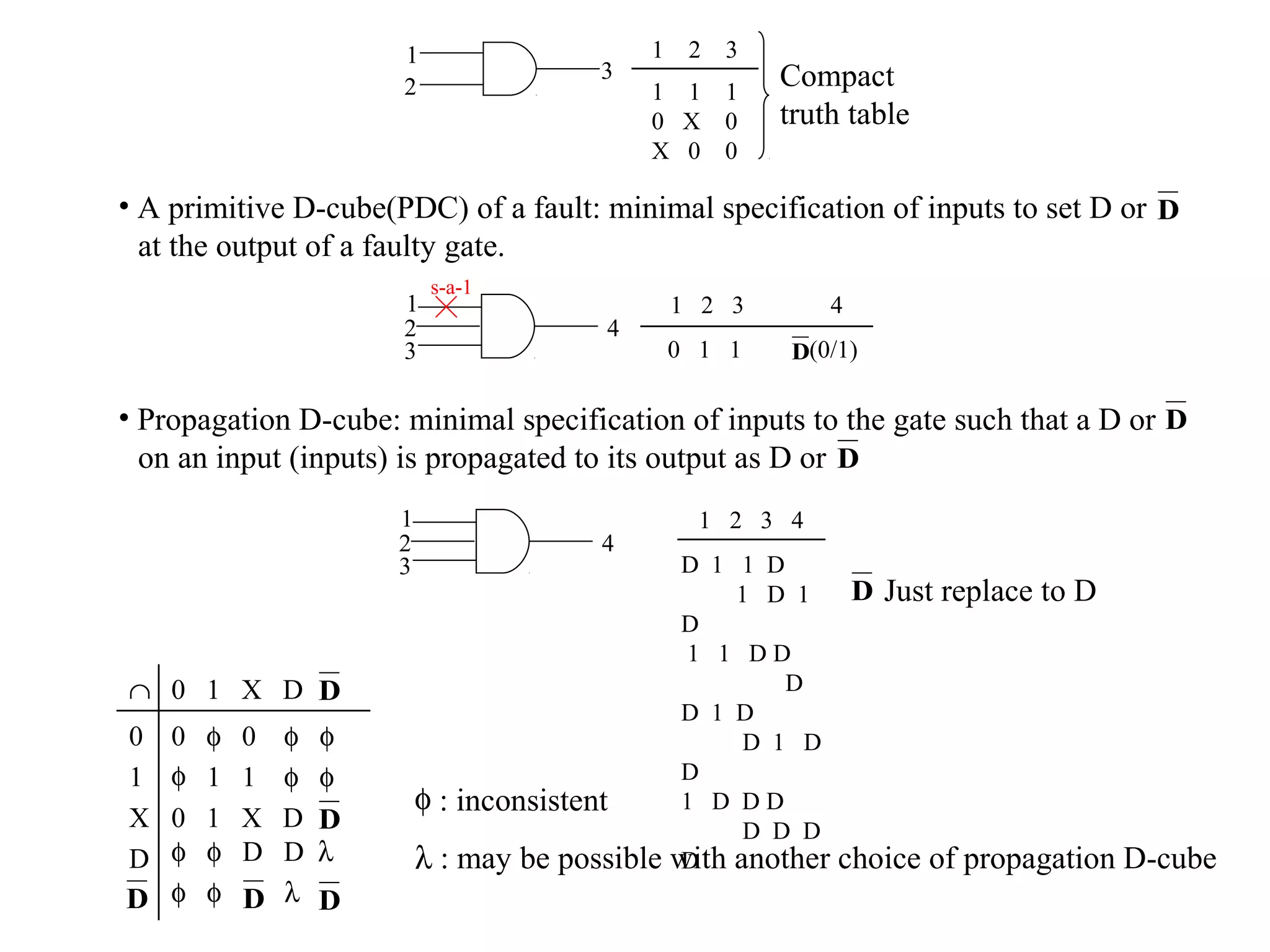

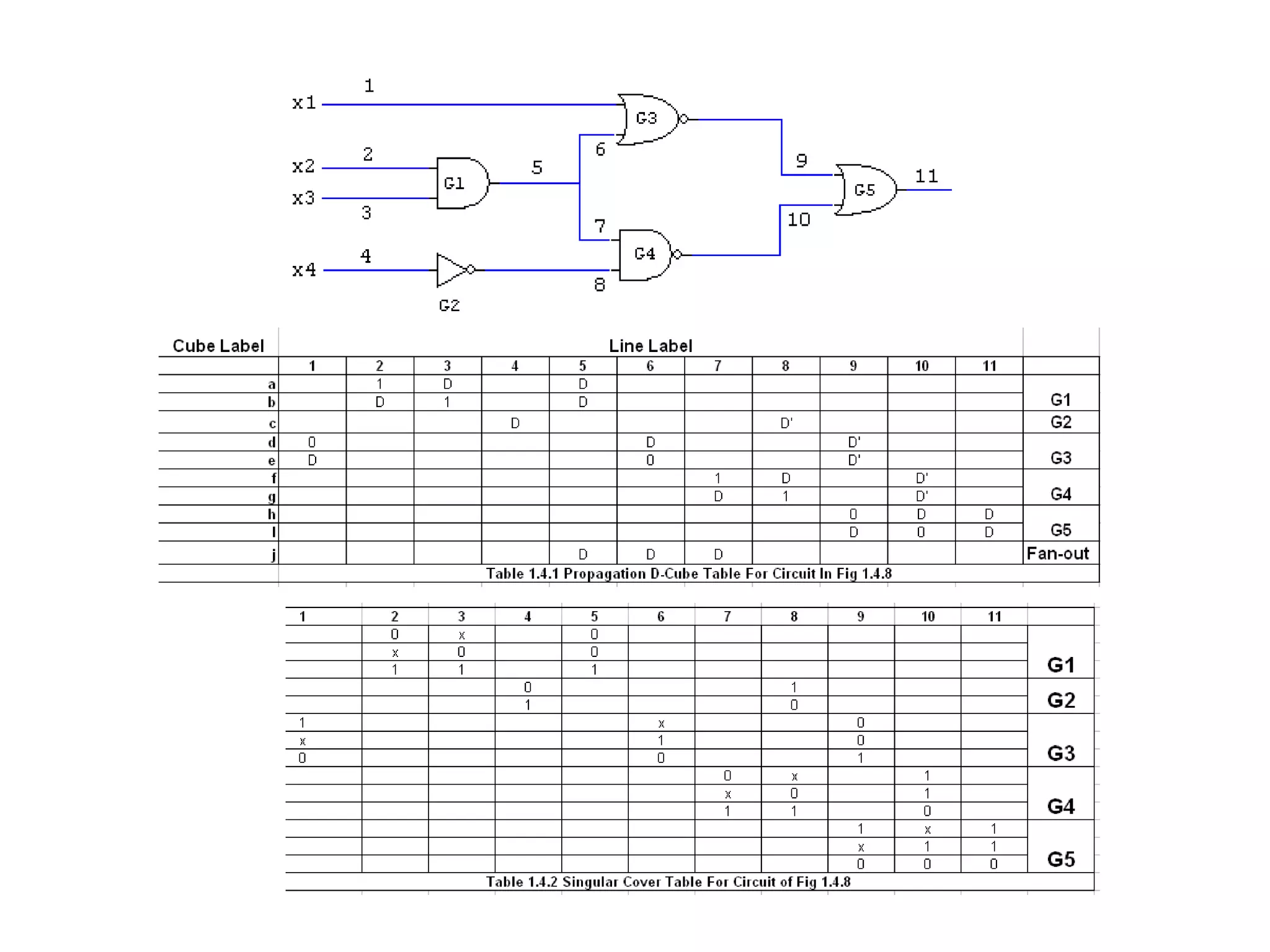

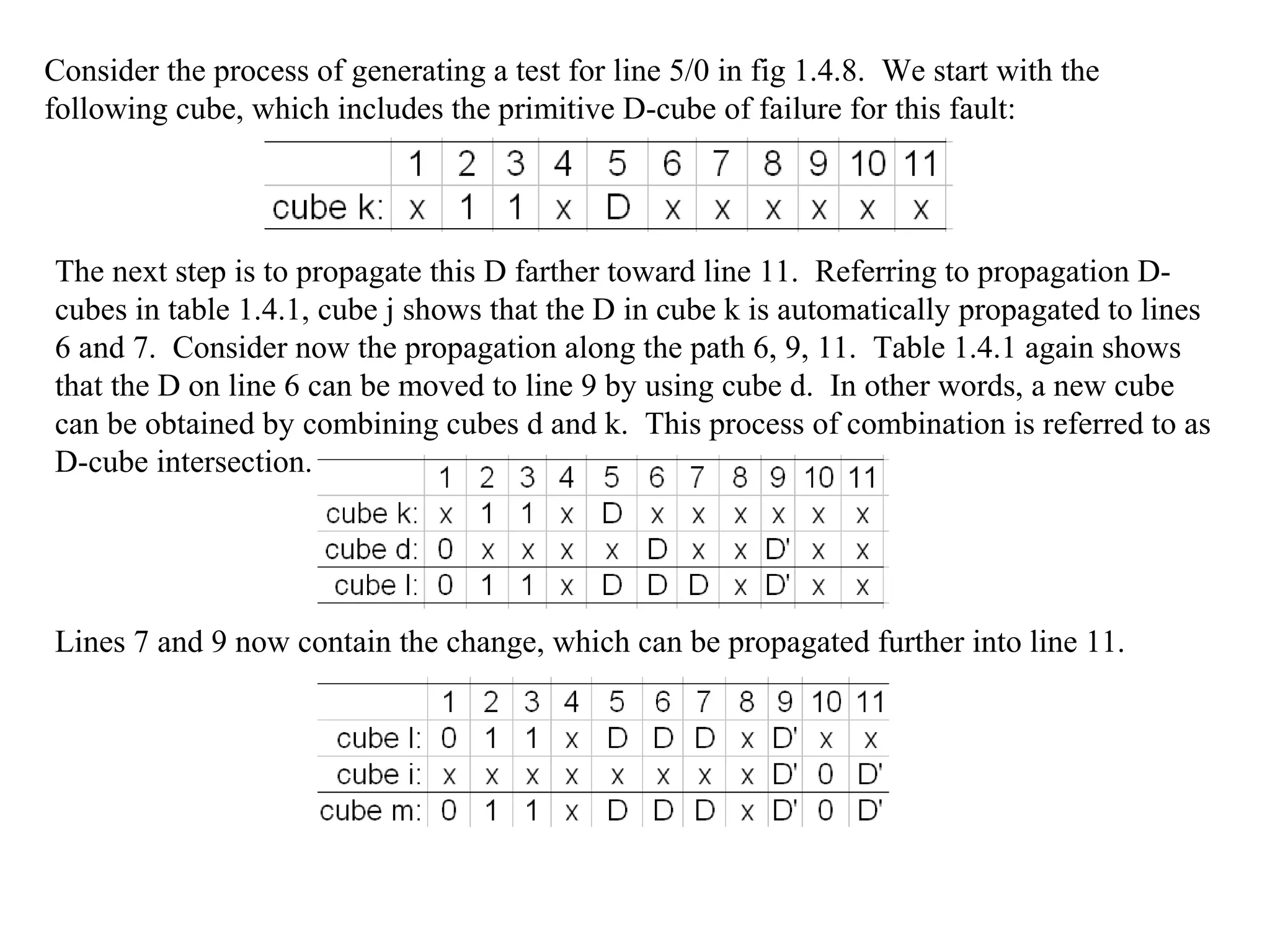

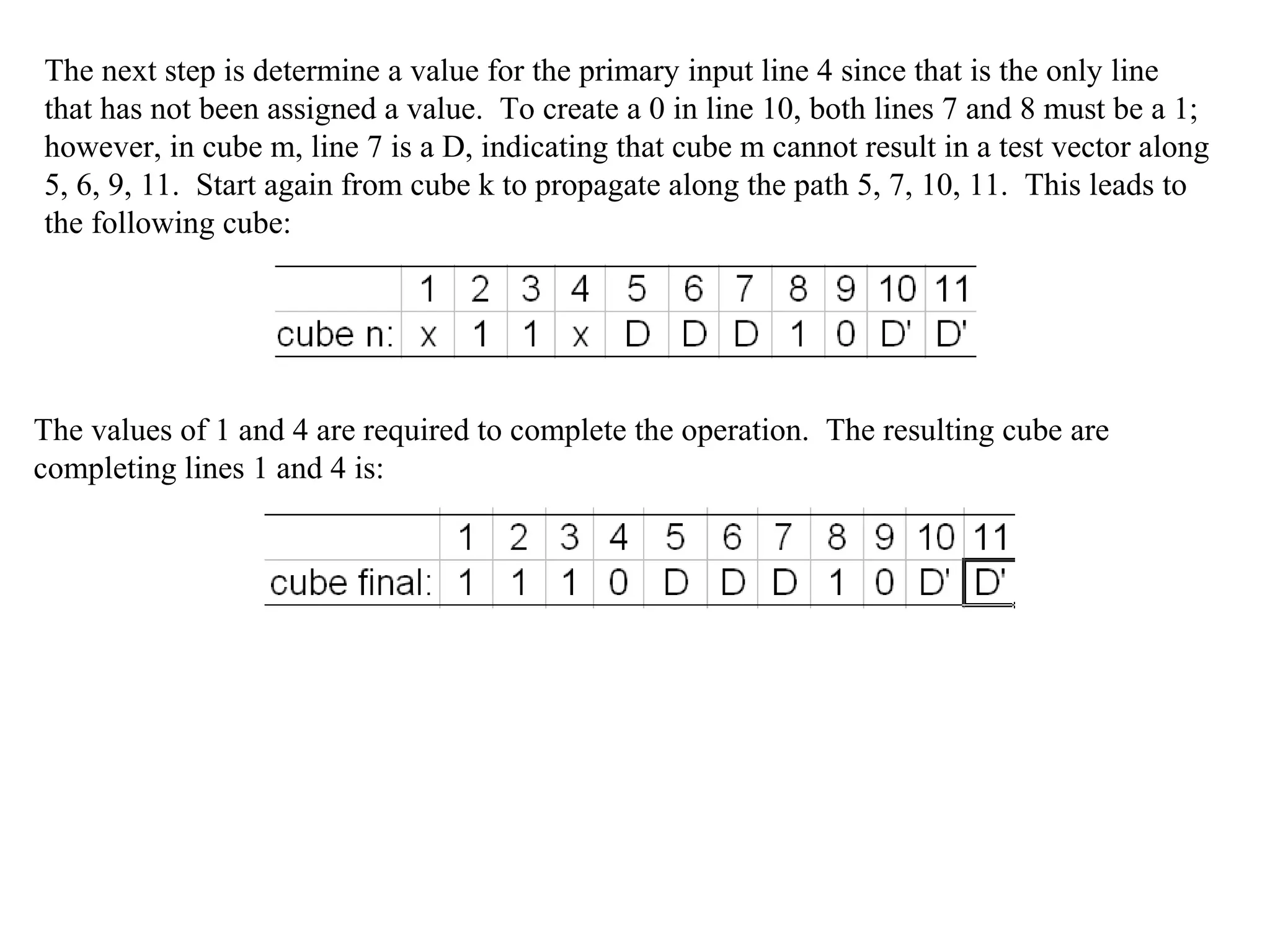

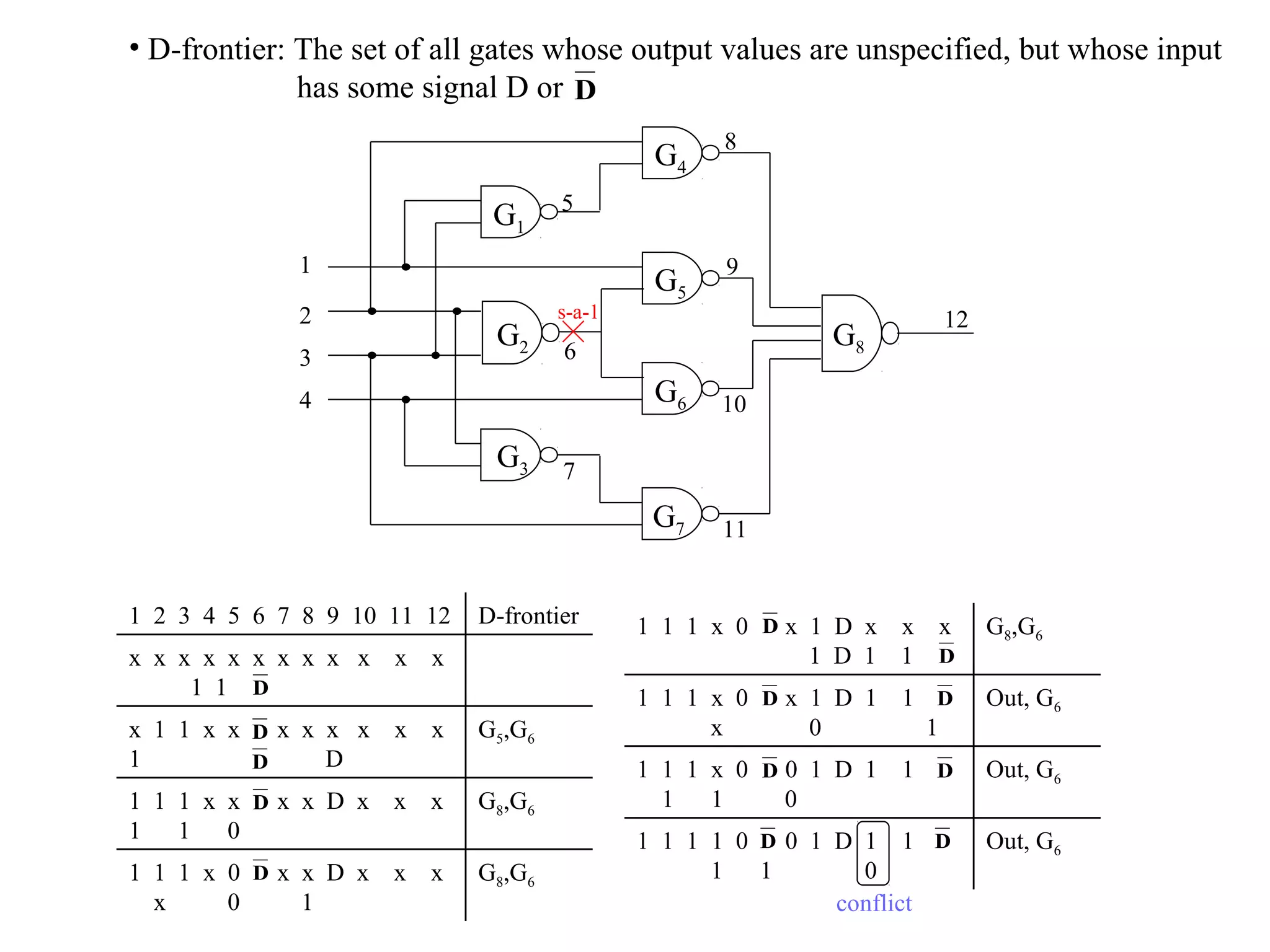

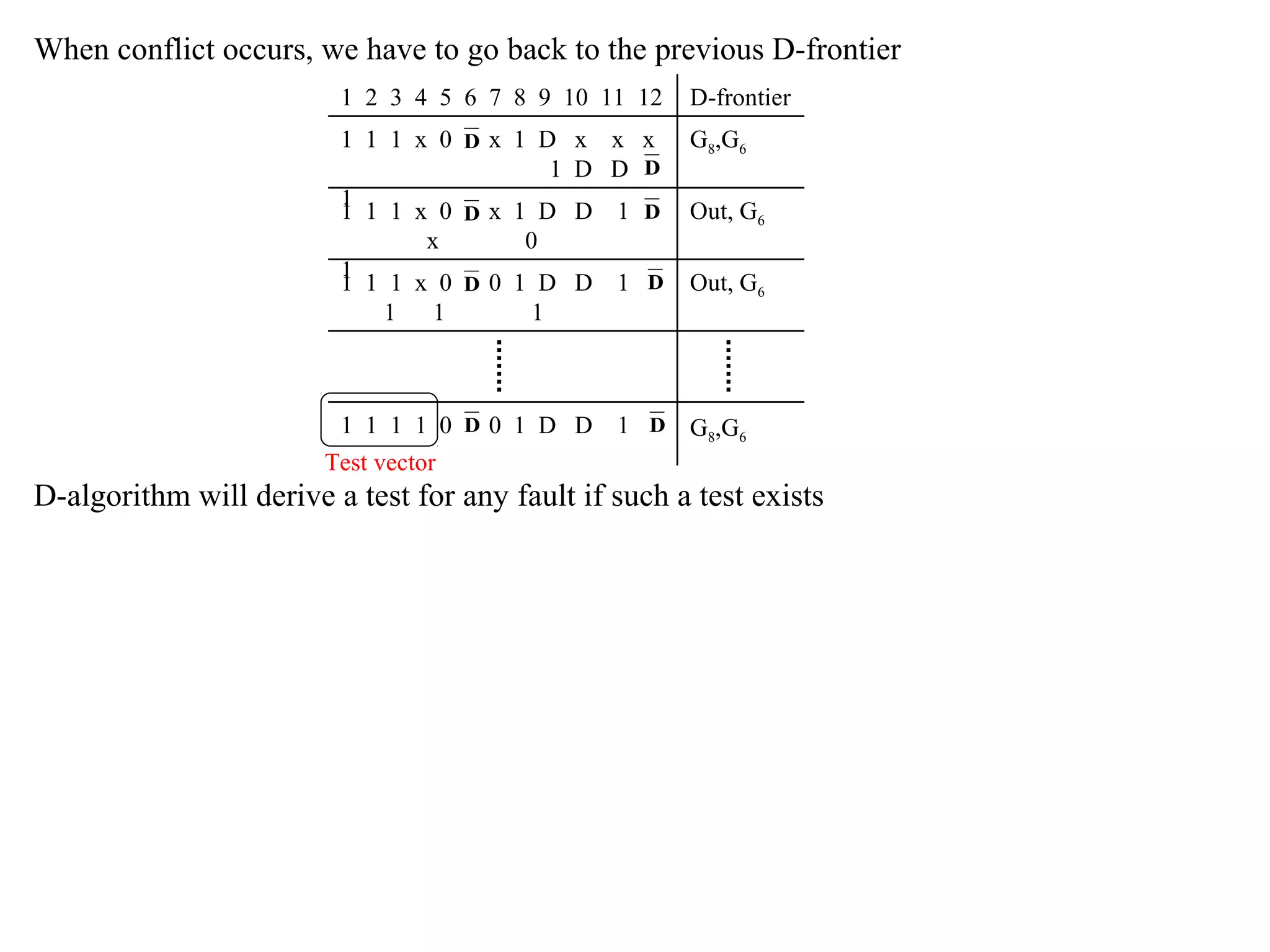

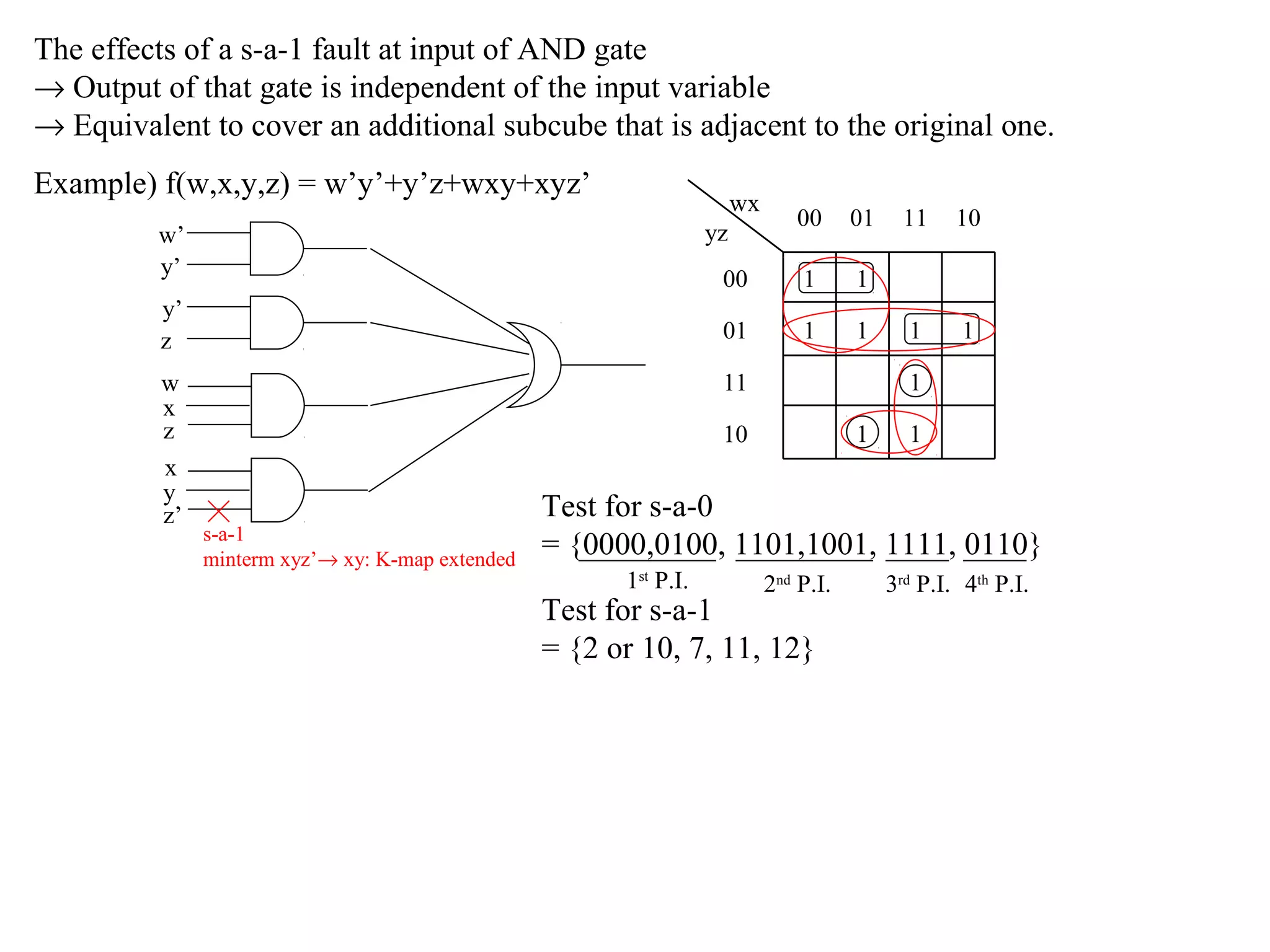

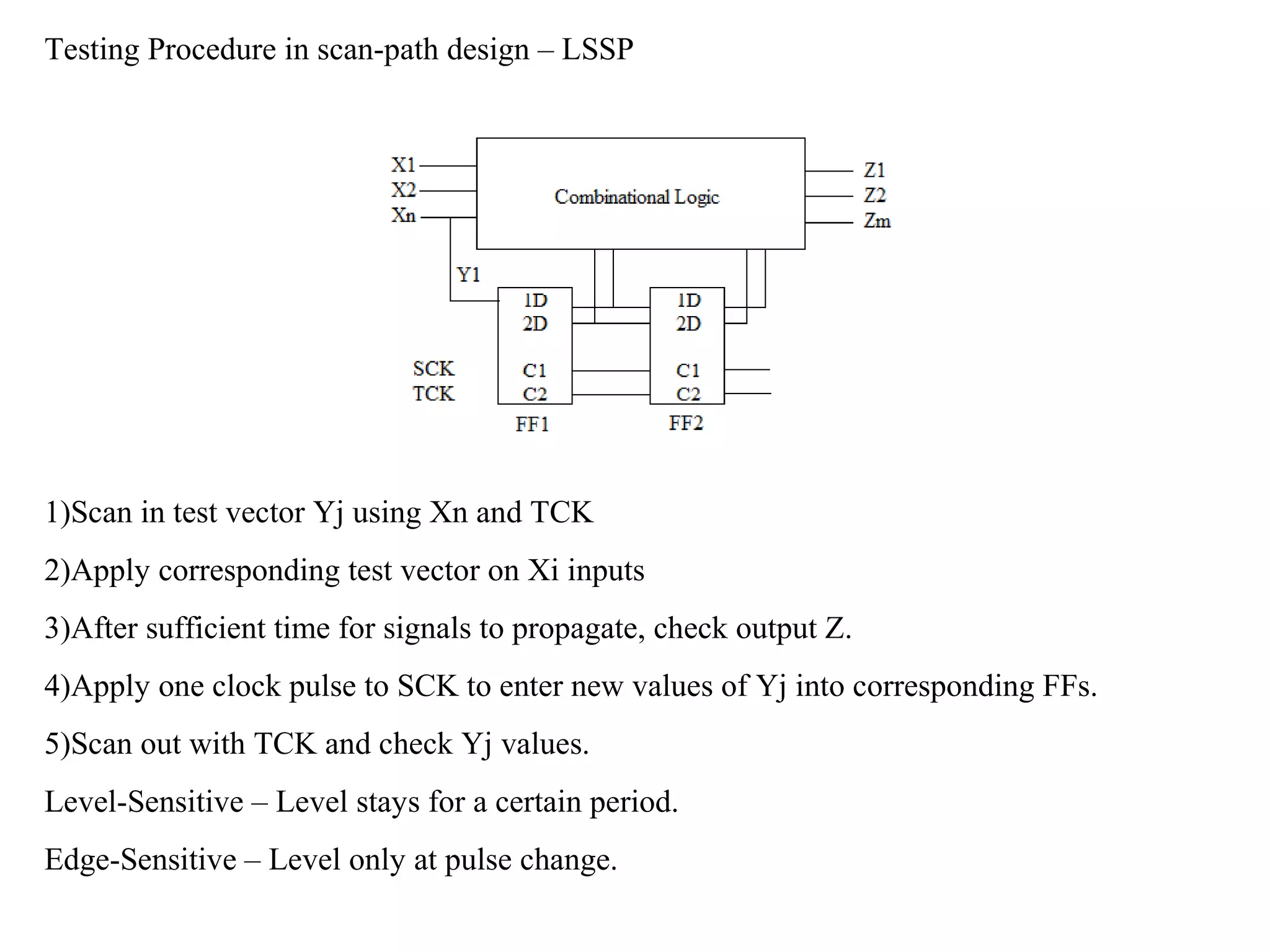

2) Test patterns are generated to detect faults by sensitizing a path from the fault to an output and justifying input values. Boolean difference and D-algorithms are used.

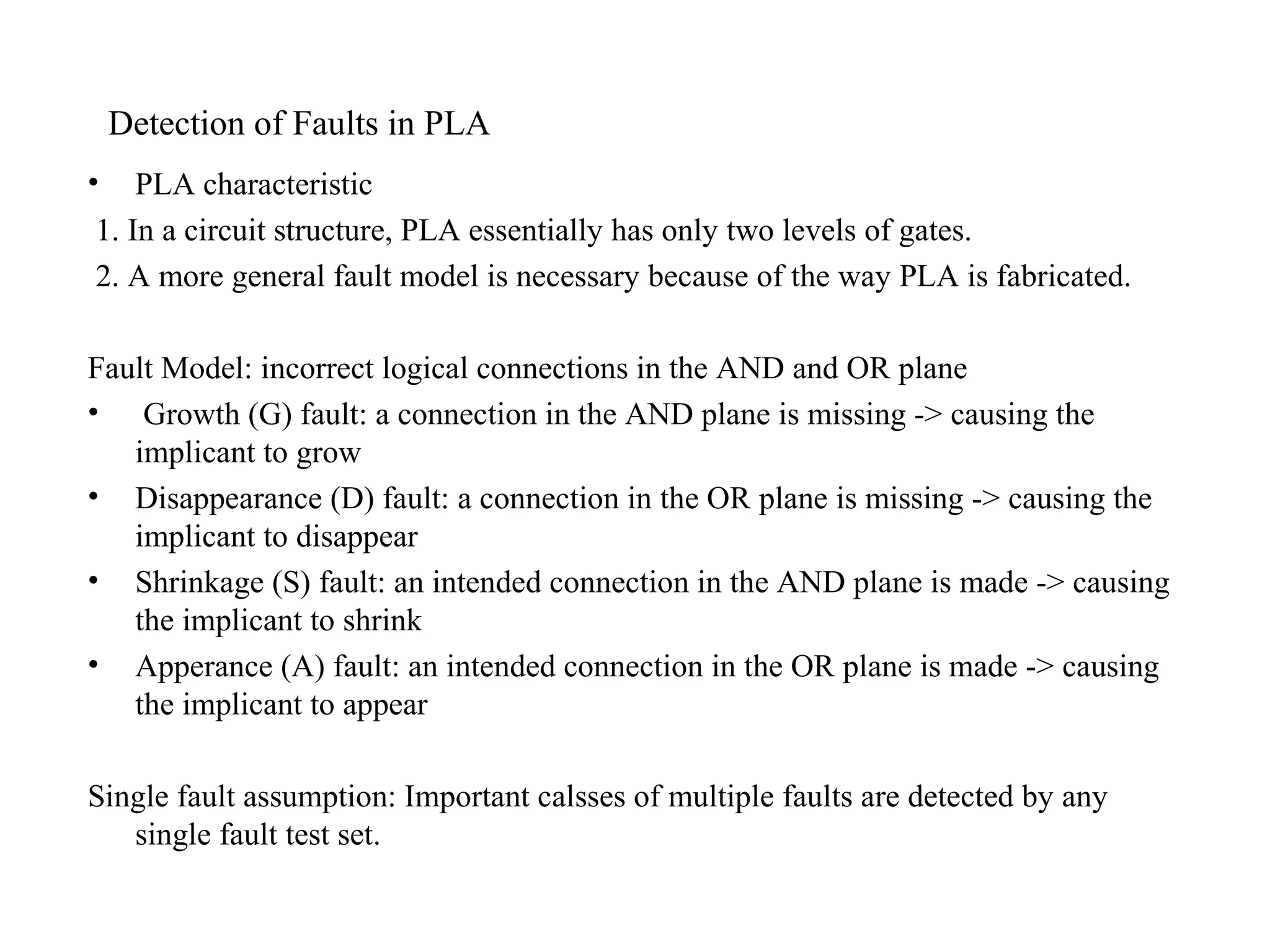

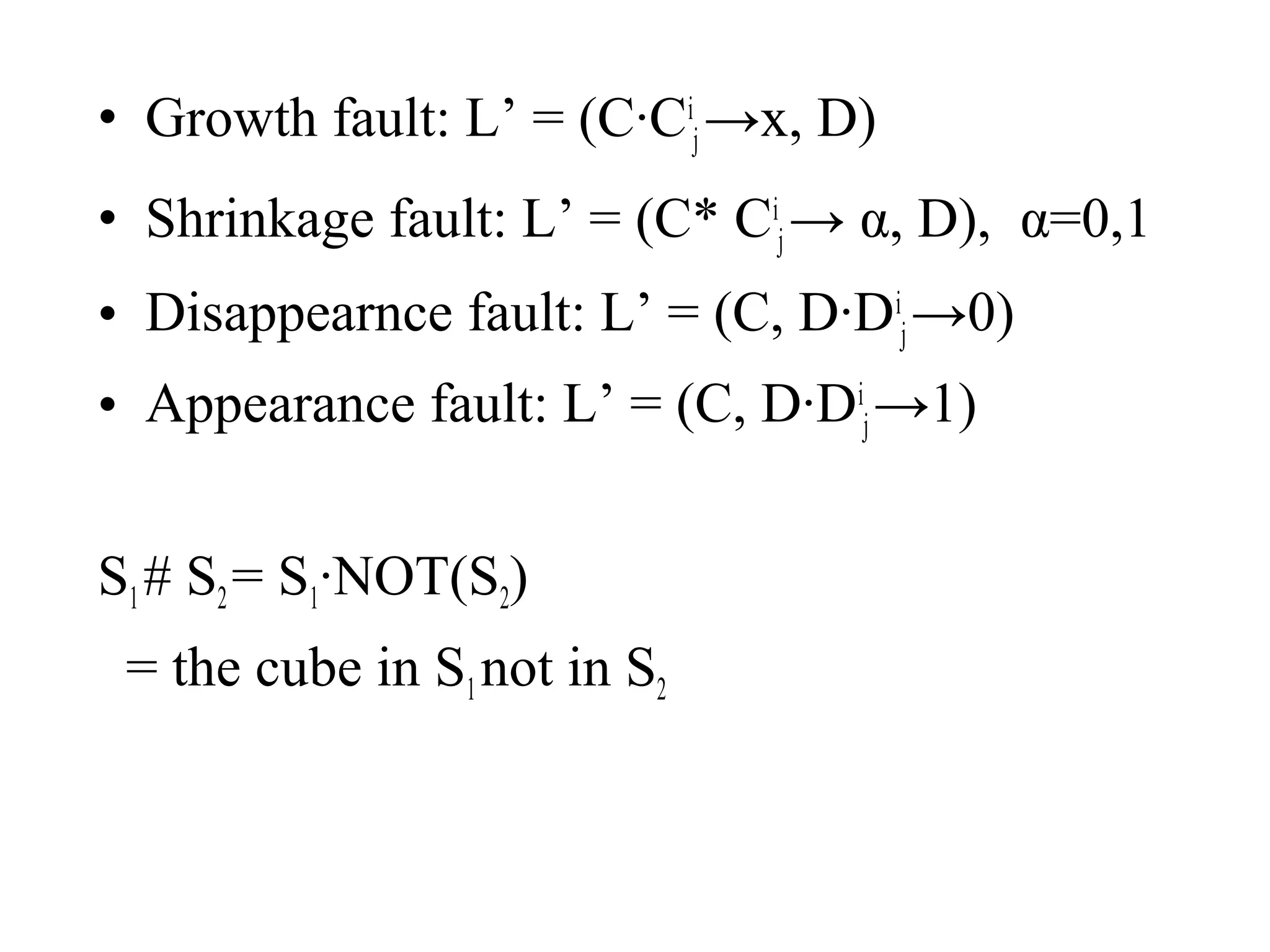

3) Faults in PLA circuits include growth, disappearance, shrinkage and appearance faults affecting the AND and OR planes. Their effect is modeled and tests generated.

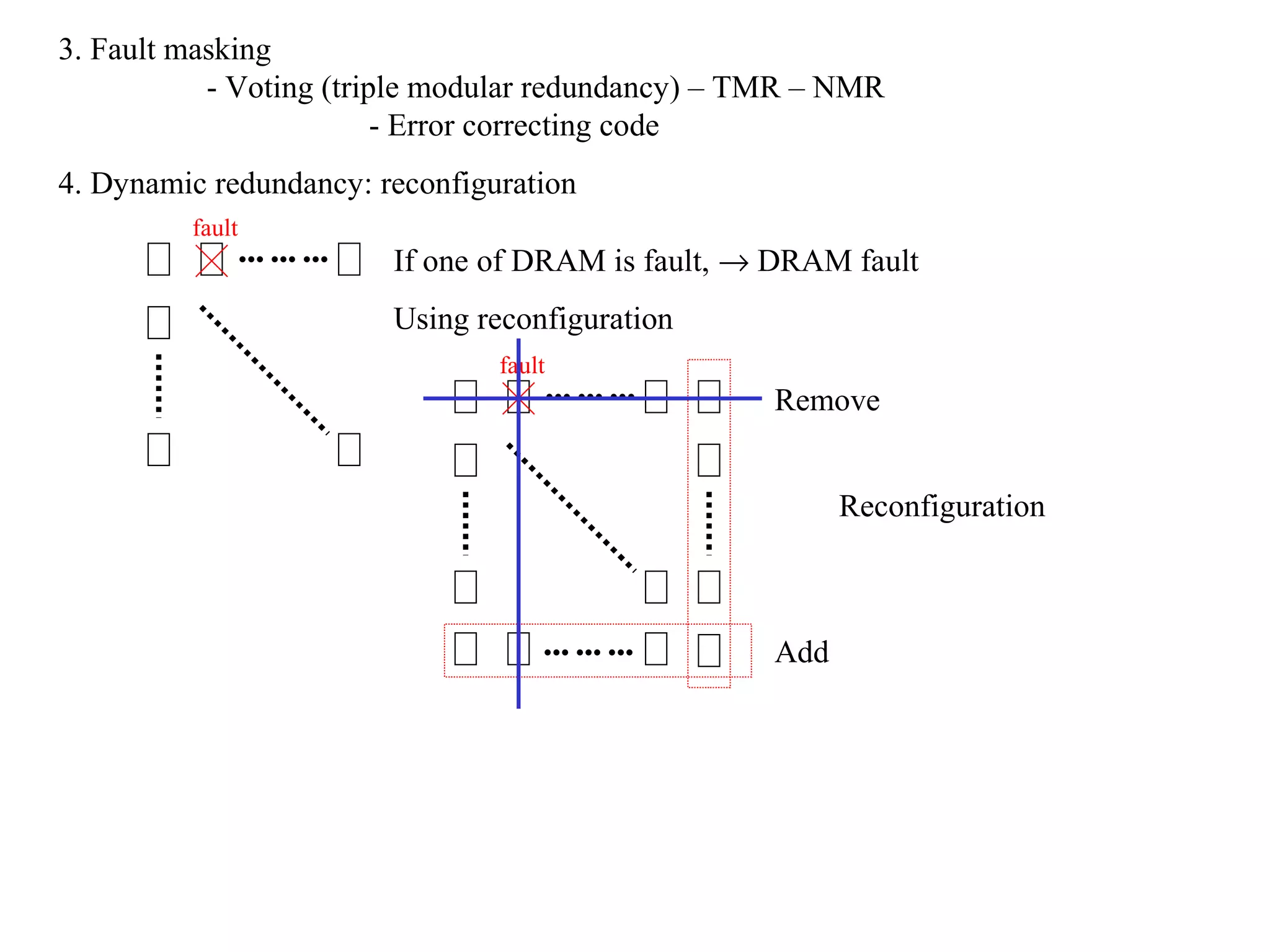

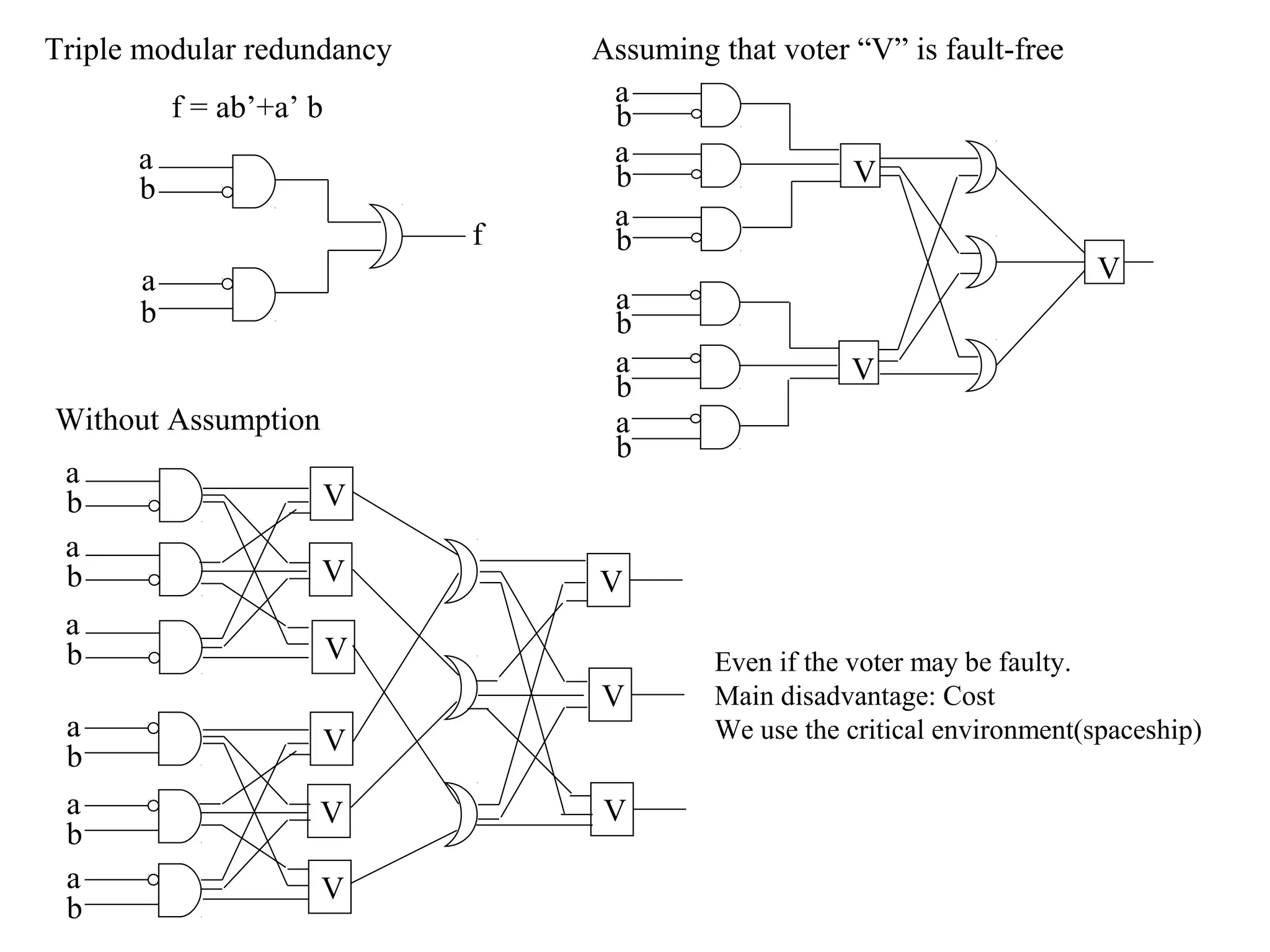

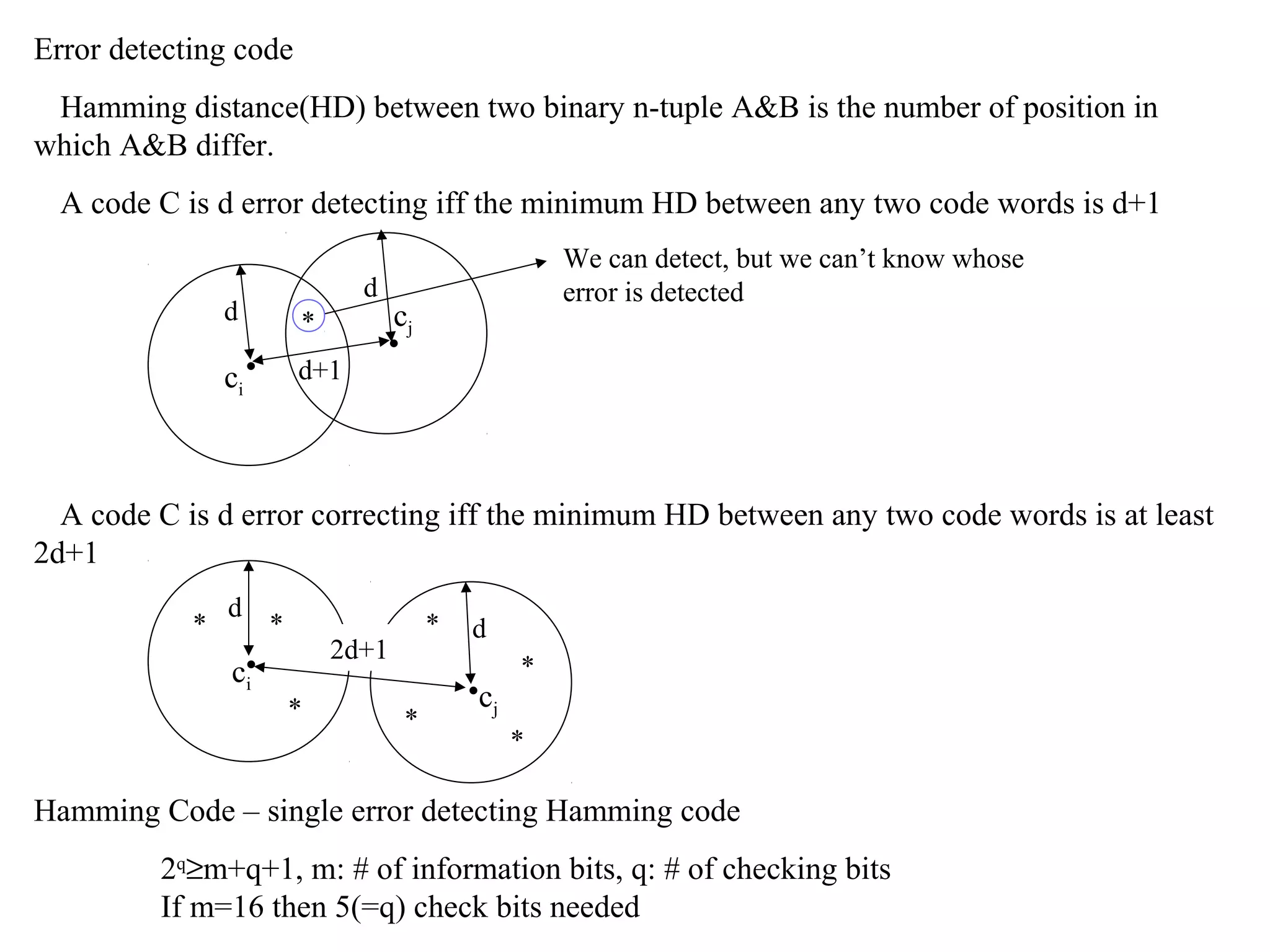

4) Fault tolerance techniques include avoidance, detection using redundancy, masking using voting, and dynamic reconfiguration to replace faulty components. Error detecting and correcting codes are also used.