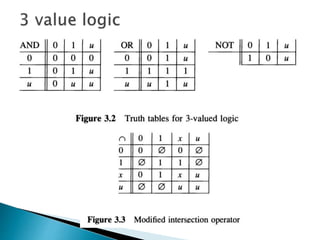

The document discusses design verification testing using logic simulation to assess system operations and verification quality. It contrasts compiled driven and event driven simulations, emphasizing aspects like timing considerations and initialization needs in sequential circuits. Additionally, it highlights the importance of fault simulation to improve test quality by determining undetected faults and covers topics such as fault coverage and various fault types in circuits.