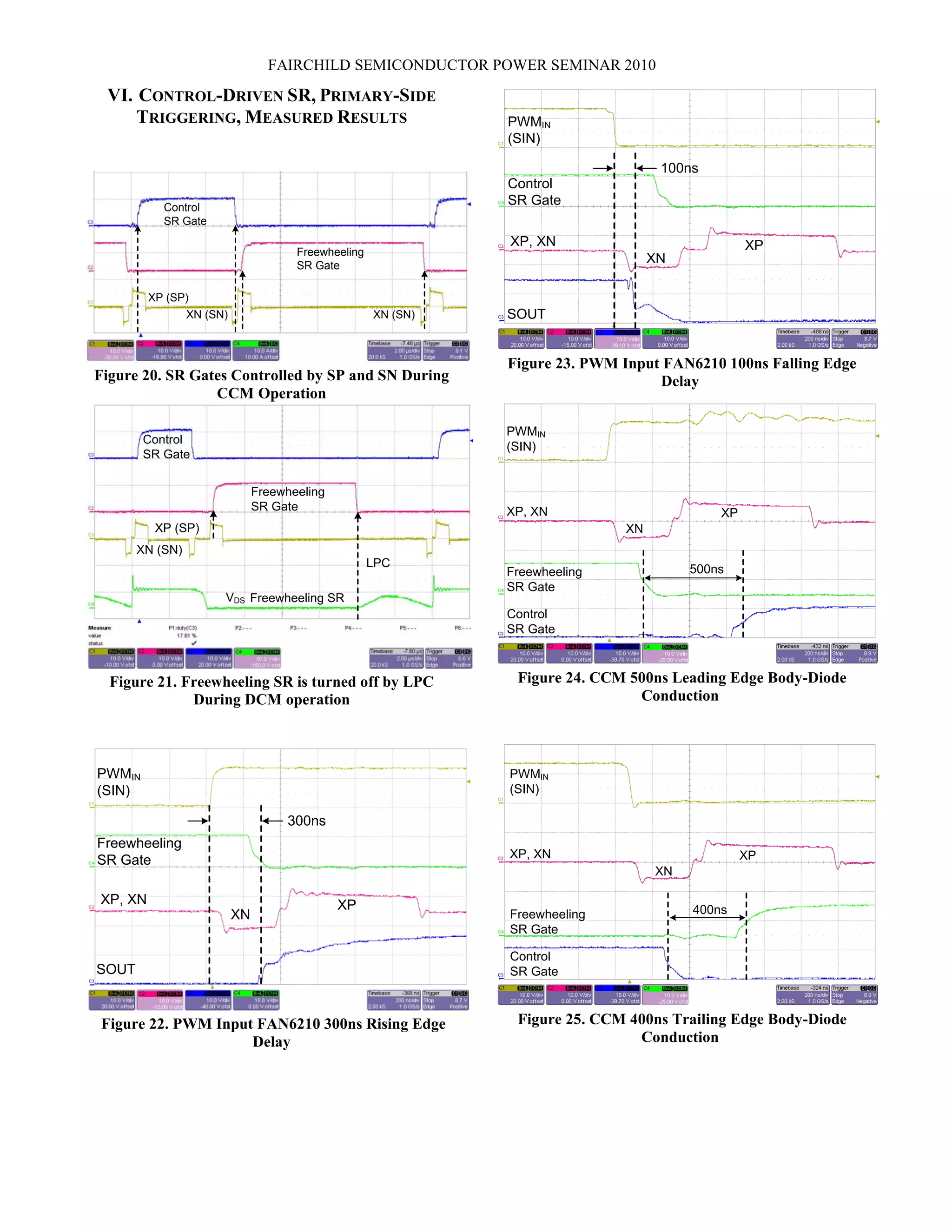

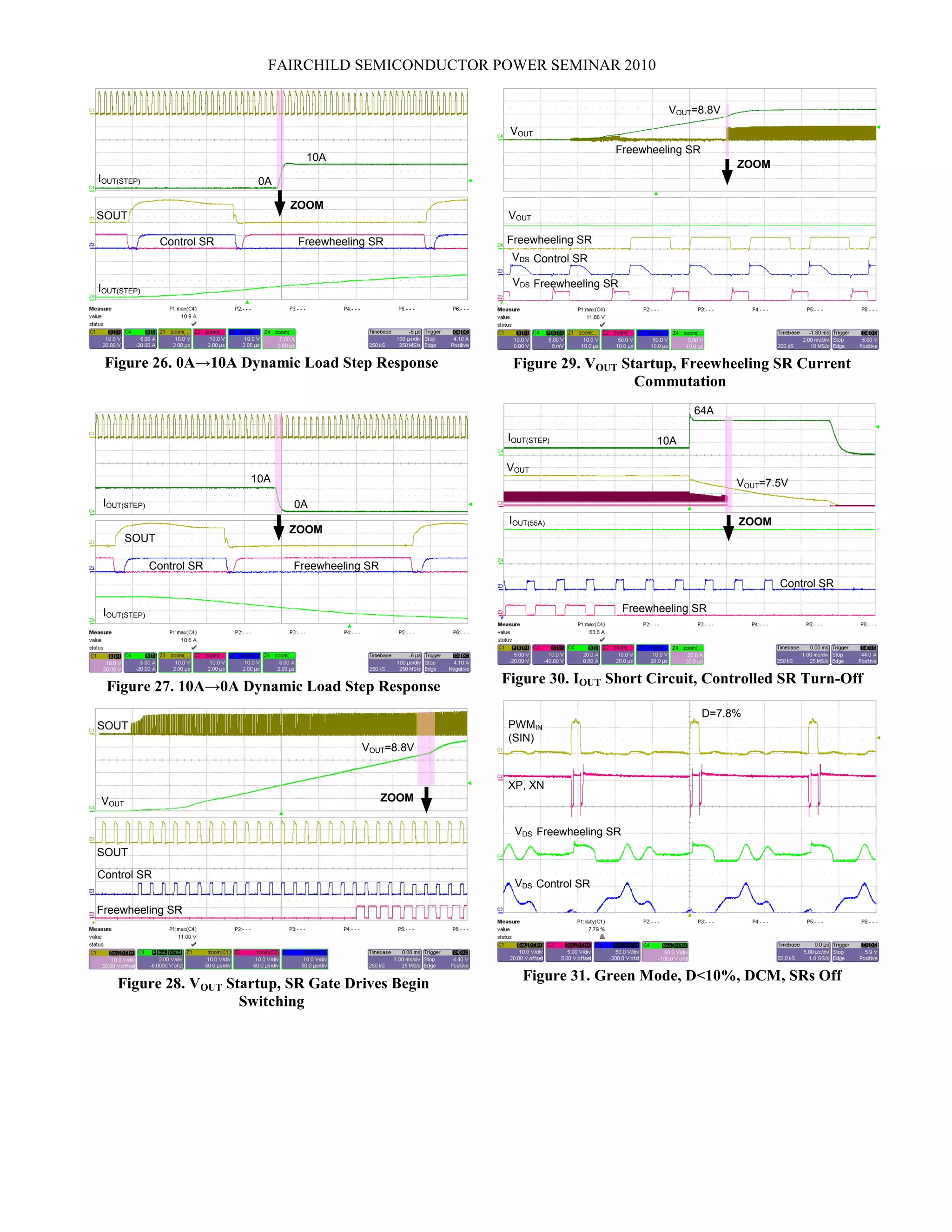

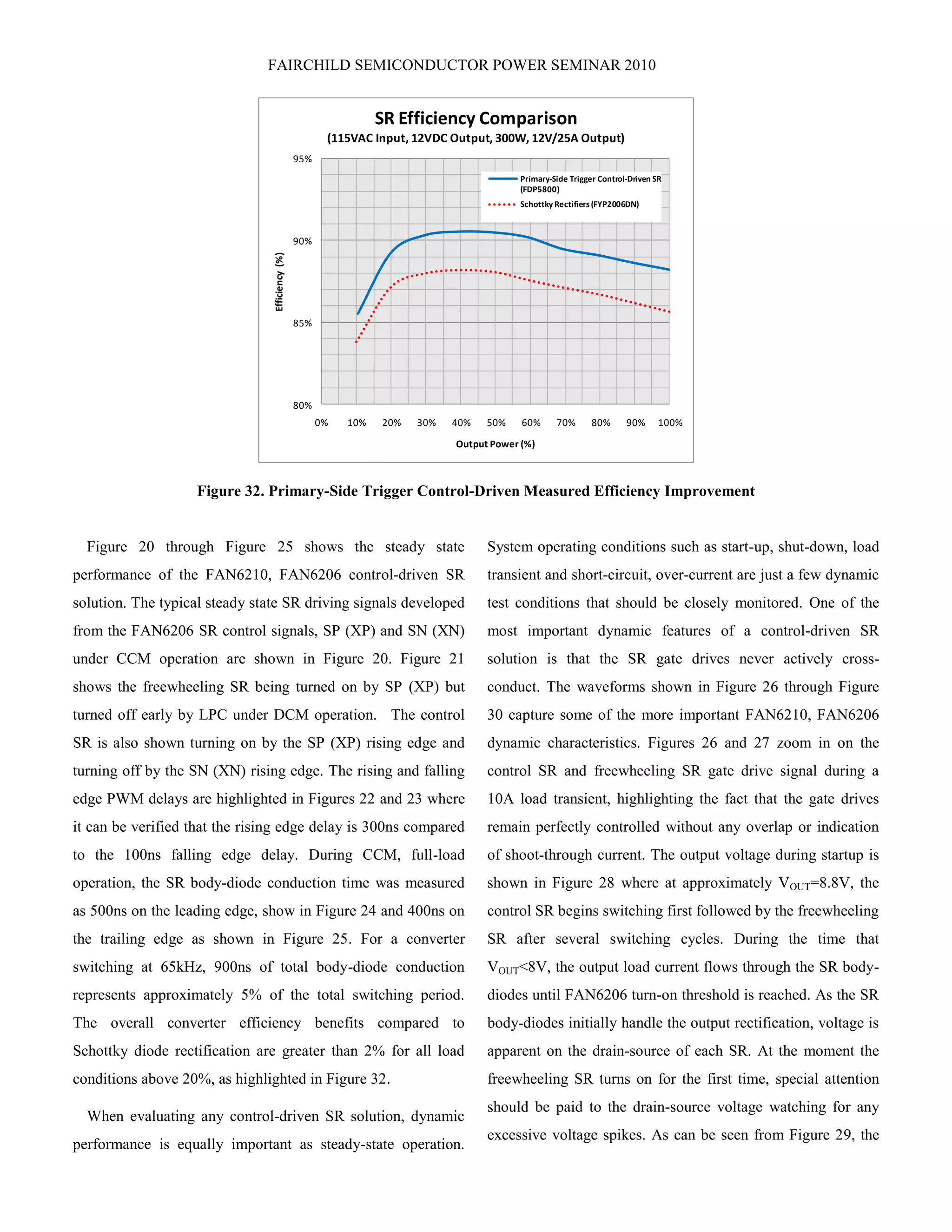

This document summarizes techniques for improving the efficiency of power converters by replacing diode rectifiers with synchronous rectifiers (SRs) using MOSFETs. SRs can reduce conduction losses by lowering the equivalent forward voltage drop compared to diodes. However, SRs introduce additional losses related to their body diode and switching operation that must be minimized through proper gate driving and timing. Integrating a Schottky diode with the SR MOSFET in a single package helps reduce body diode losses and reverse recovery effects. Optimizing the gate driving method and timing is critical for SR performance in forward converters.

![FAIRCHILD SEMICONDUCTOR POWER SEMINAR 2010

REFERENCES

[1] “FAN6210, Primary-Side Synchronous Rectifier (SR) Trigger

Controller for Dual Forward Converter”, Datasheet, Fairchild

Semiconductor, March 2010

[2] “FAN6206 Highly Integrated Dual-Channel Synchronous Rectification

Controller for Dual-Forward Converter”, Datasheet, Fairchild

Semiconductor, April 2010

[3] “Primary-Side Synchronous Rectifier (SR) Trigger Solution for Dual-

Forward Converter”, AN-6206, Fairchild Semiconductor, April 2010

Steve Mappus is a Principal Systems Engineer

working in Fairchild Semiconductor’s Power

Conversion group located in Bedford, NH, USA. In his

current role, he is responsible for new product

development of power supply control and MOSFET gate drive ICs. He has

more than 20 years of power supply design experience including 10 years

designing military and commercial power systems for avionic applications.

More recently, he has spent the last 10 years working in the power

management semiconductor business specializing in Systems and

Applications Engineering. His areas of interest include high-power converter

topologies, soft-switching converters, synchronous rectification, high-

frequency power conversion, and power factor correction.](https://image.slidesharecdn.com/0060a69b-4327-4cf4-95be-ef238e912311-150818015228-lva1-app6891/75/Synchronous-Rectification-for-Forward-Converters_SMappus_June-4-2010-18-2048.jpg)