This document outlines the key concepts covered in the first lecture of an introduction to CMOS VLSI design course, including:

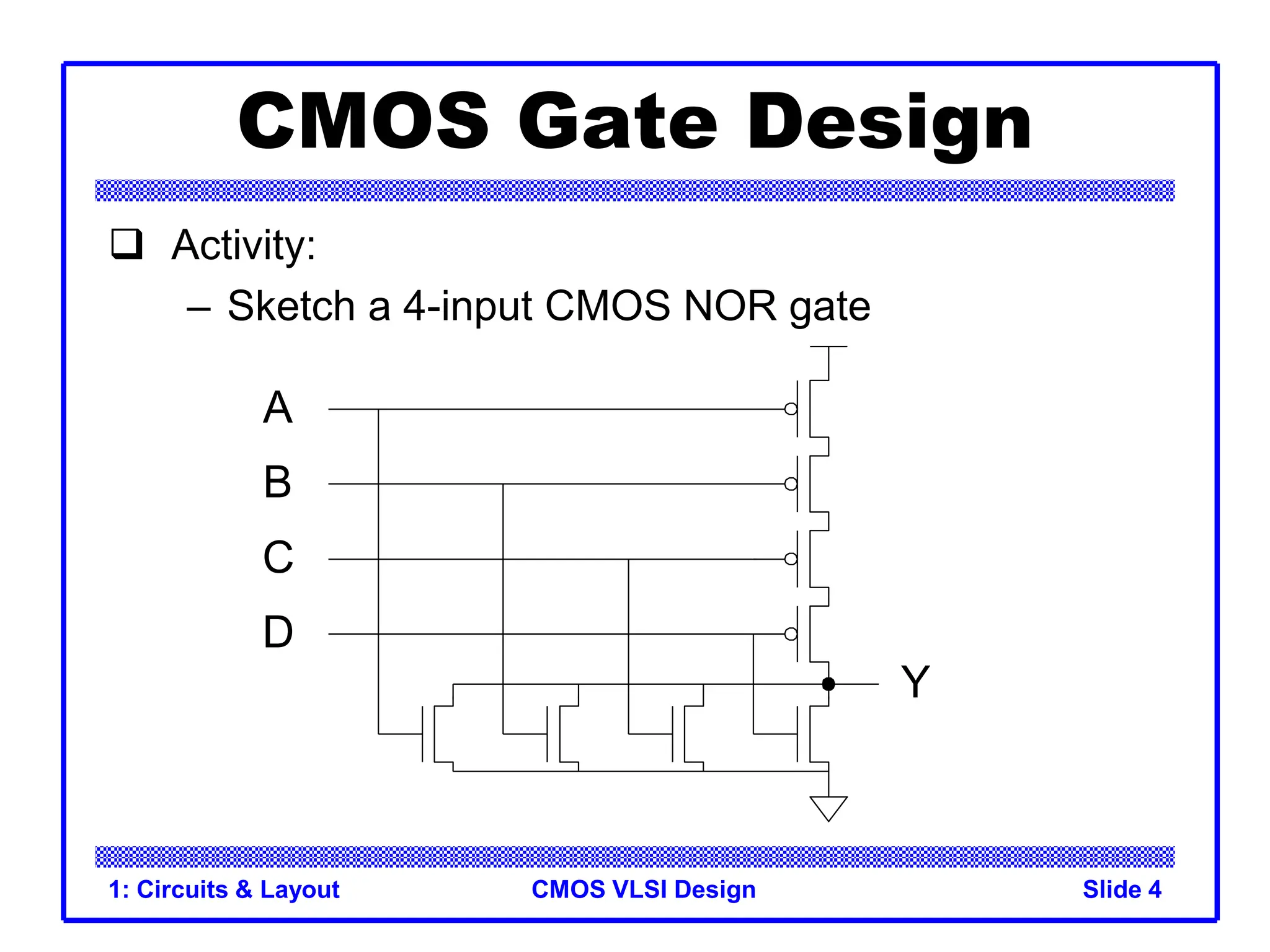

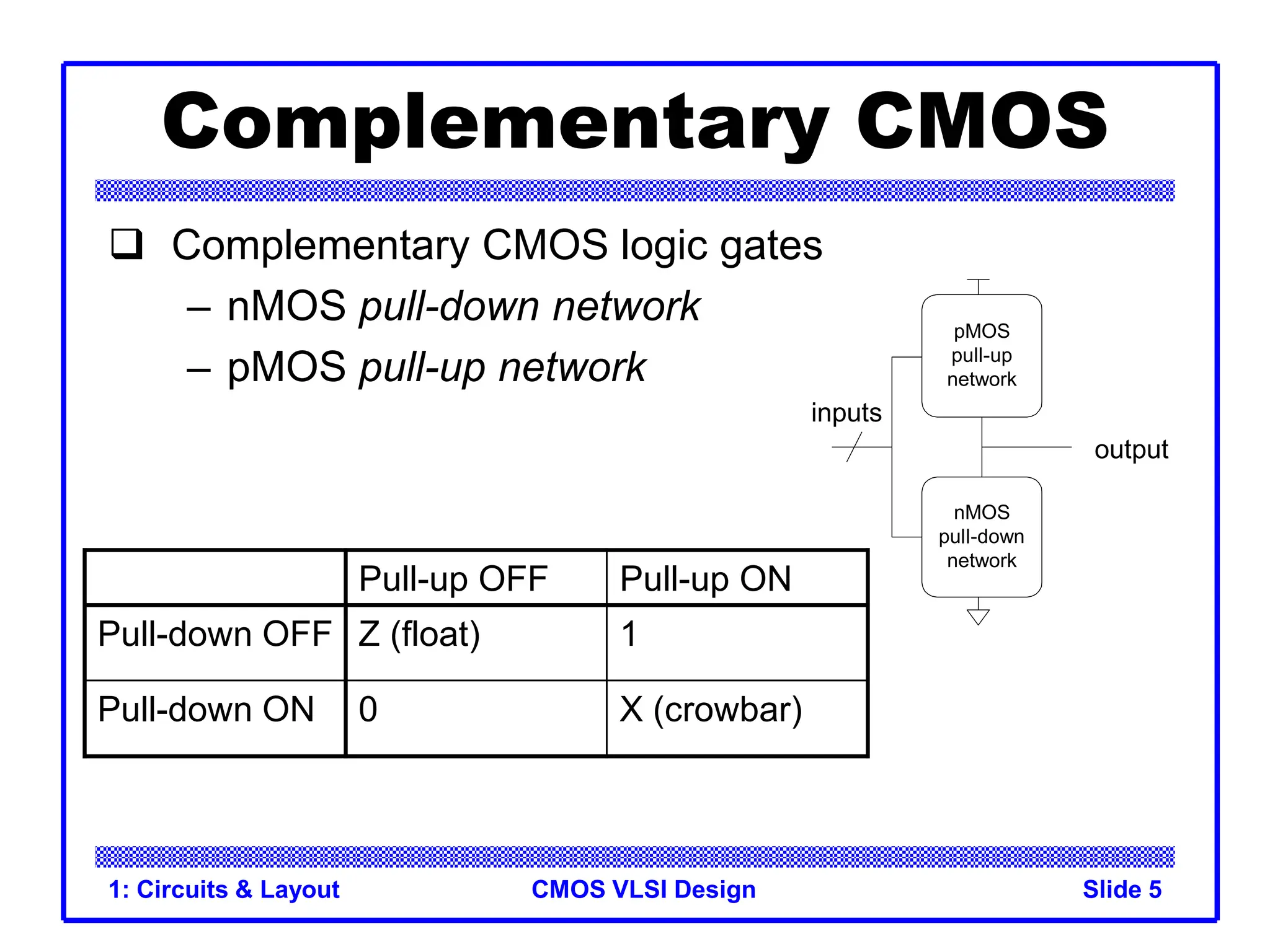

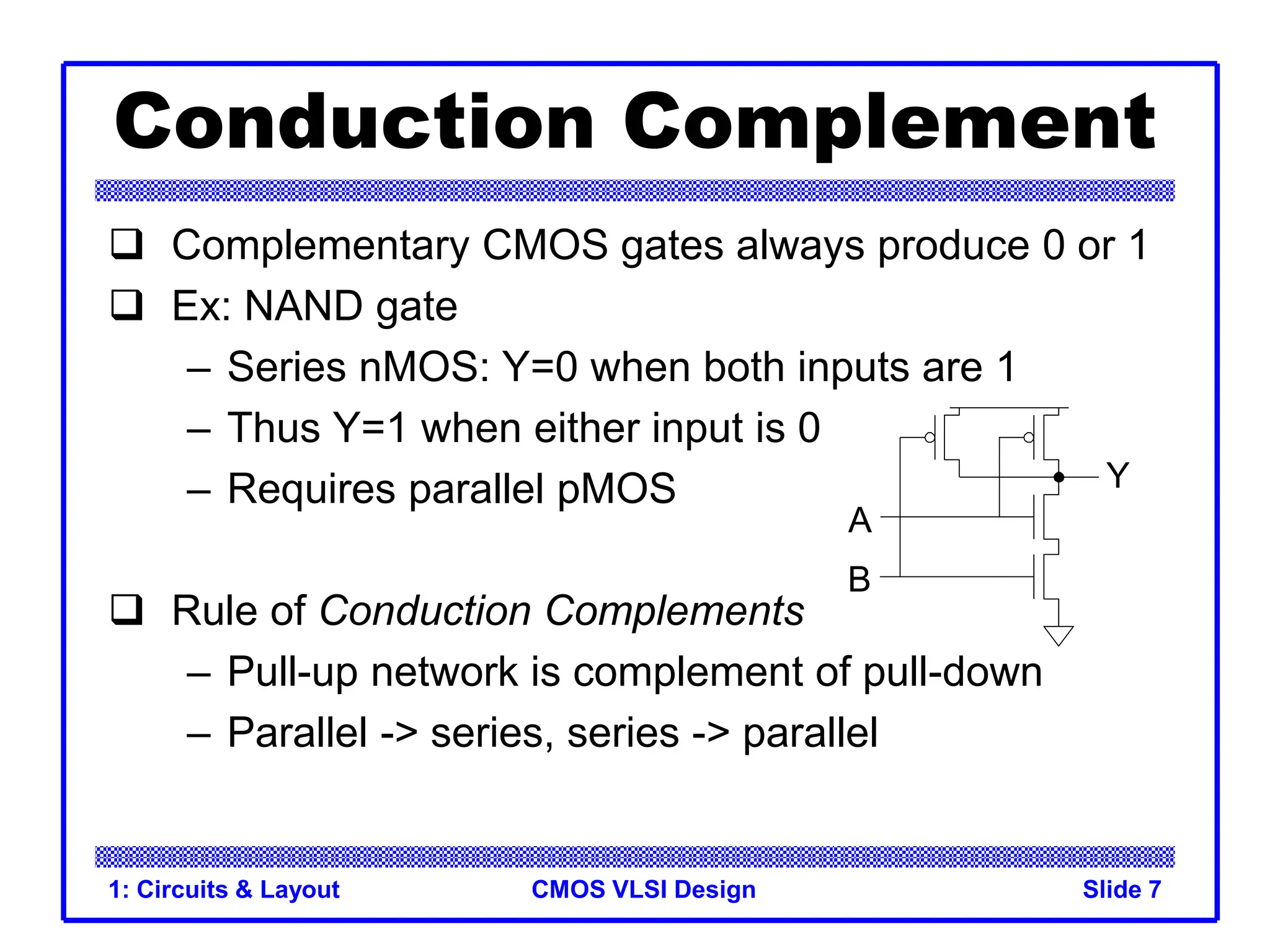

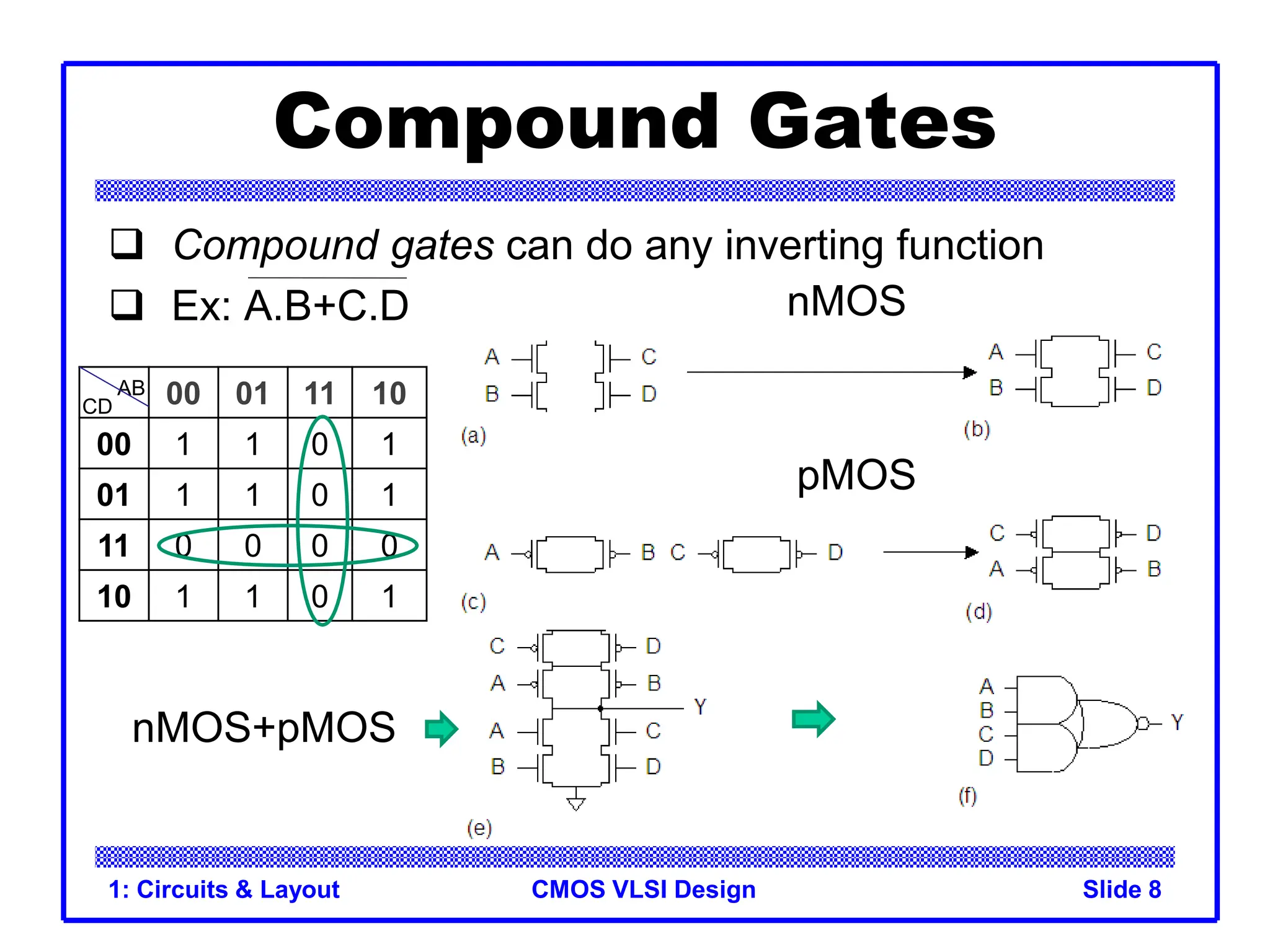

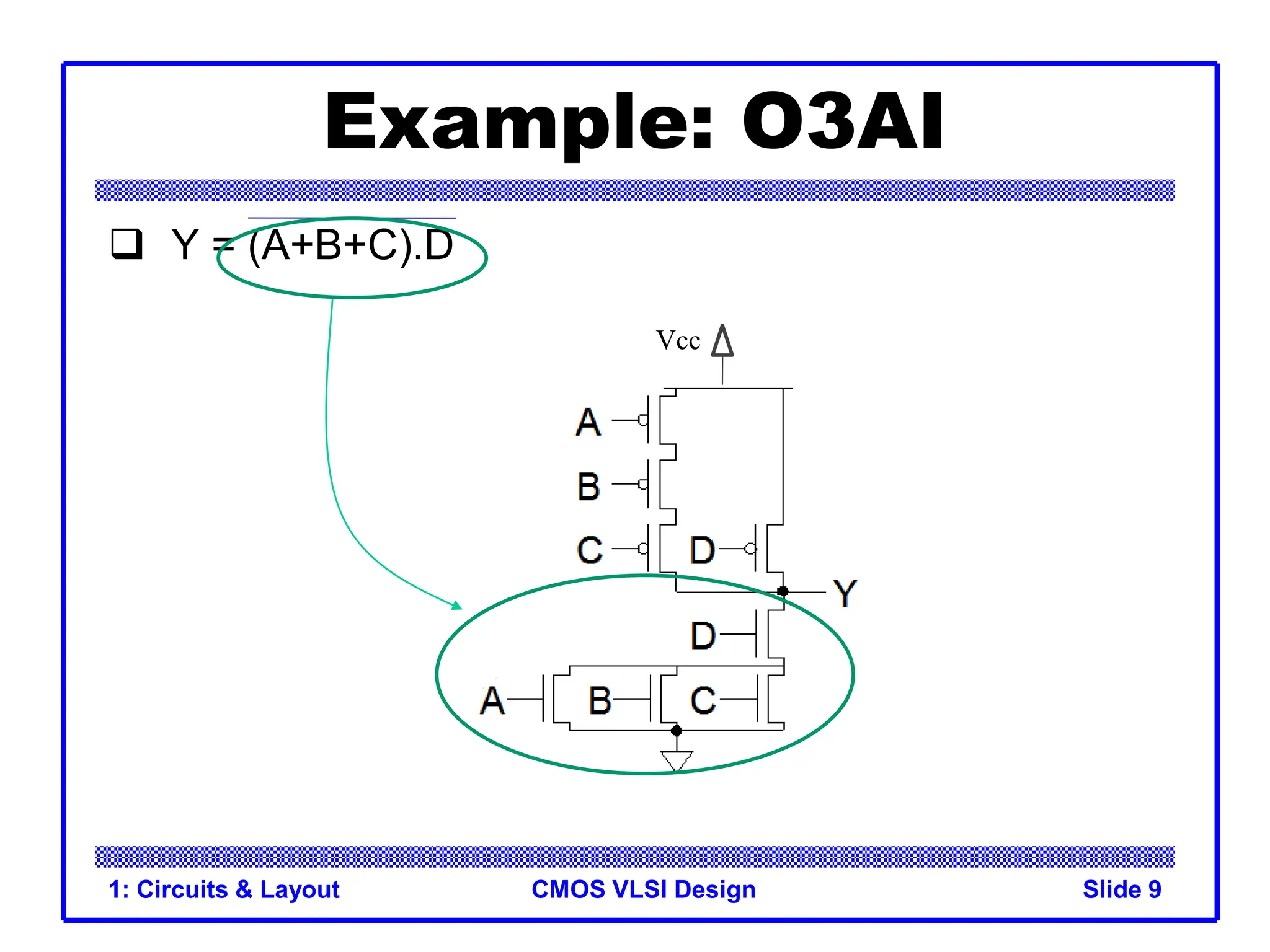

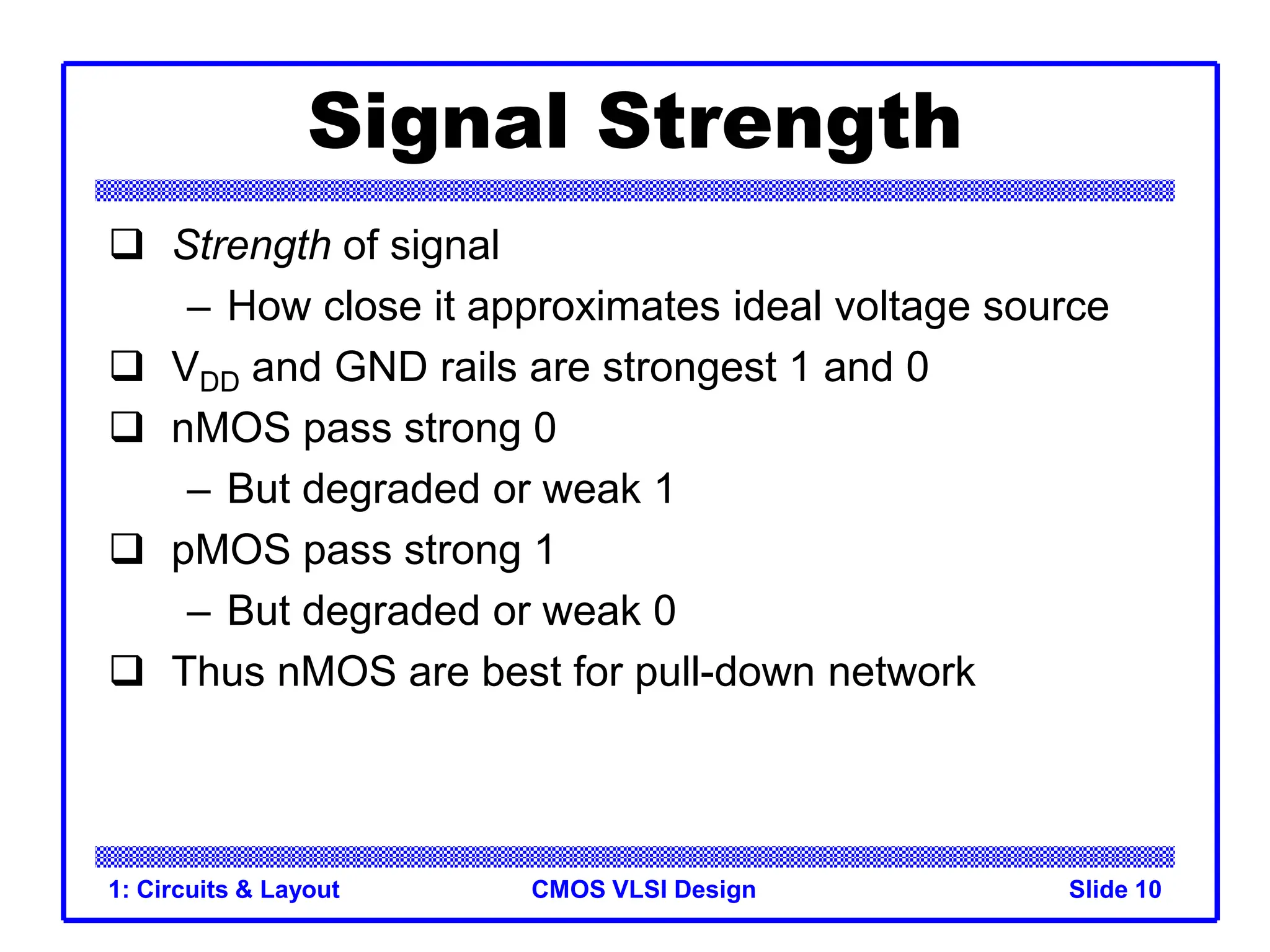

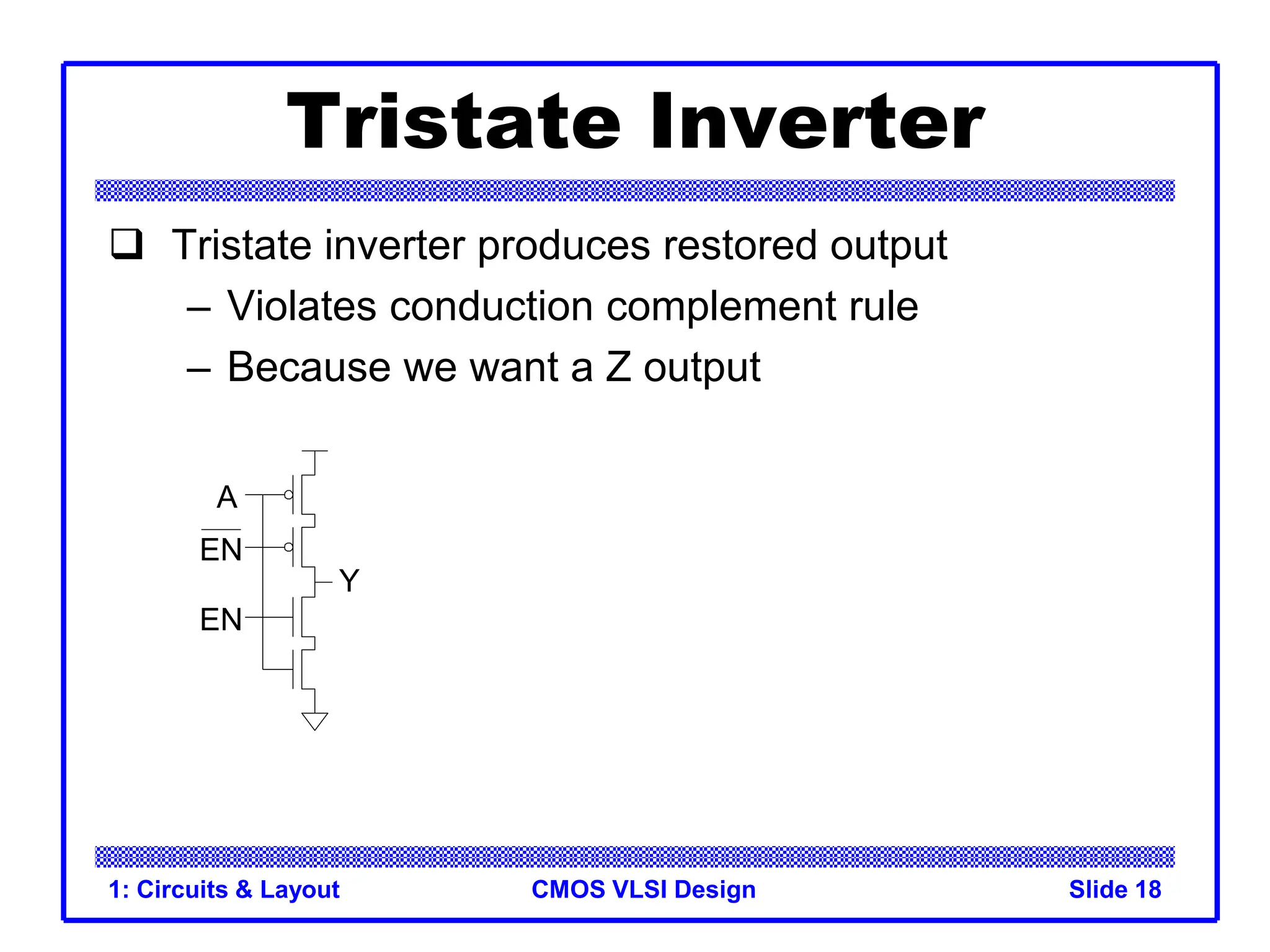

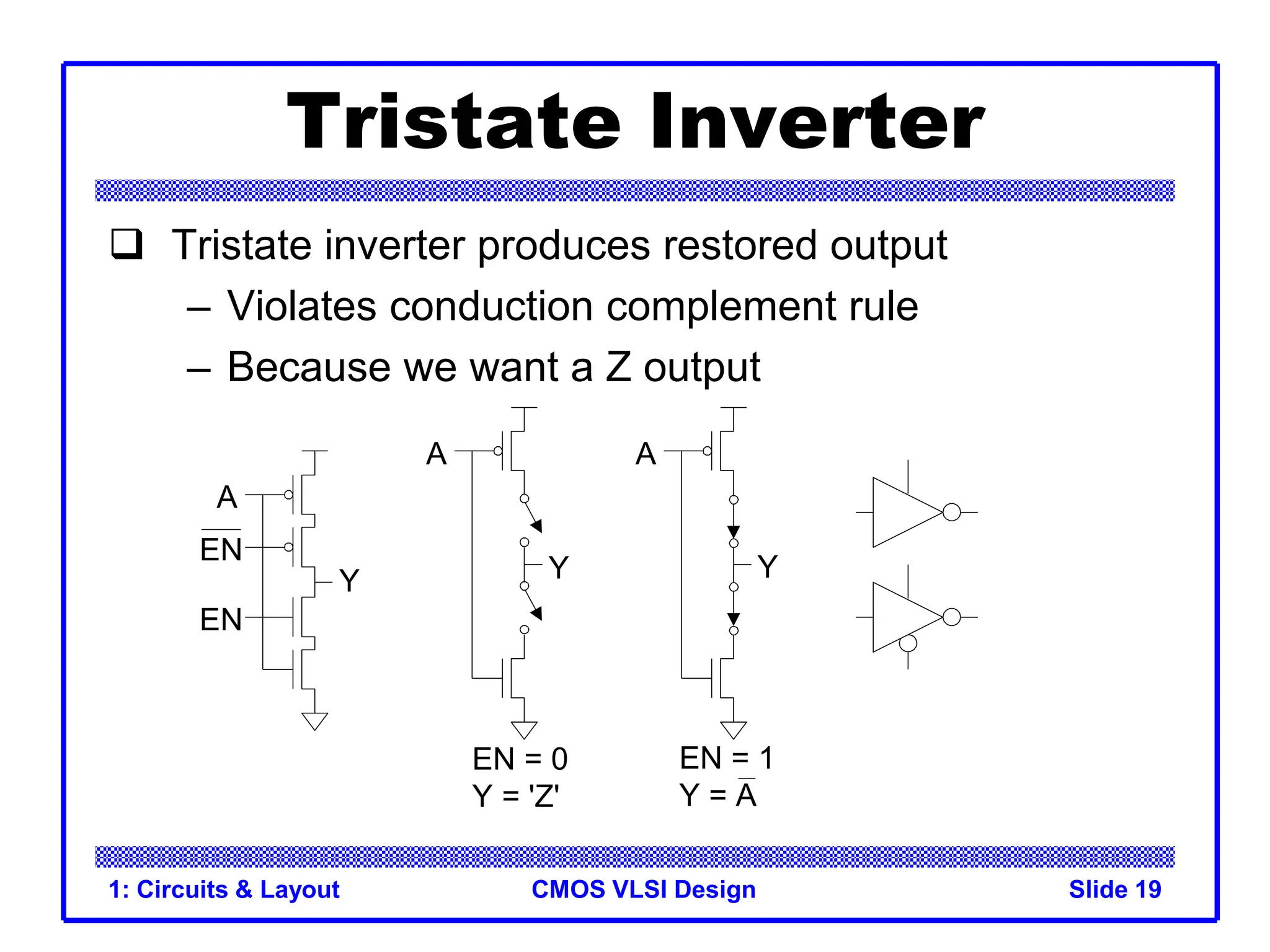

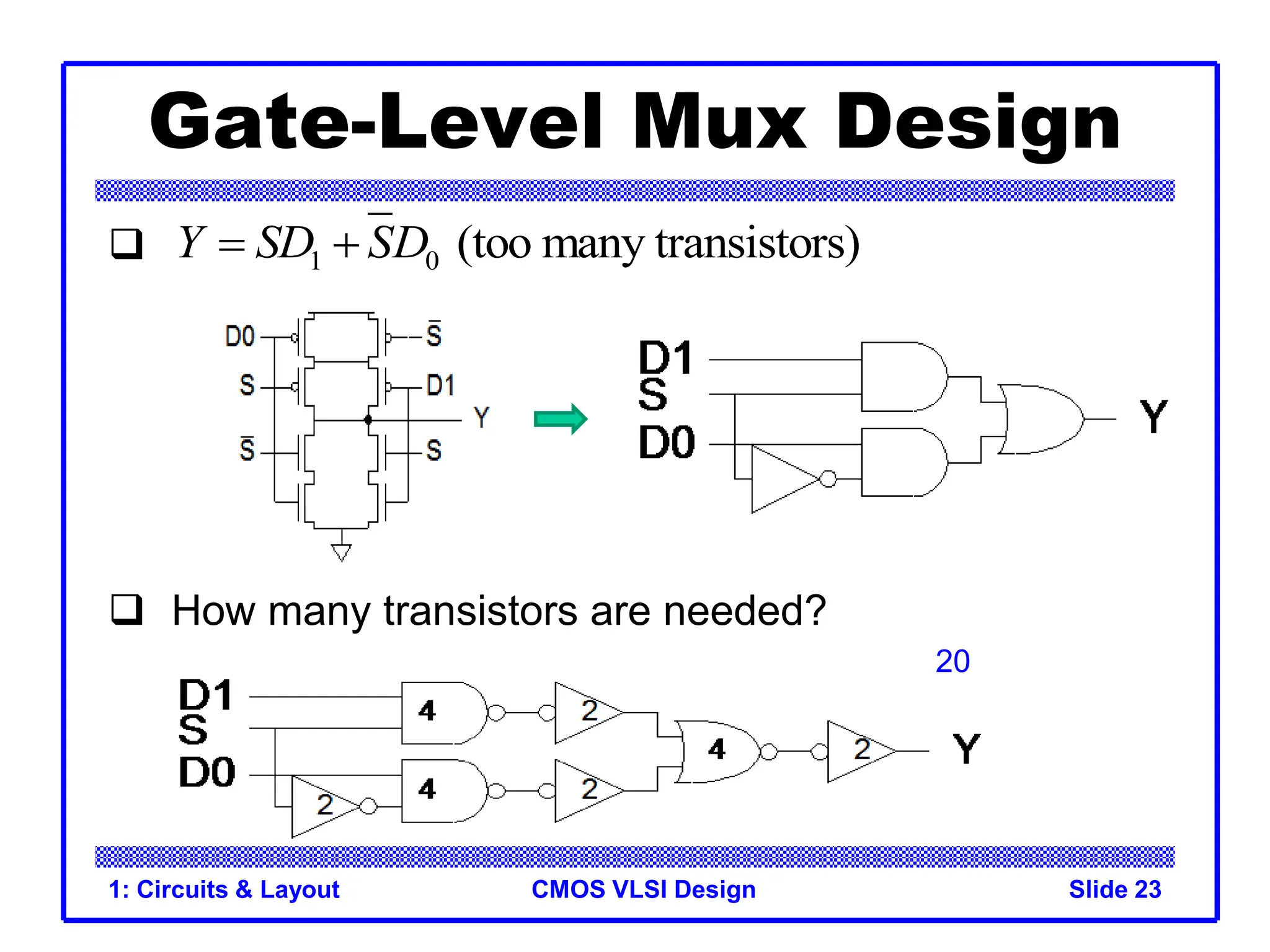

1) The design of basic CMOS logic gates using nMOS pull-down and pMOS pull-up networks along with the concept of conduction complements.

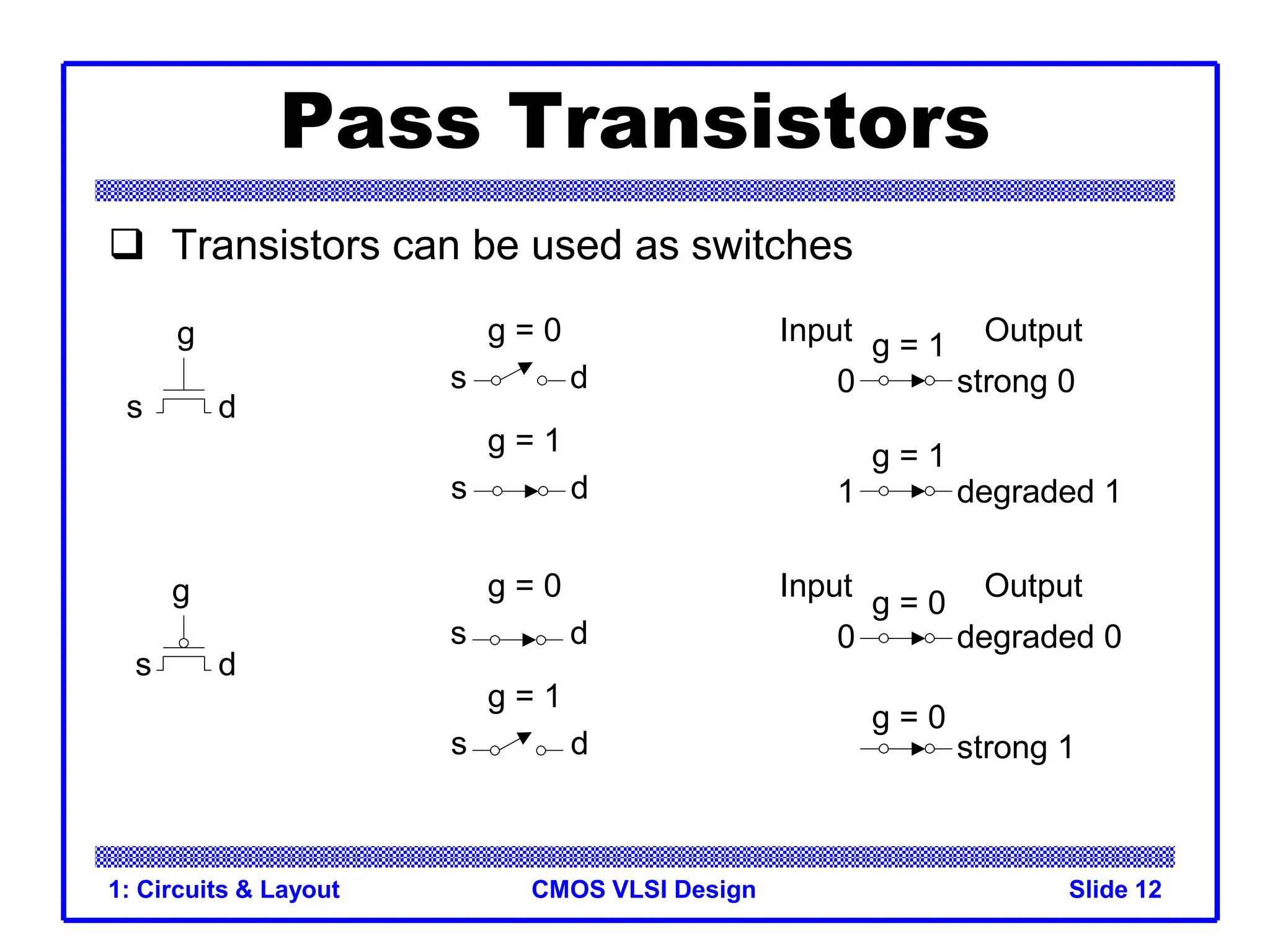

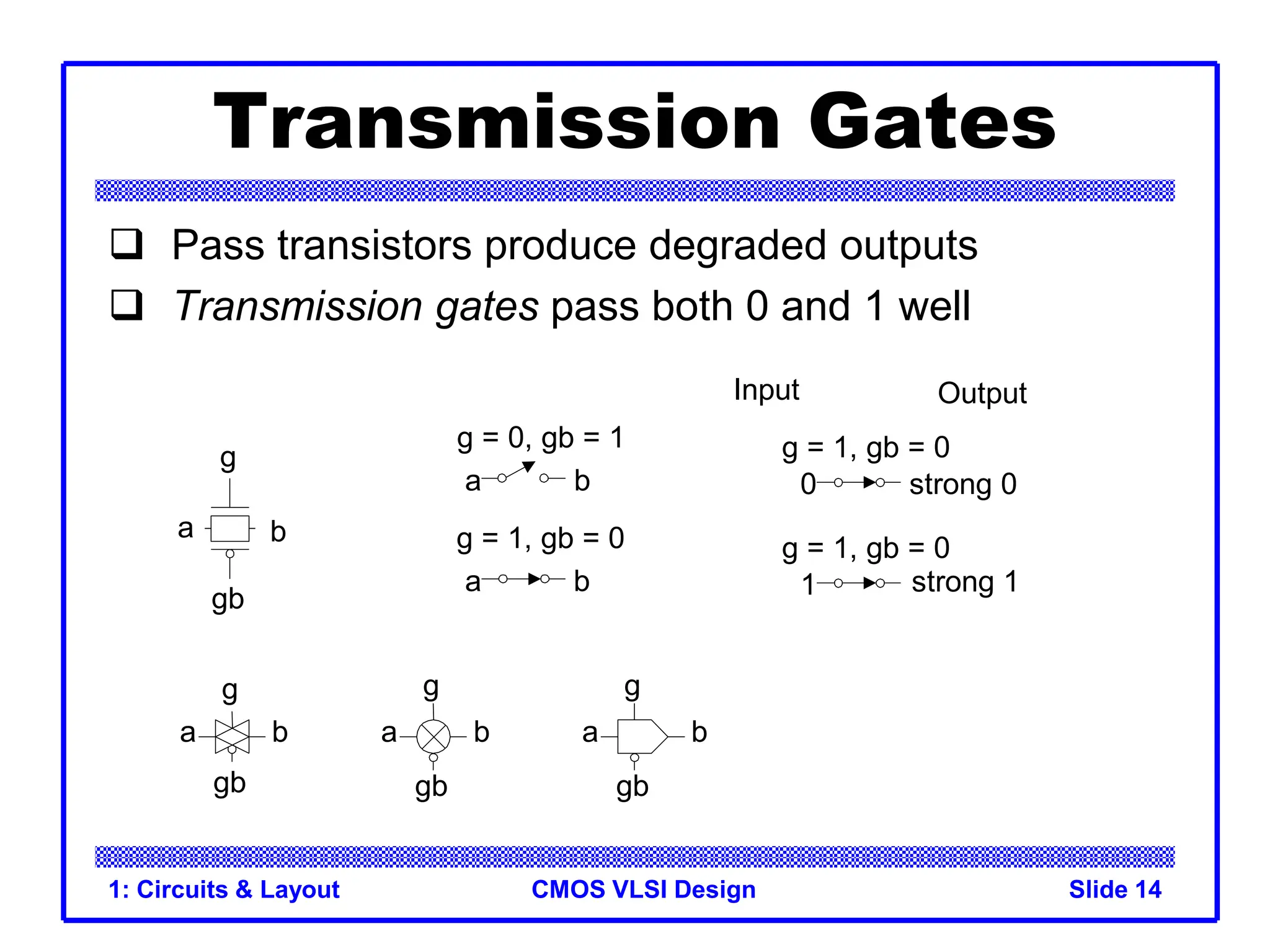

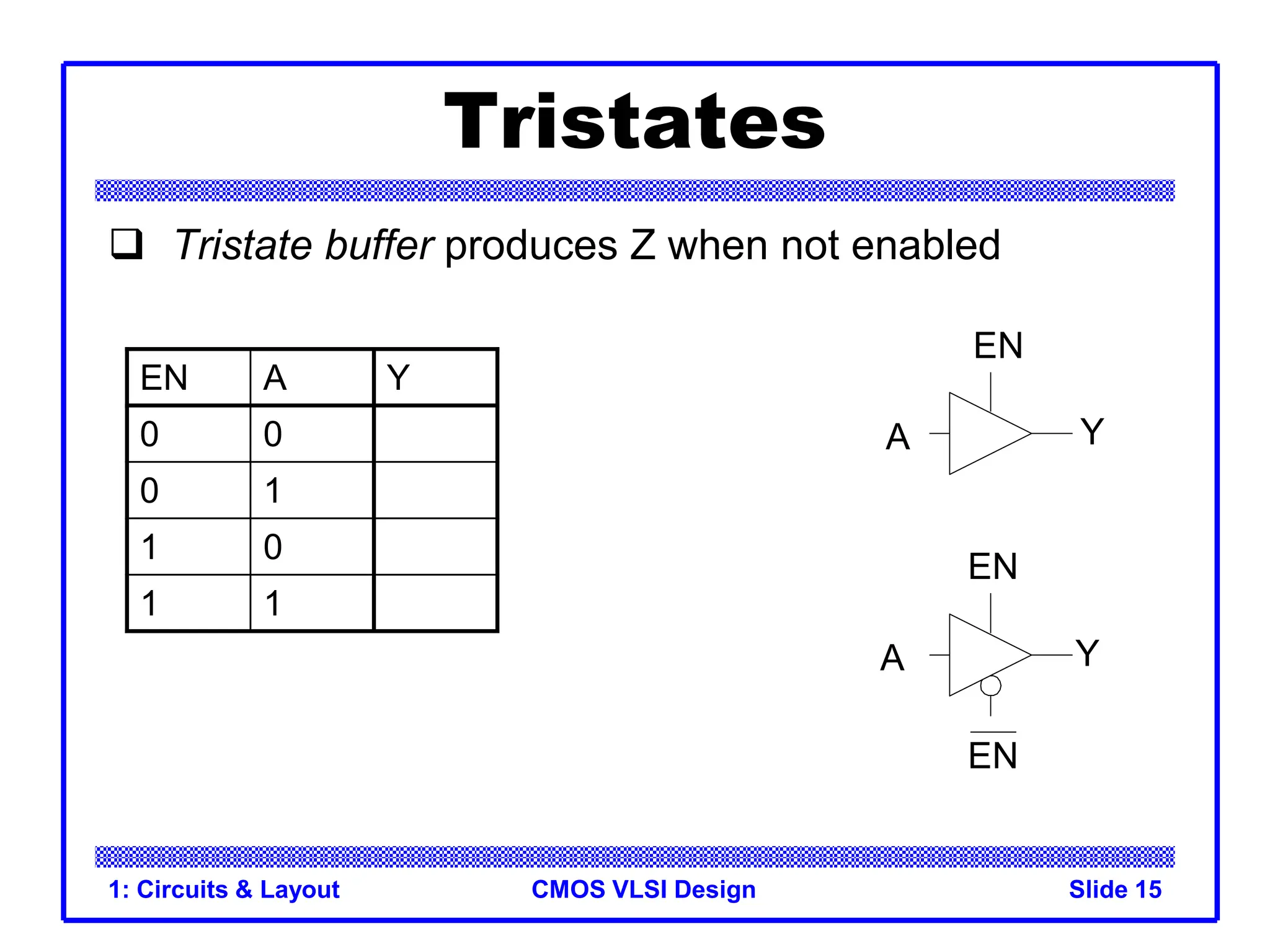

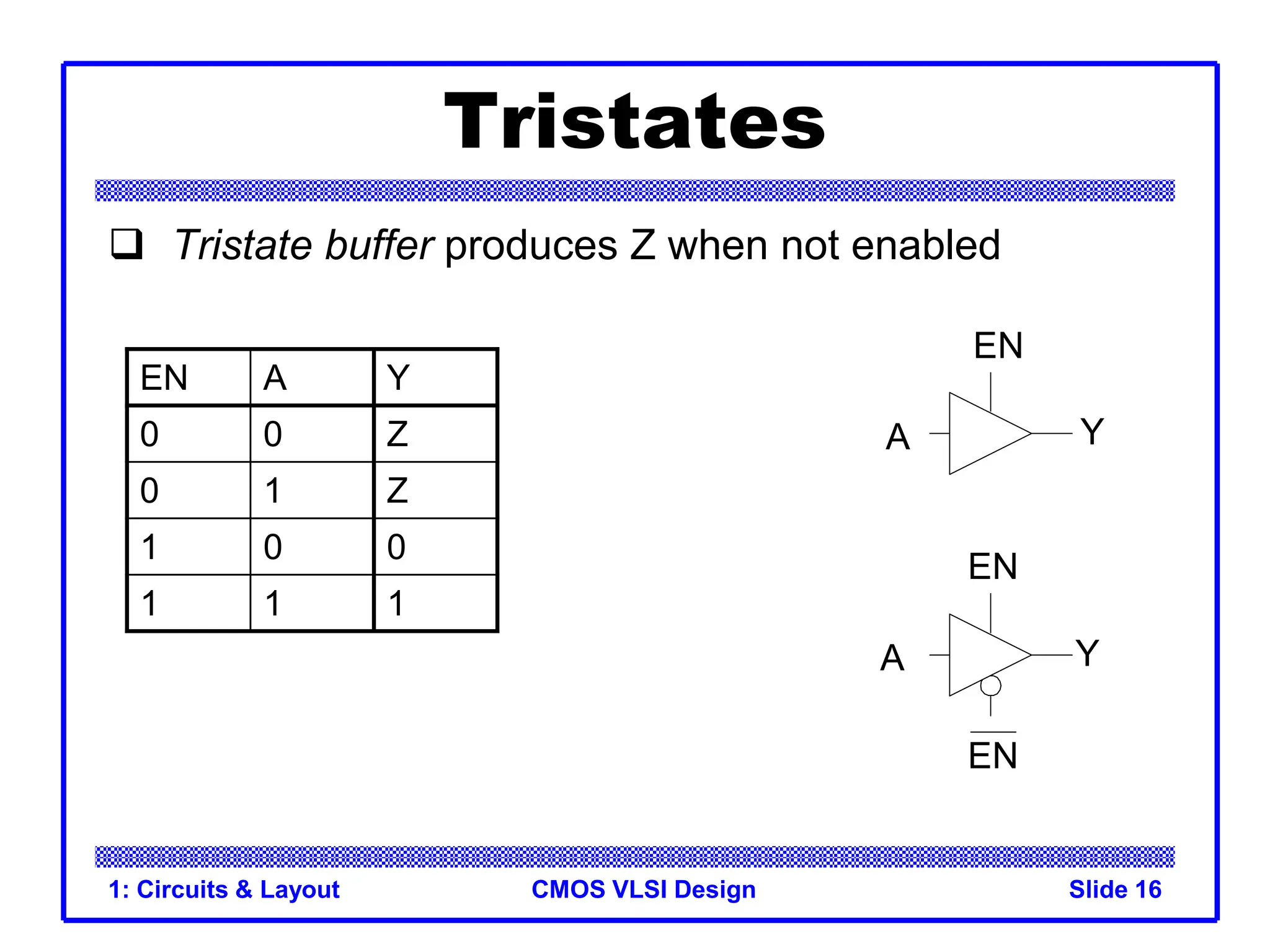

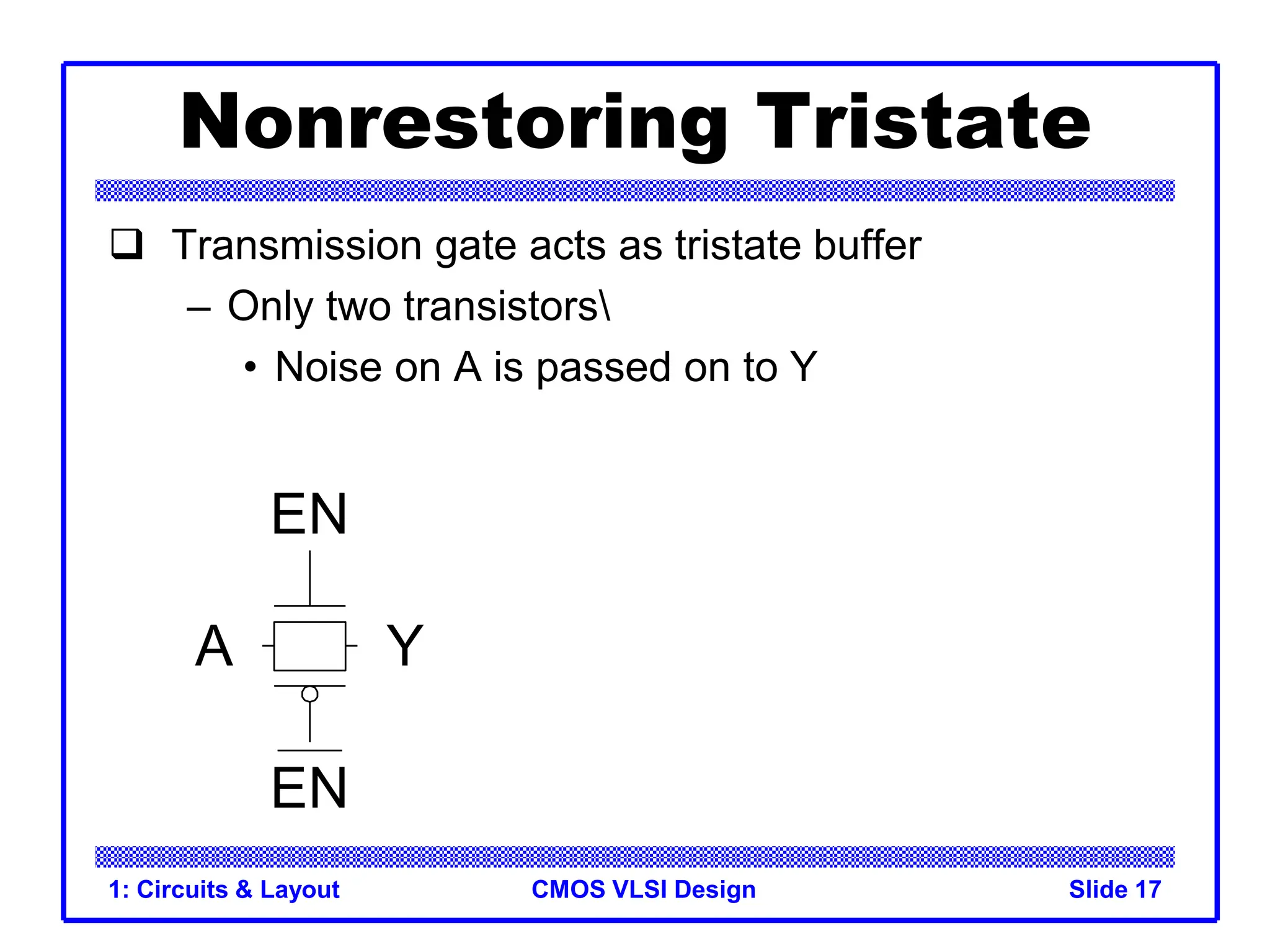

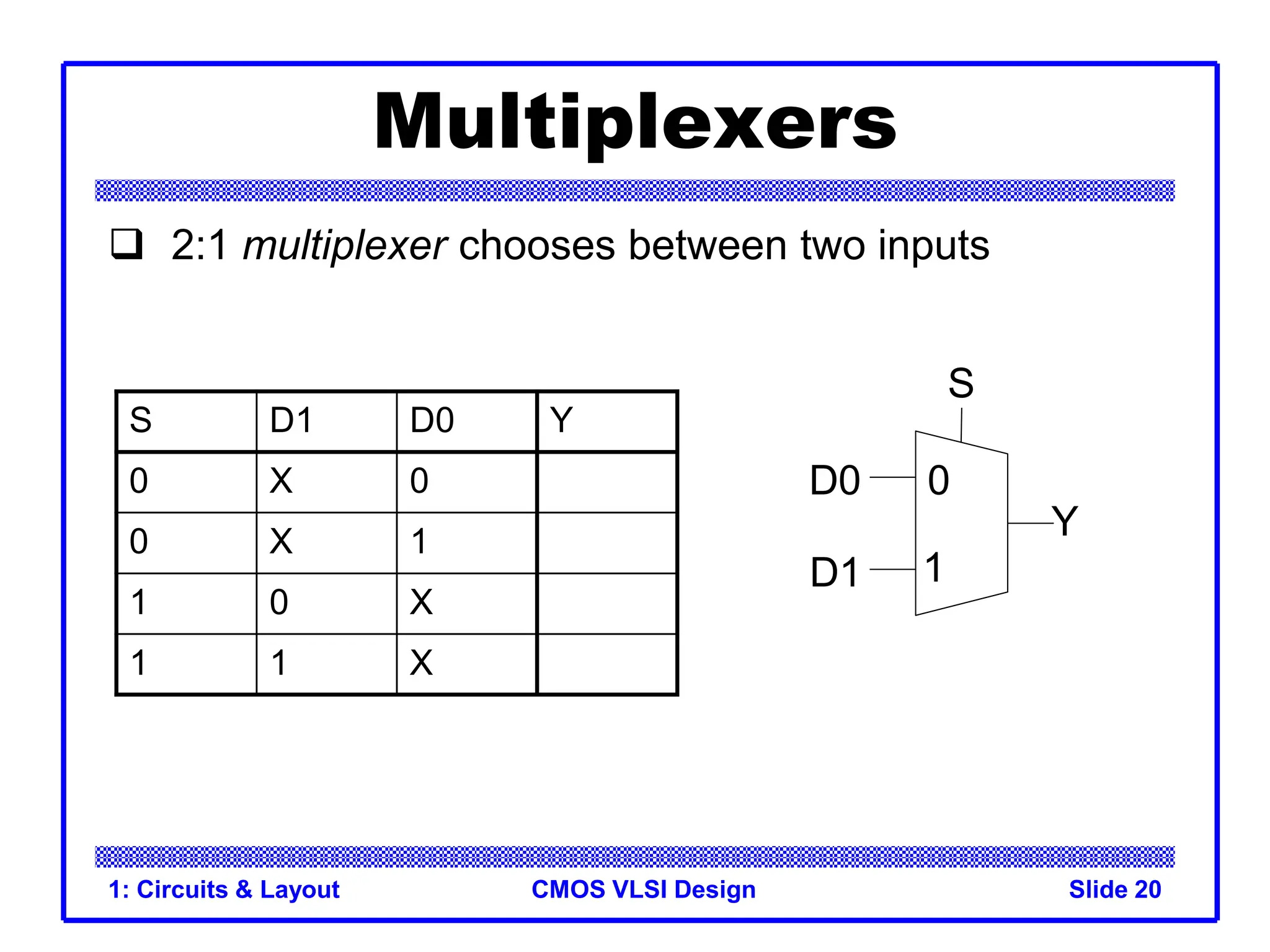

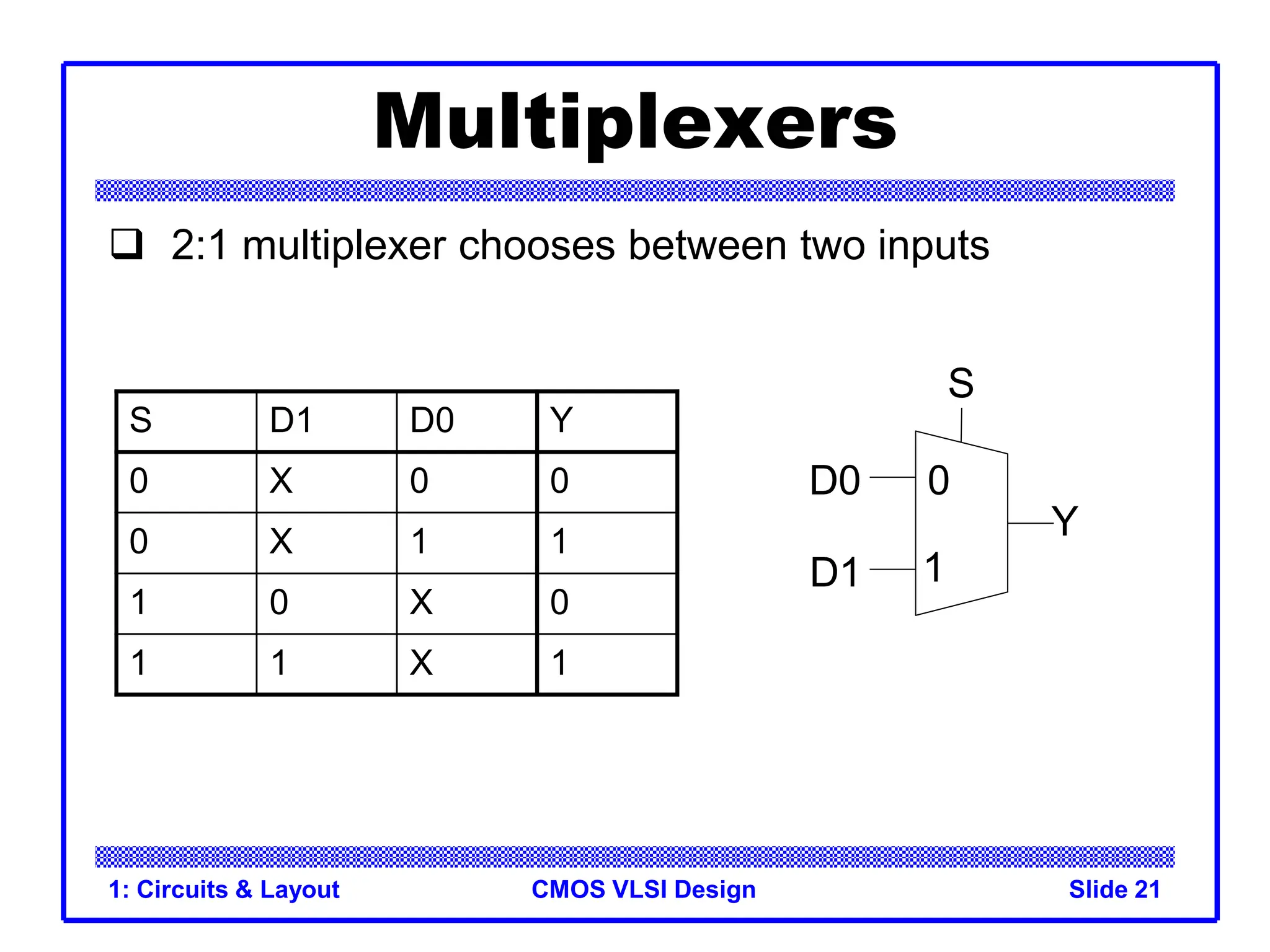

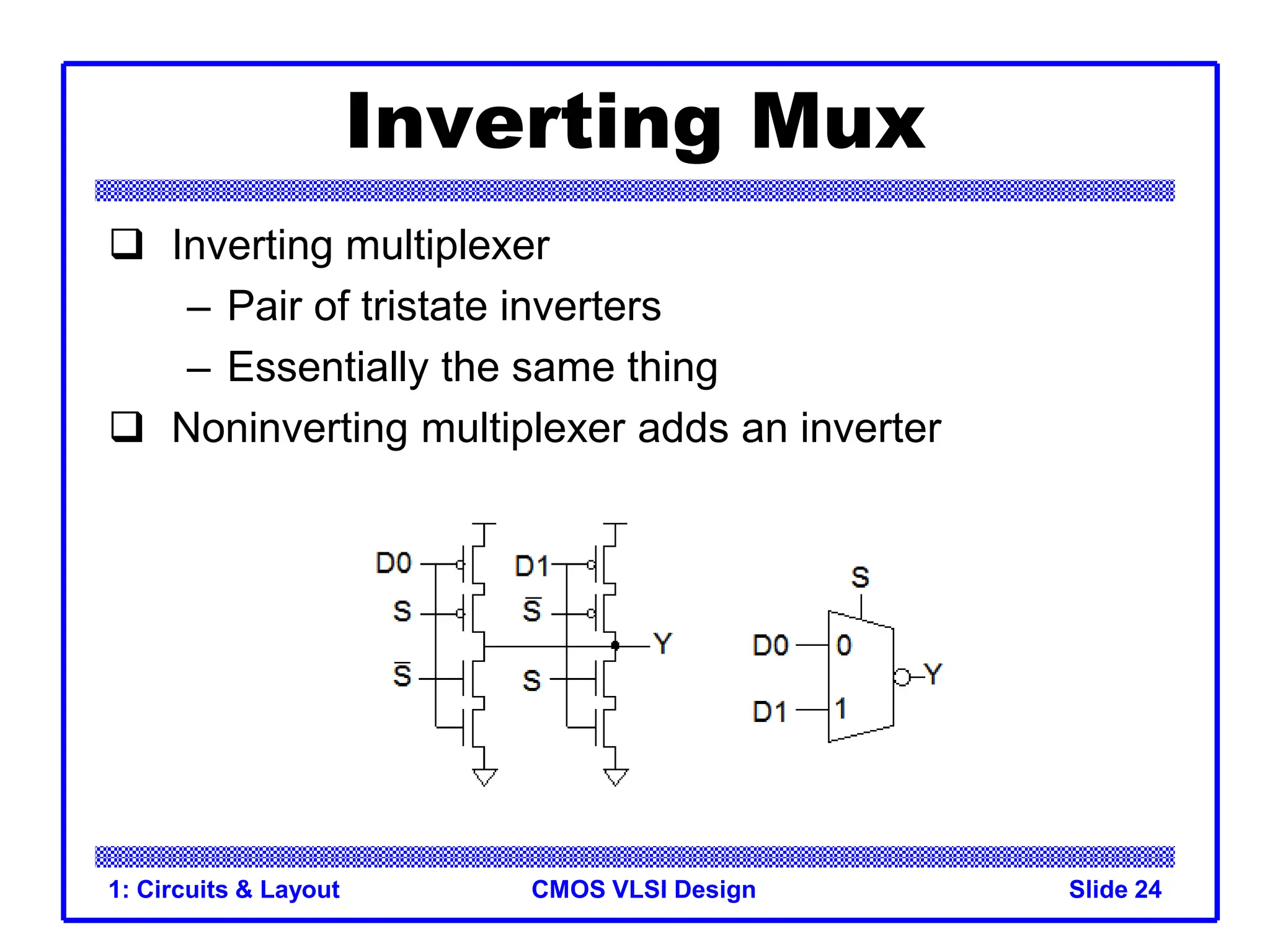

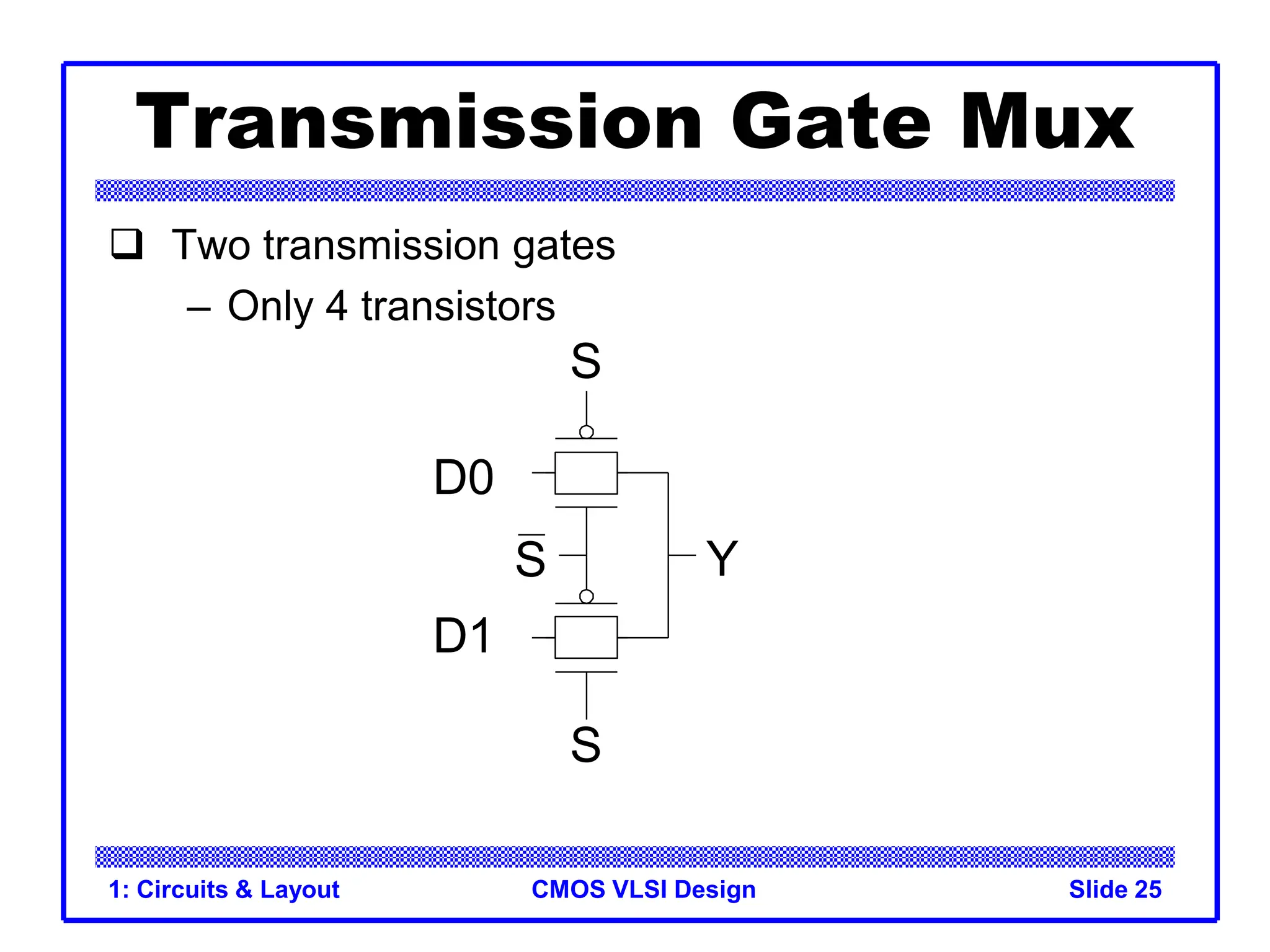

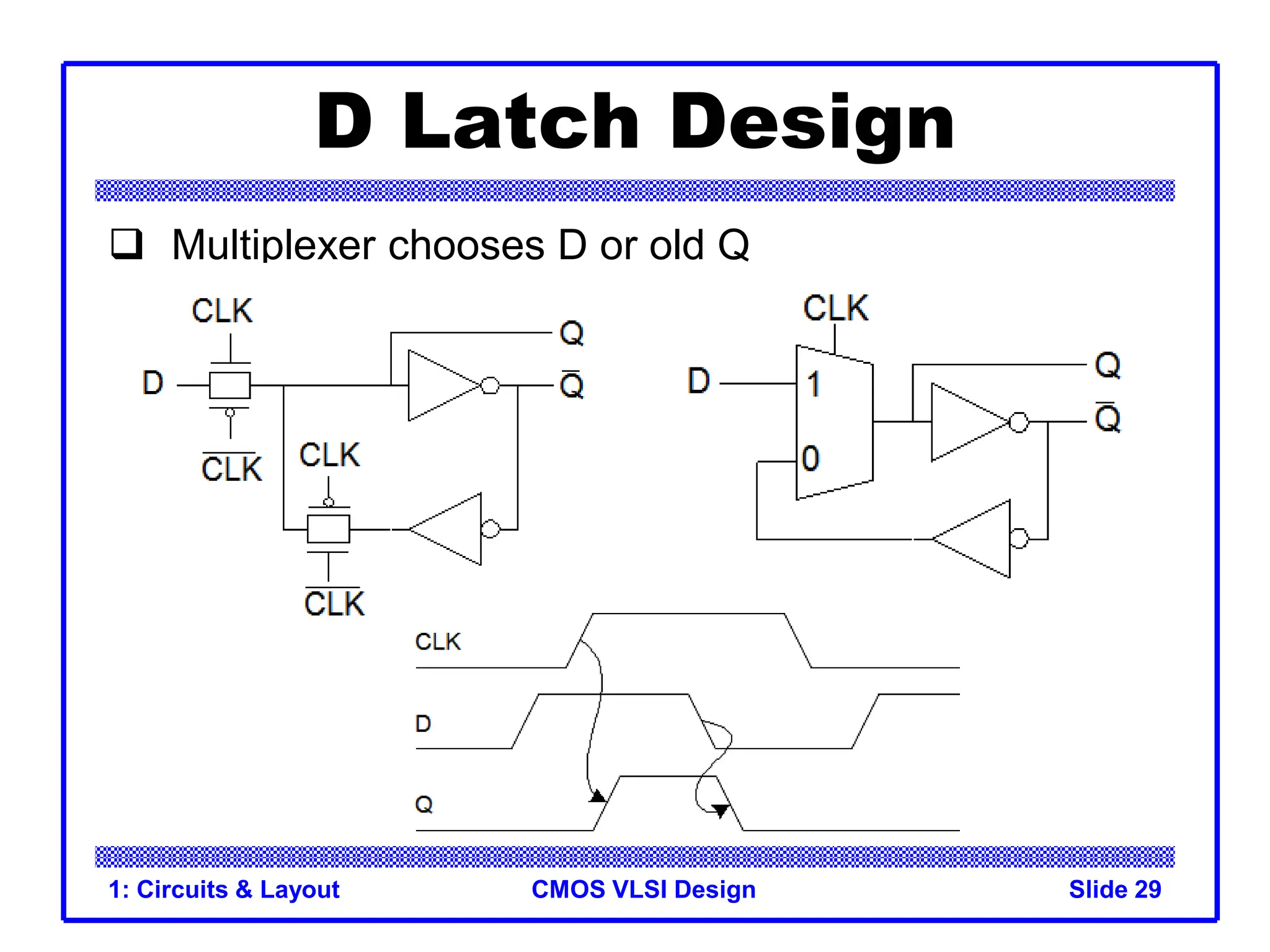

2) The use of pass transistors and transmission gates to implement multiplexers and tristate buffers.

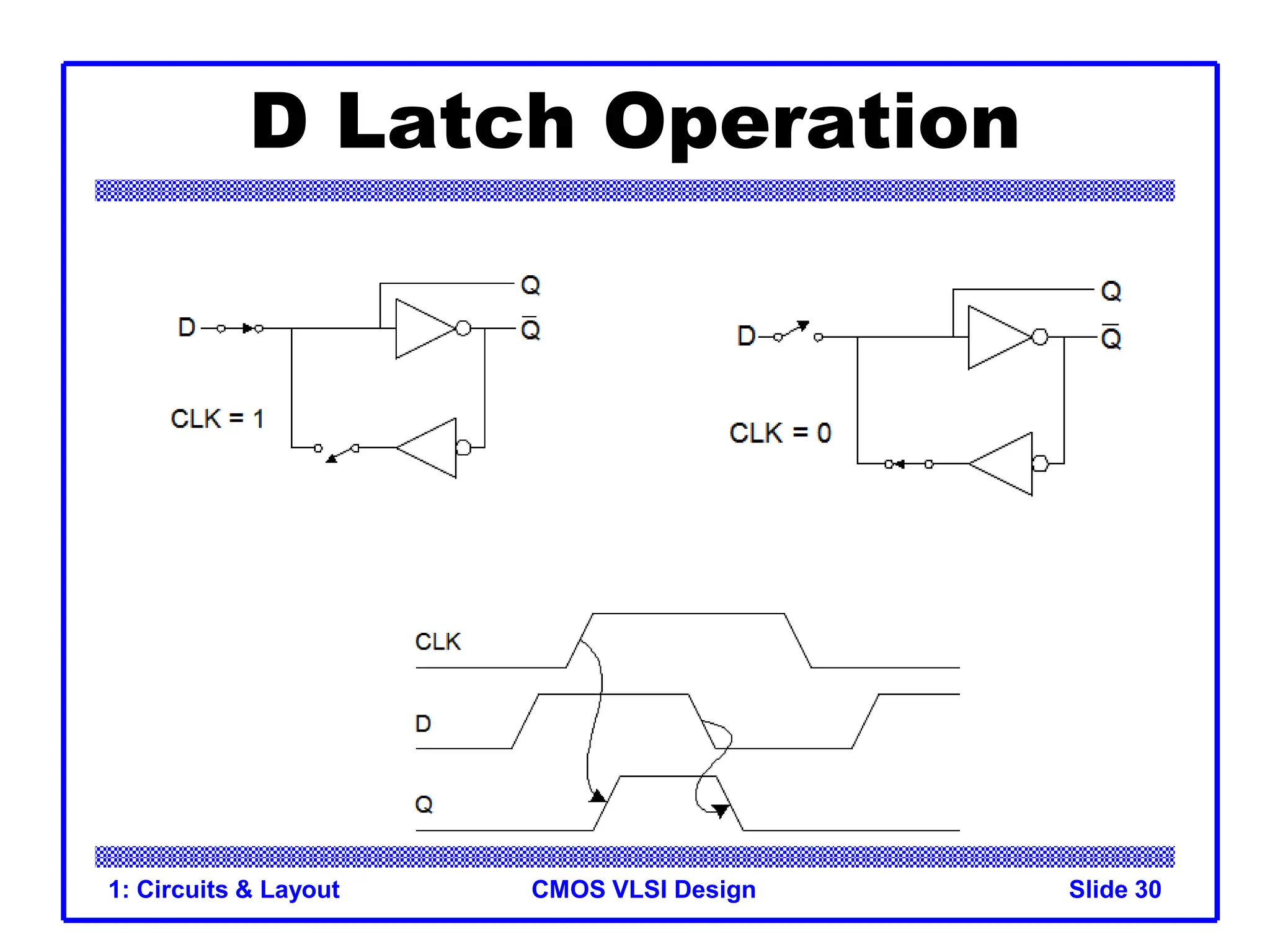

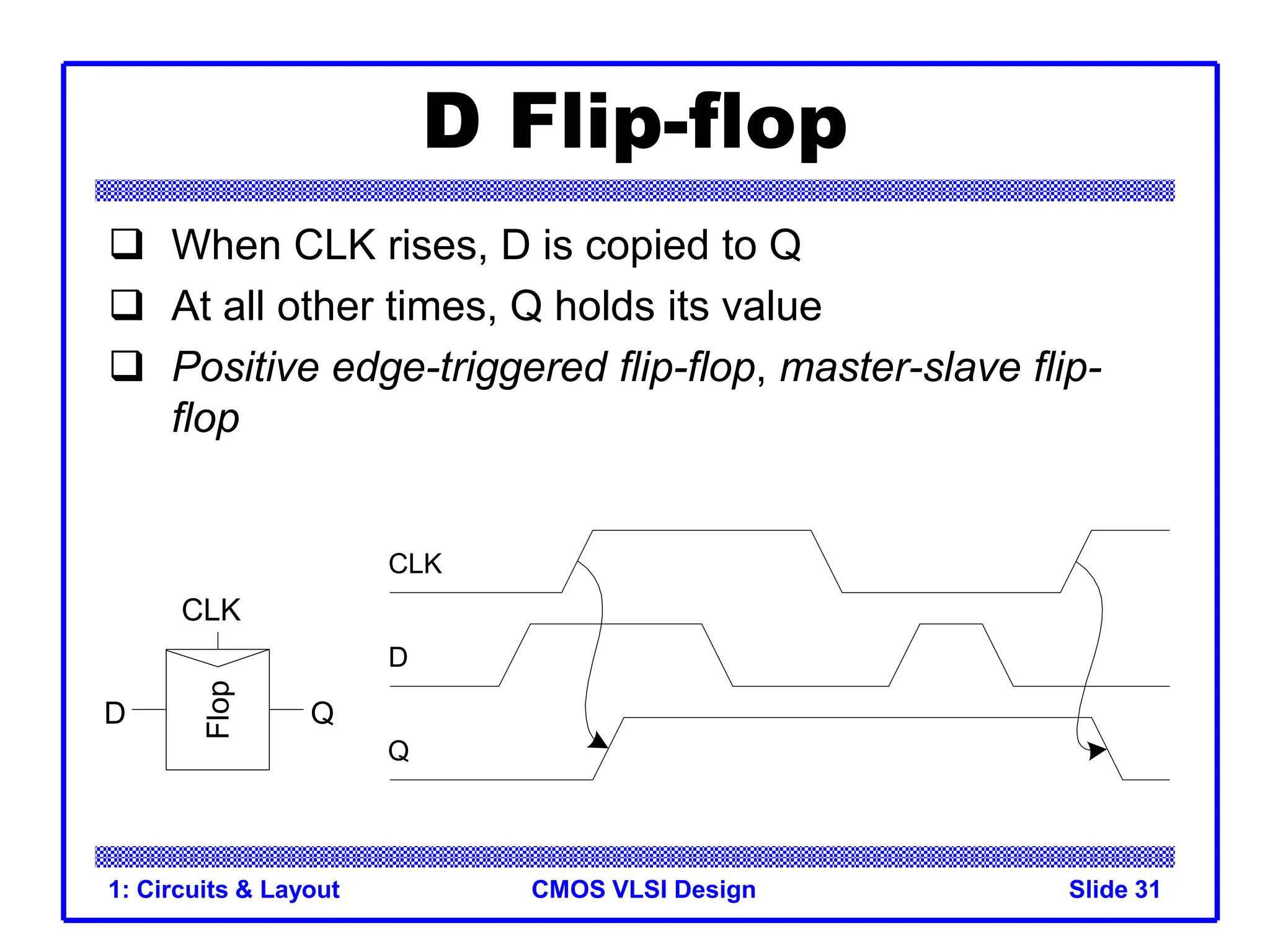

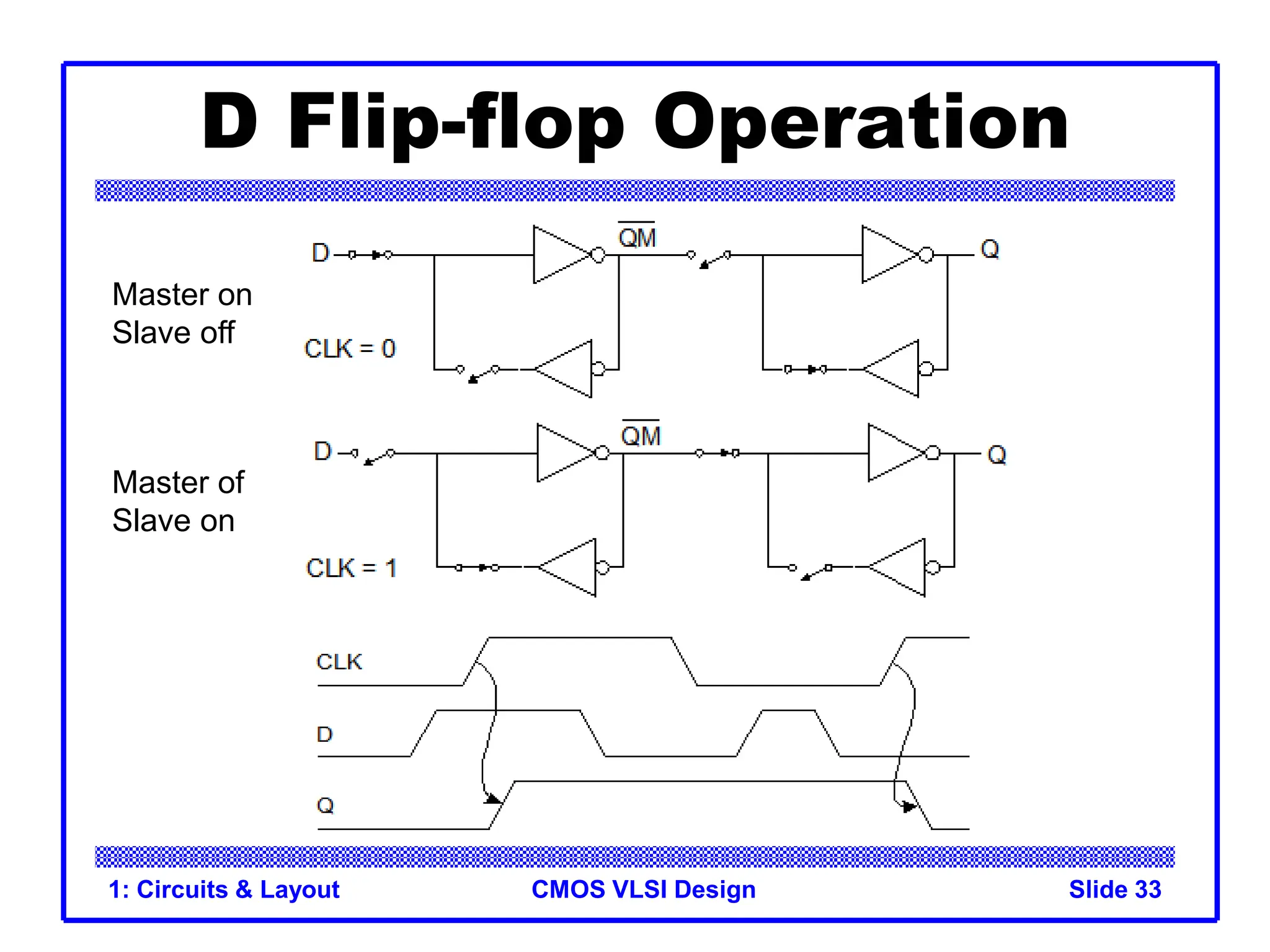

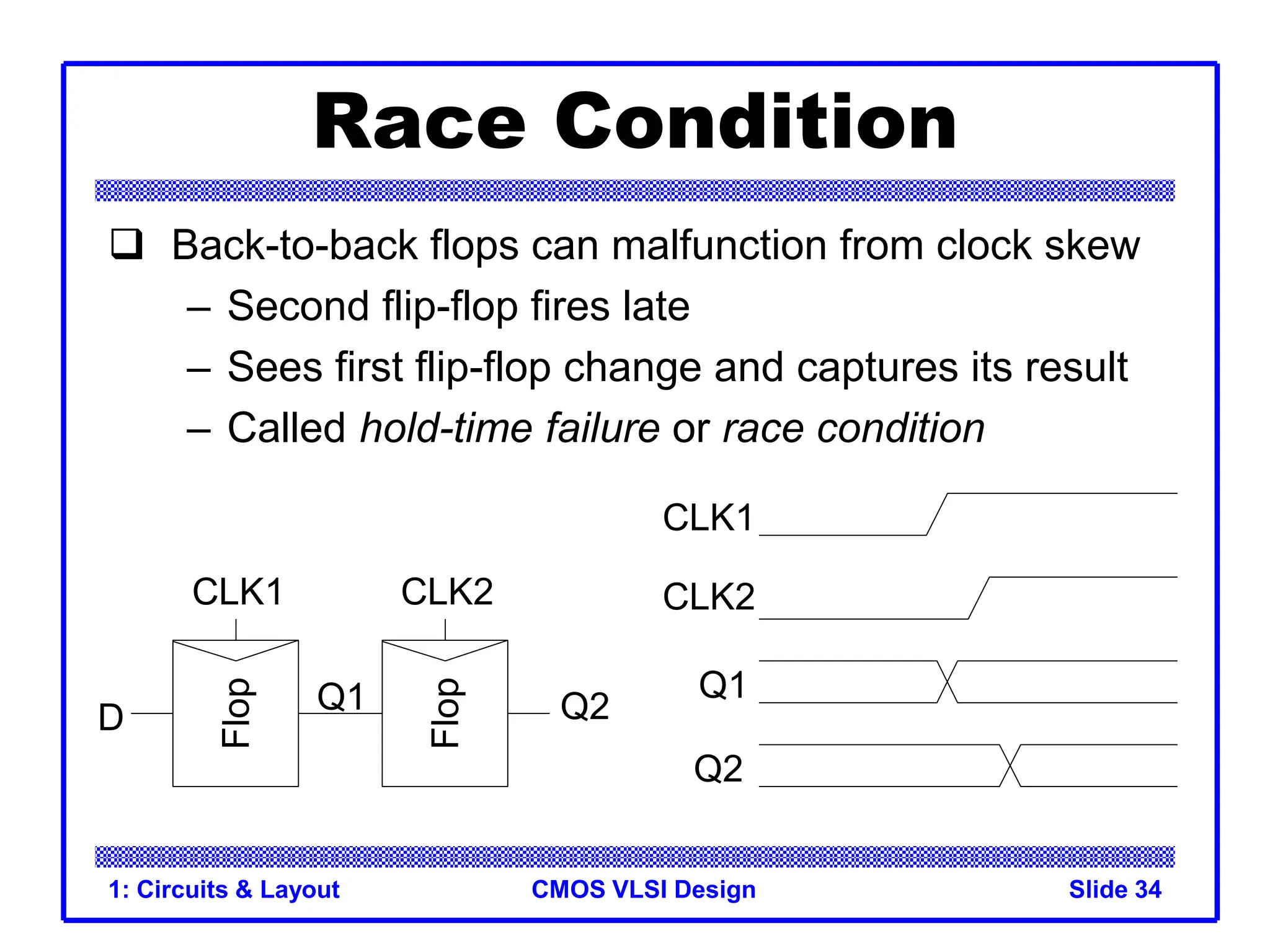

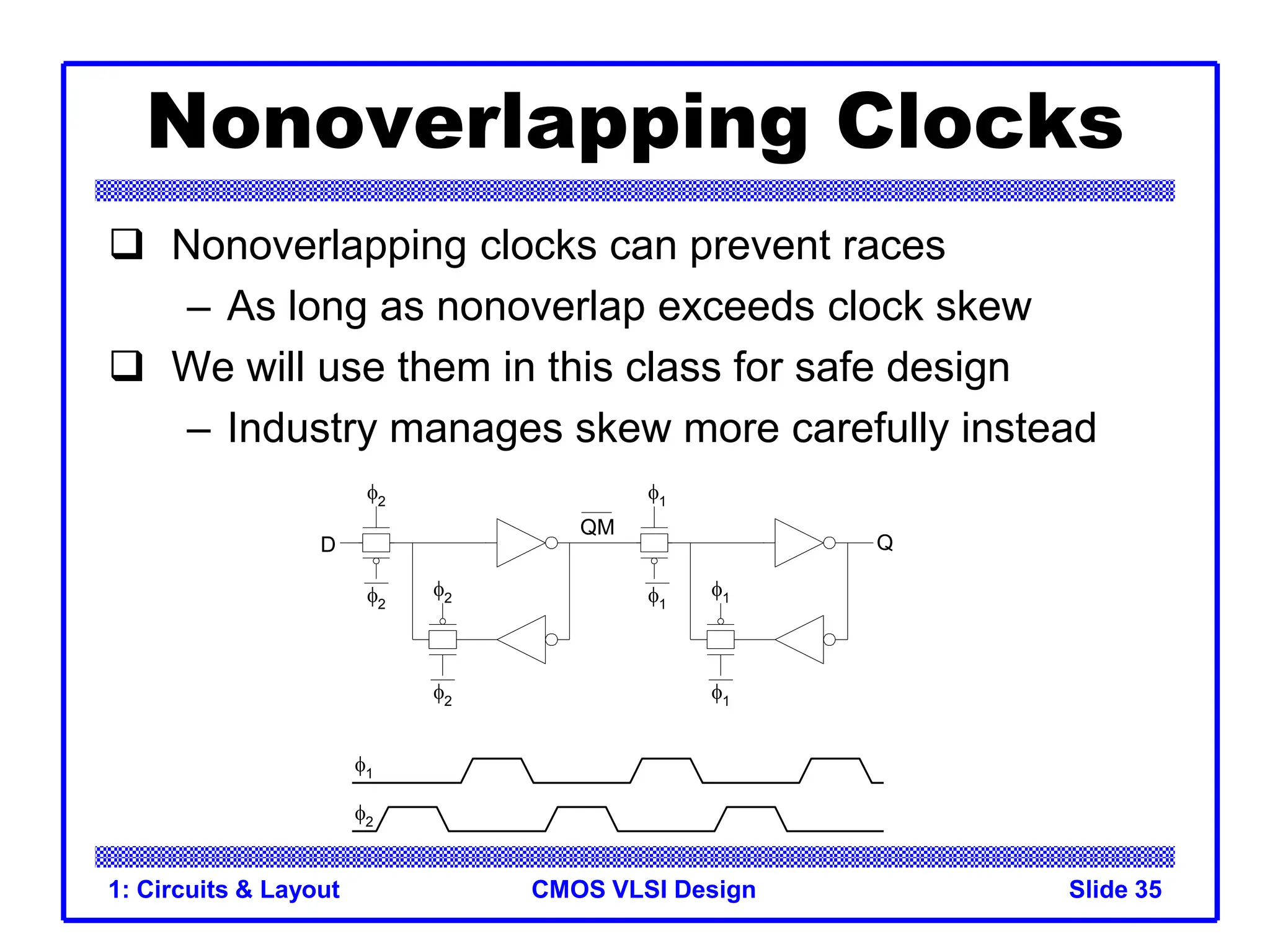

3) The design and operation of basic latches and flip-flops using D latches and a master-slave flip-flop configuration to prevent race conditions between clock signals.