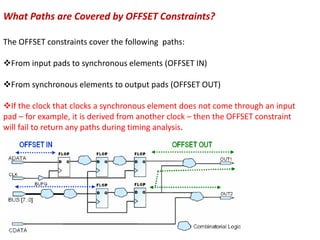

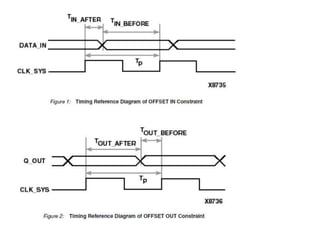

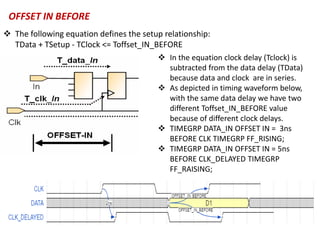

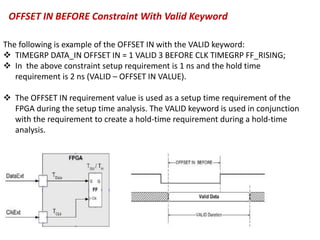

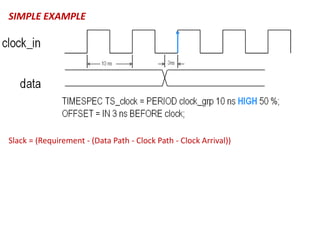

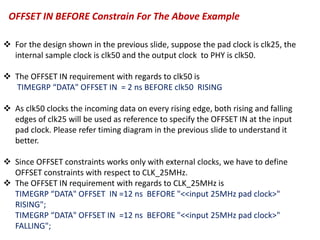

OFFSET constraints define the timing relationship between external clock pads and their corresponding input or output data. OFFSET IN constraints ensure external input data meets the setup time of internal flip-flops, while OFFSET OUT constraints control downstream device timing. These constraints are important for specifying interfaces with external components.