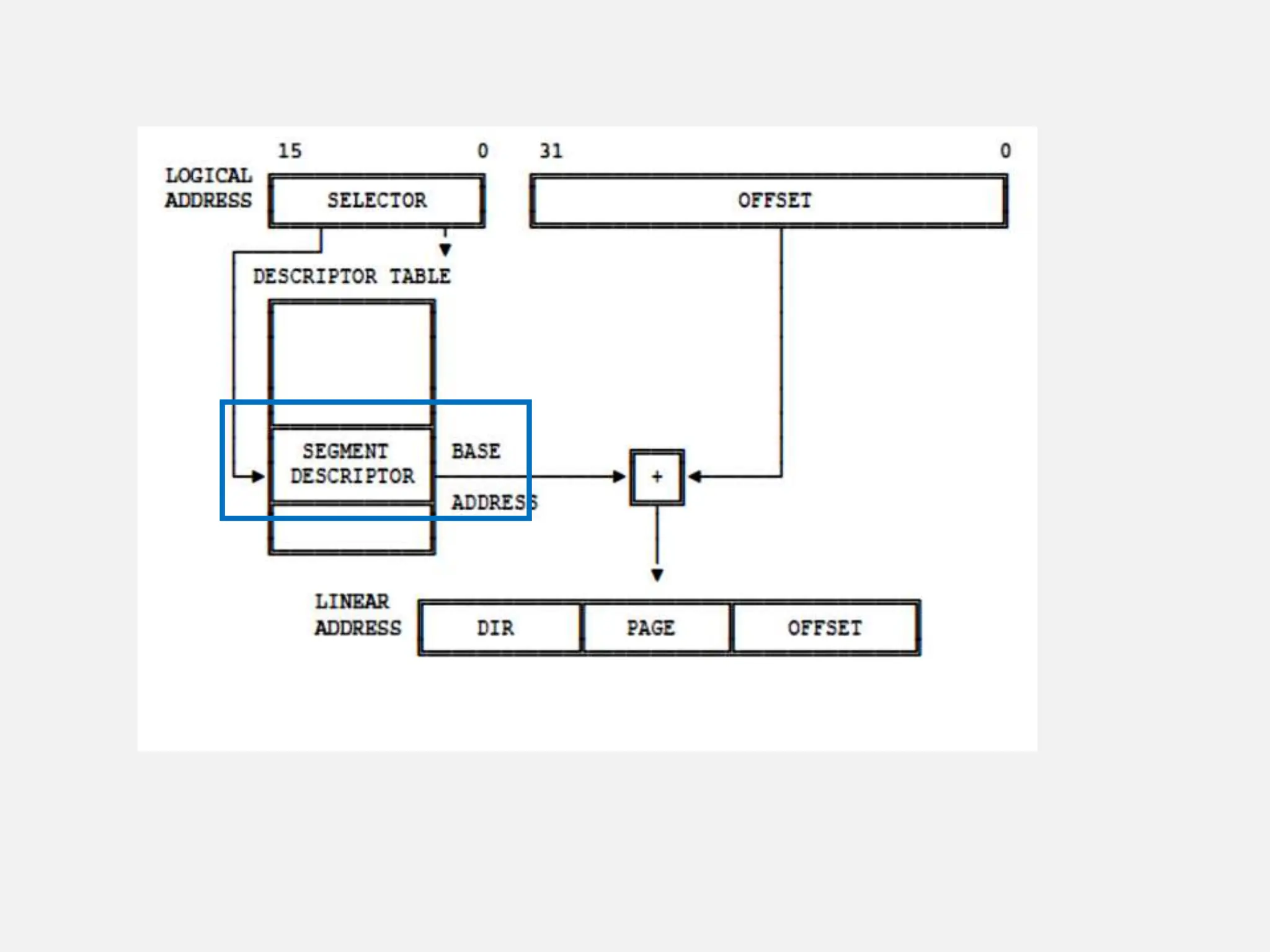

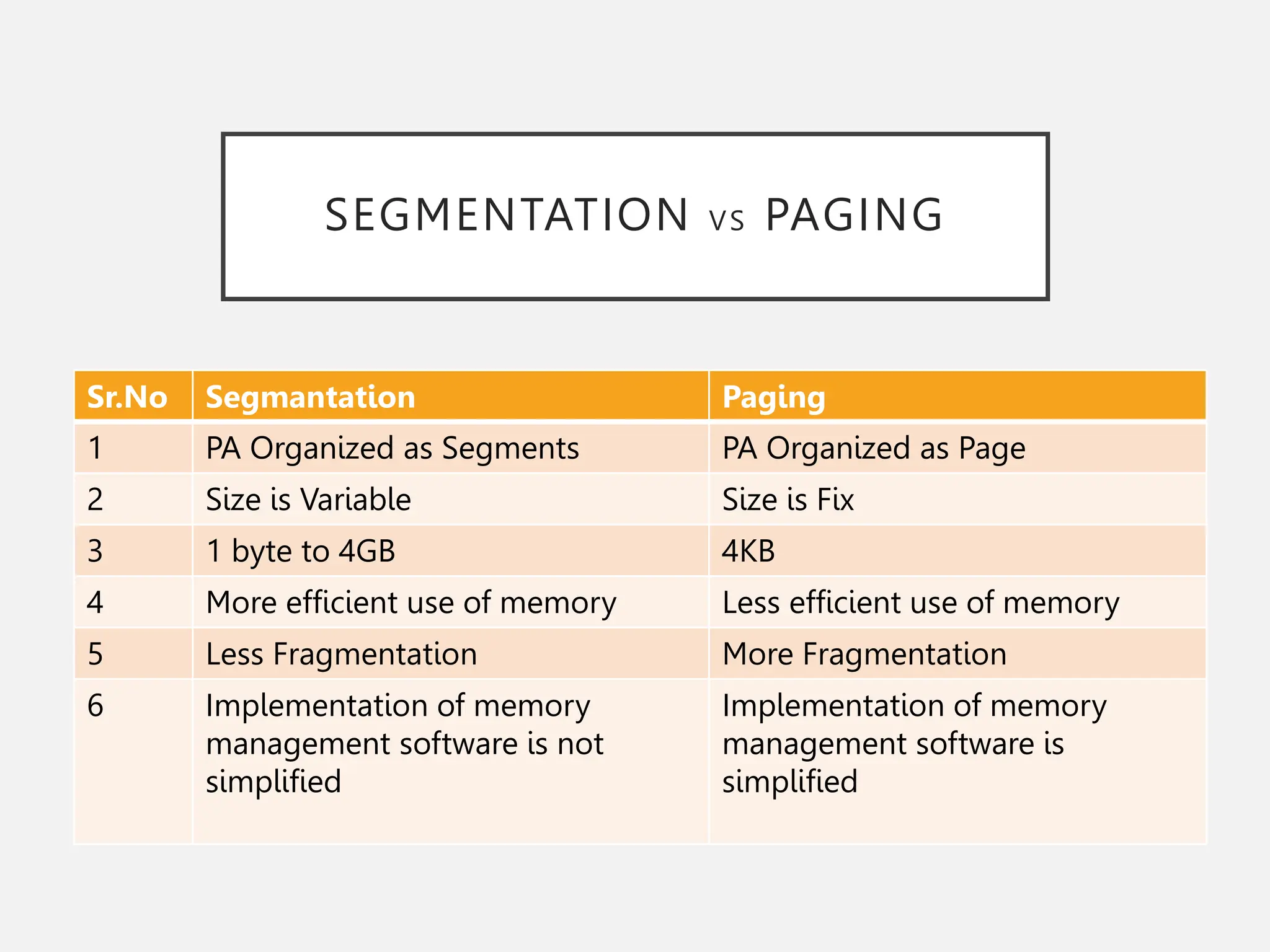

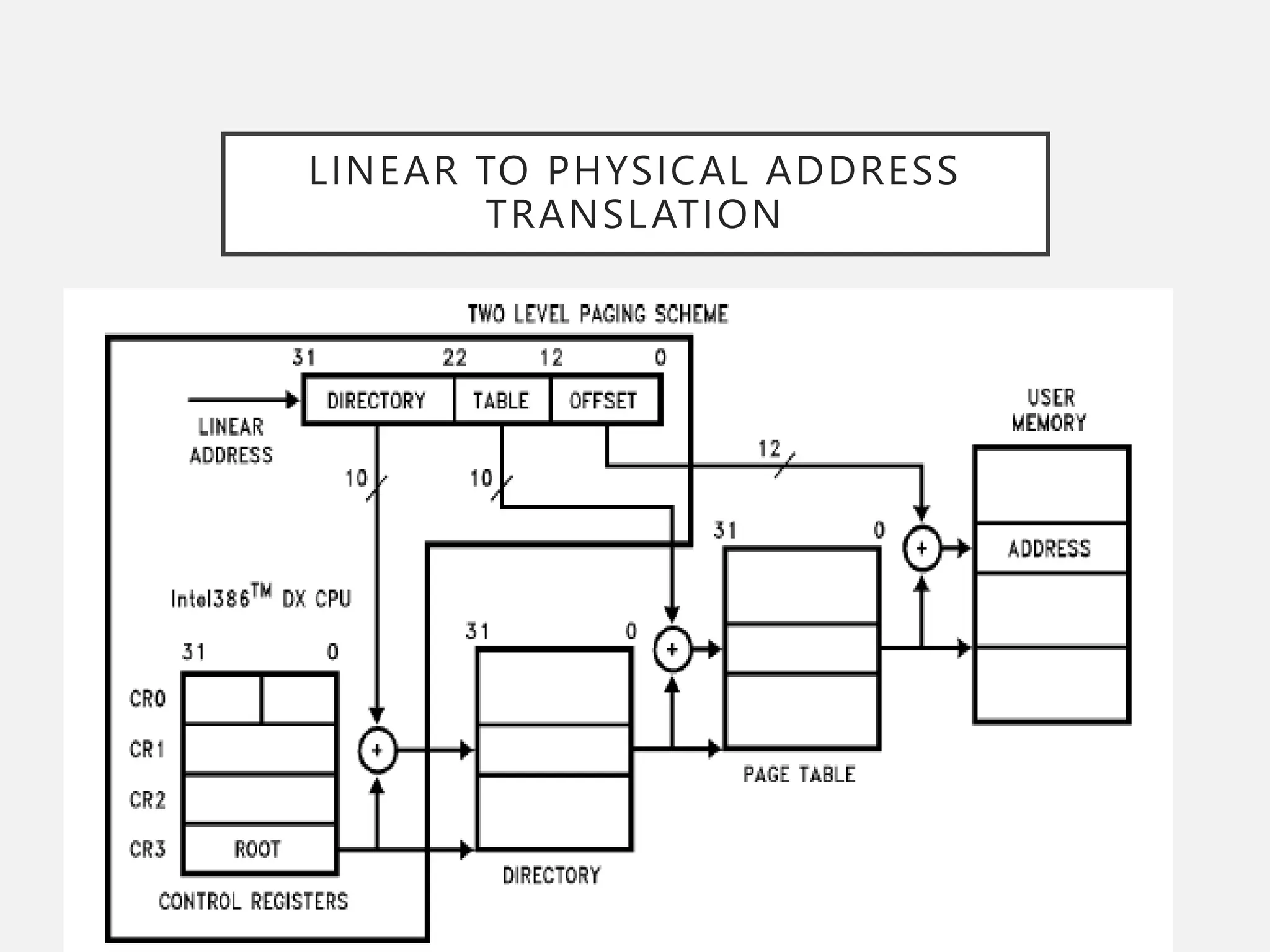

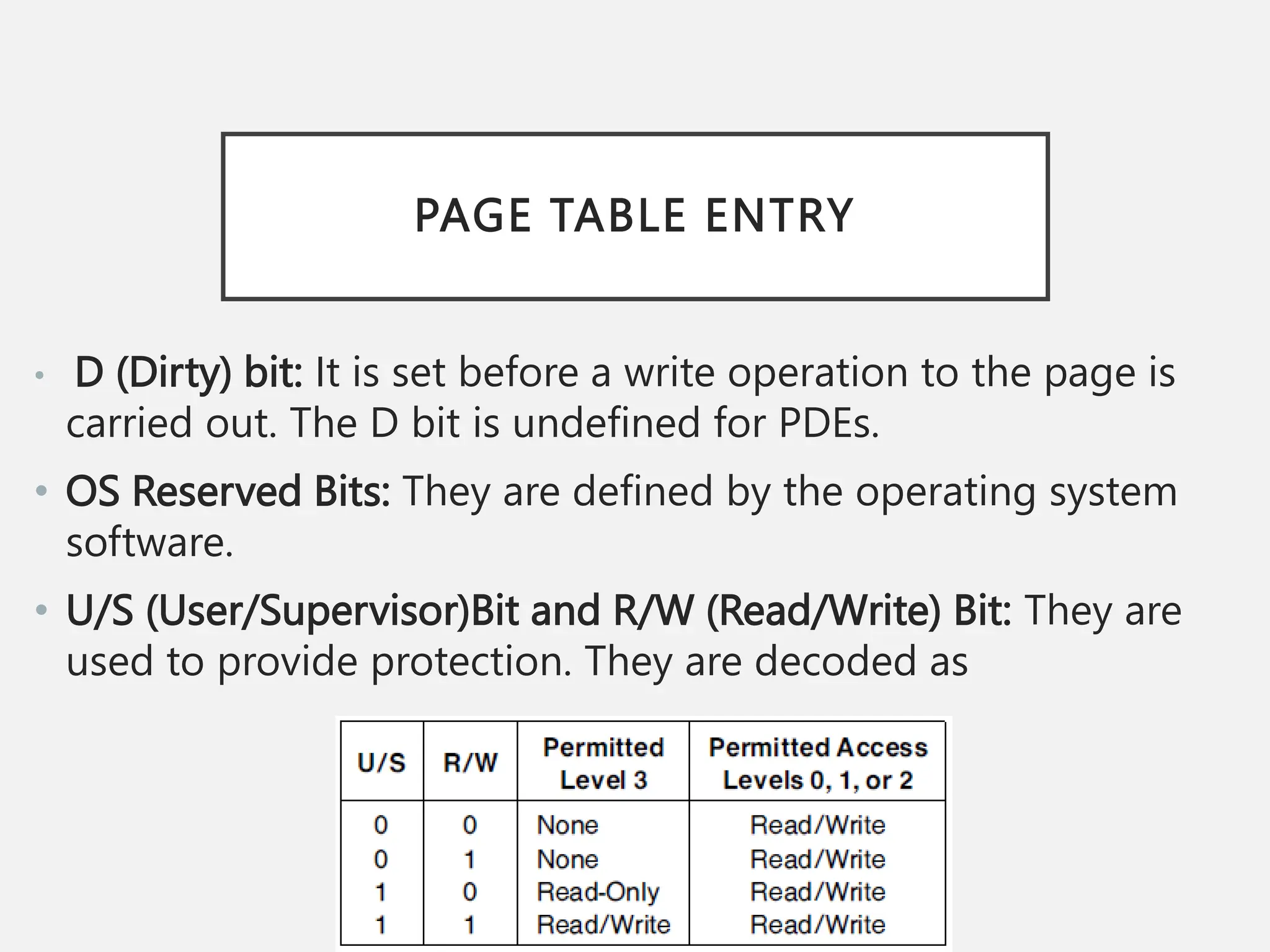

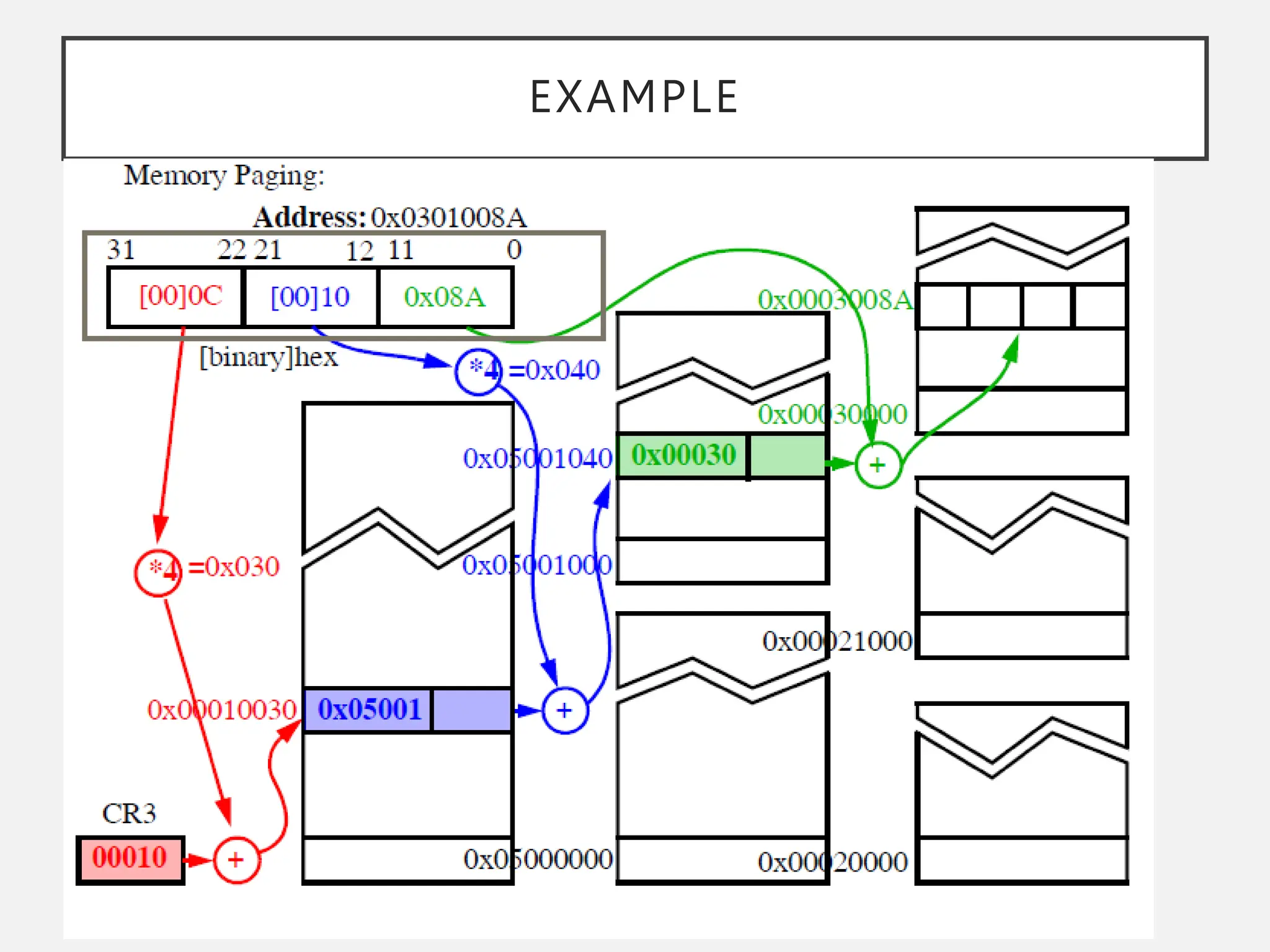

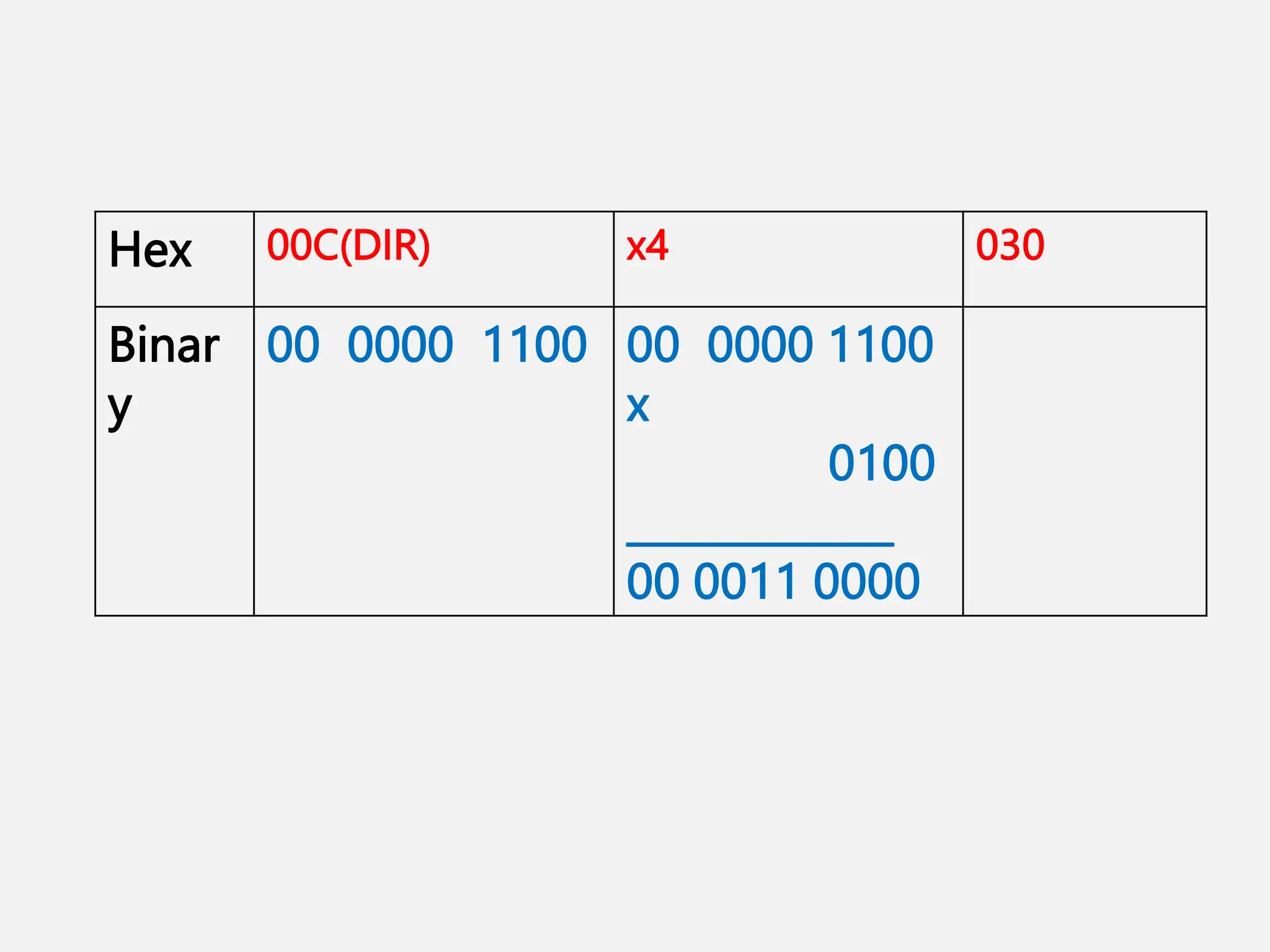

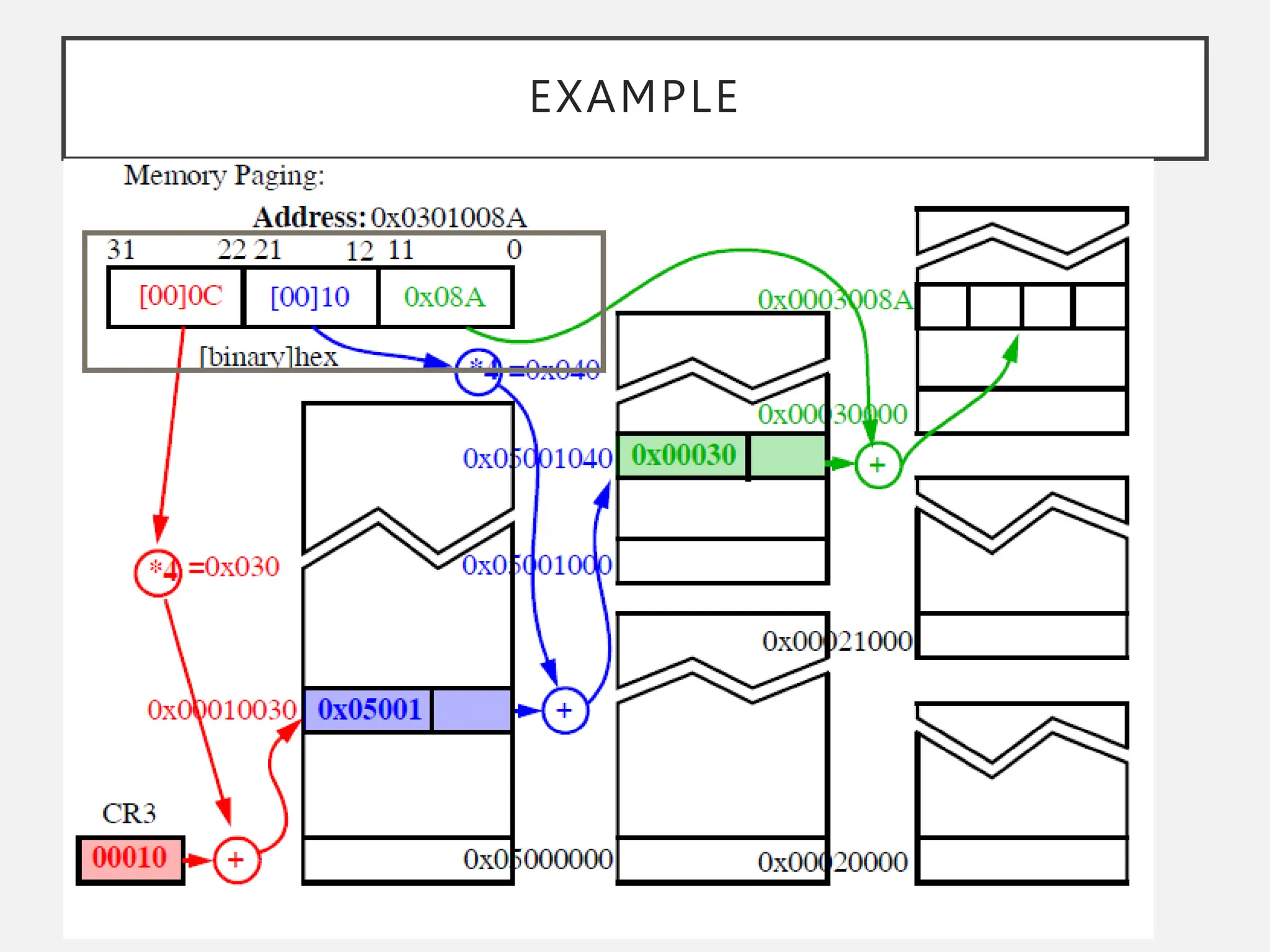

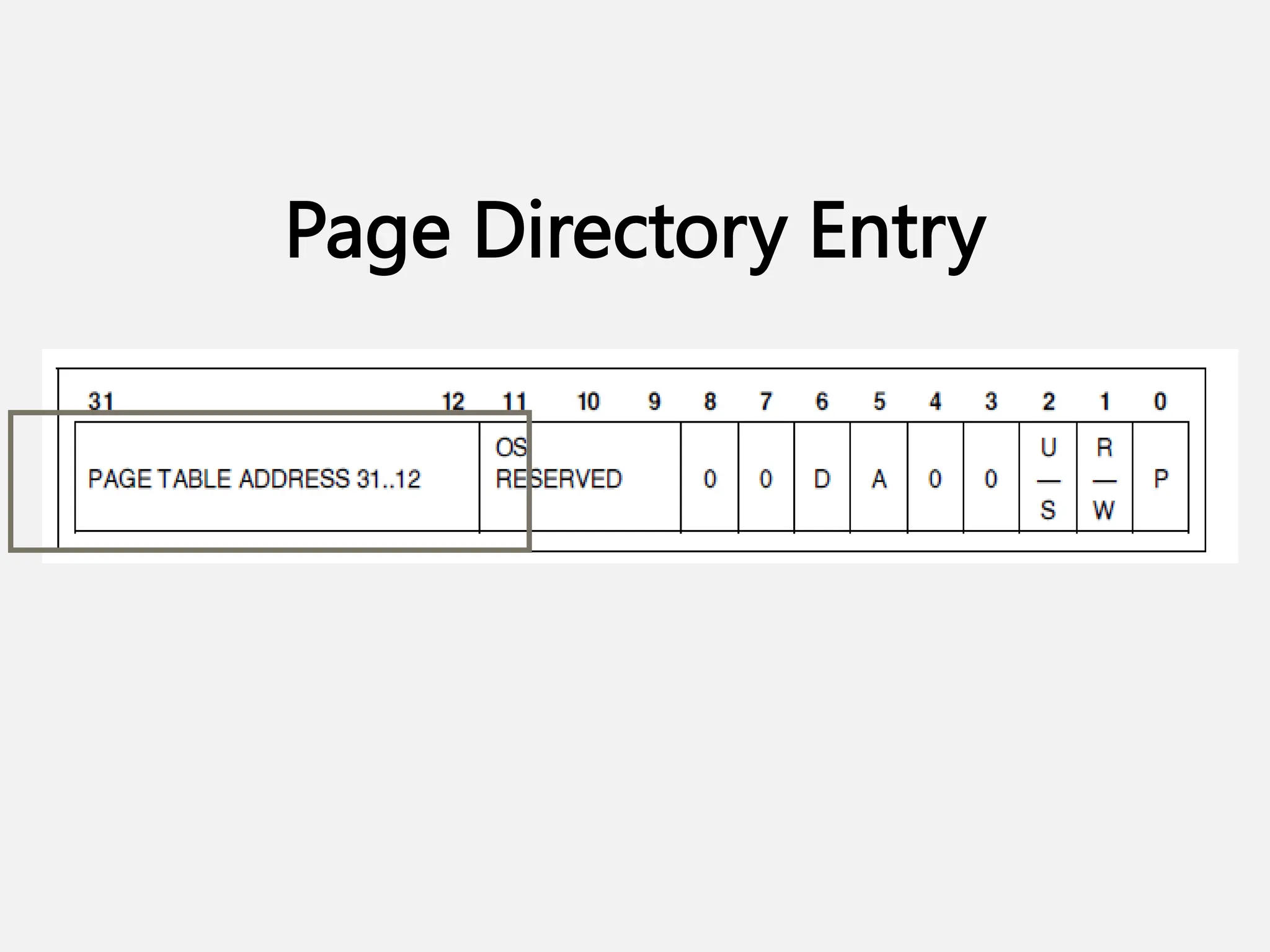

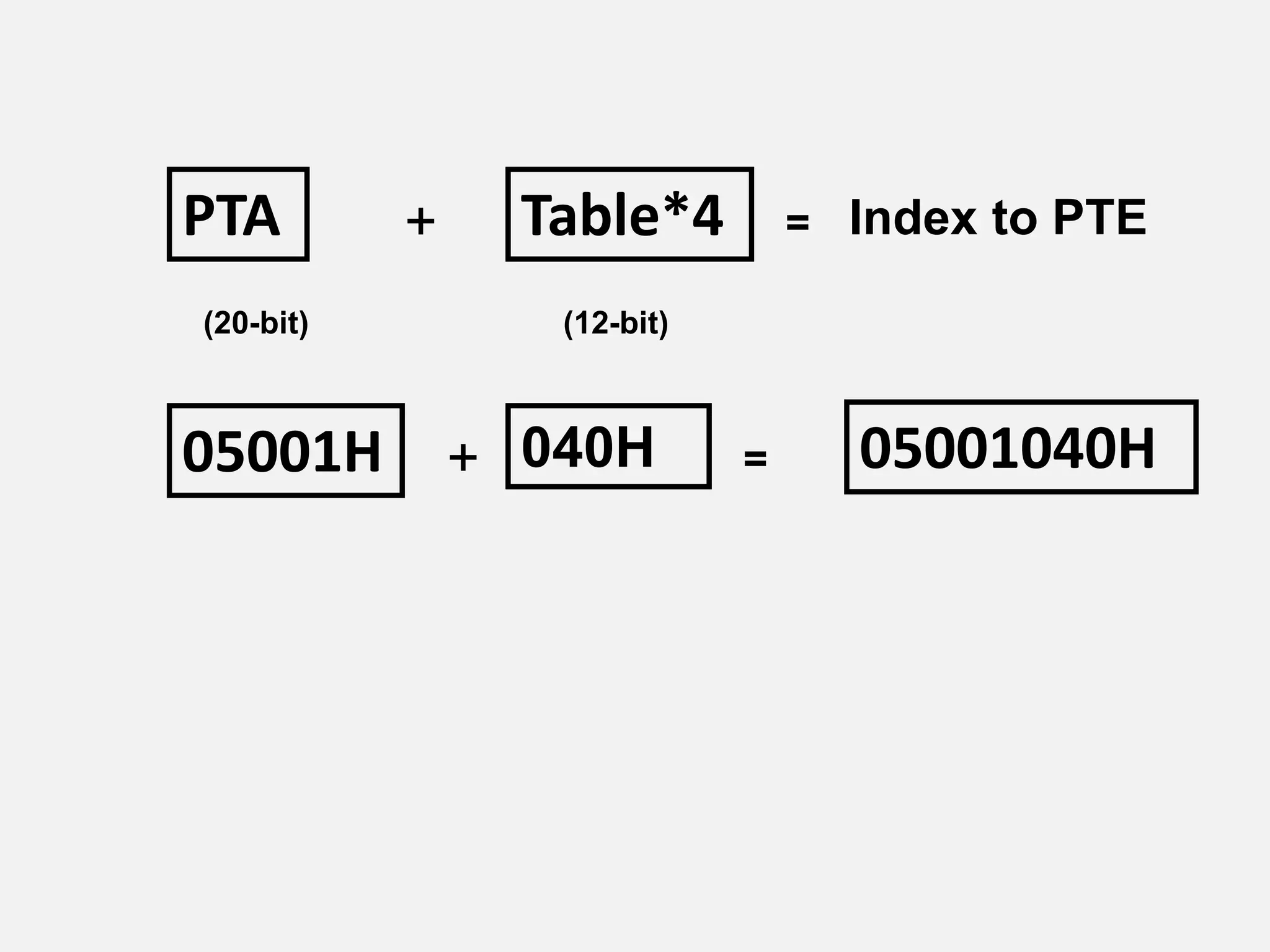

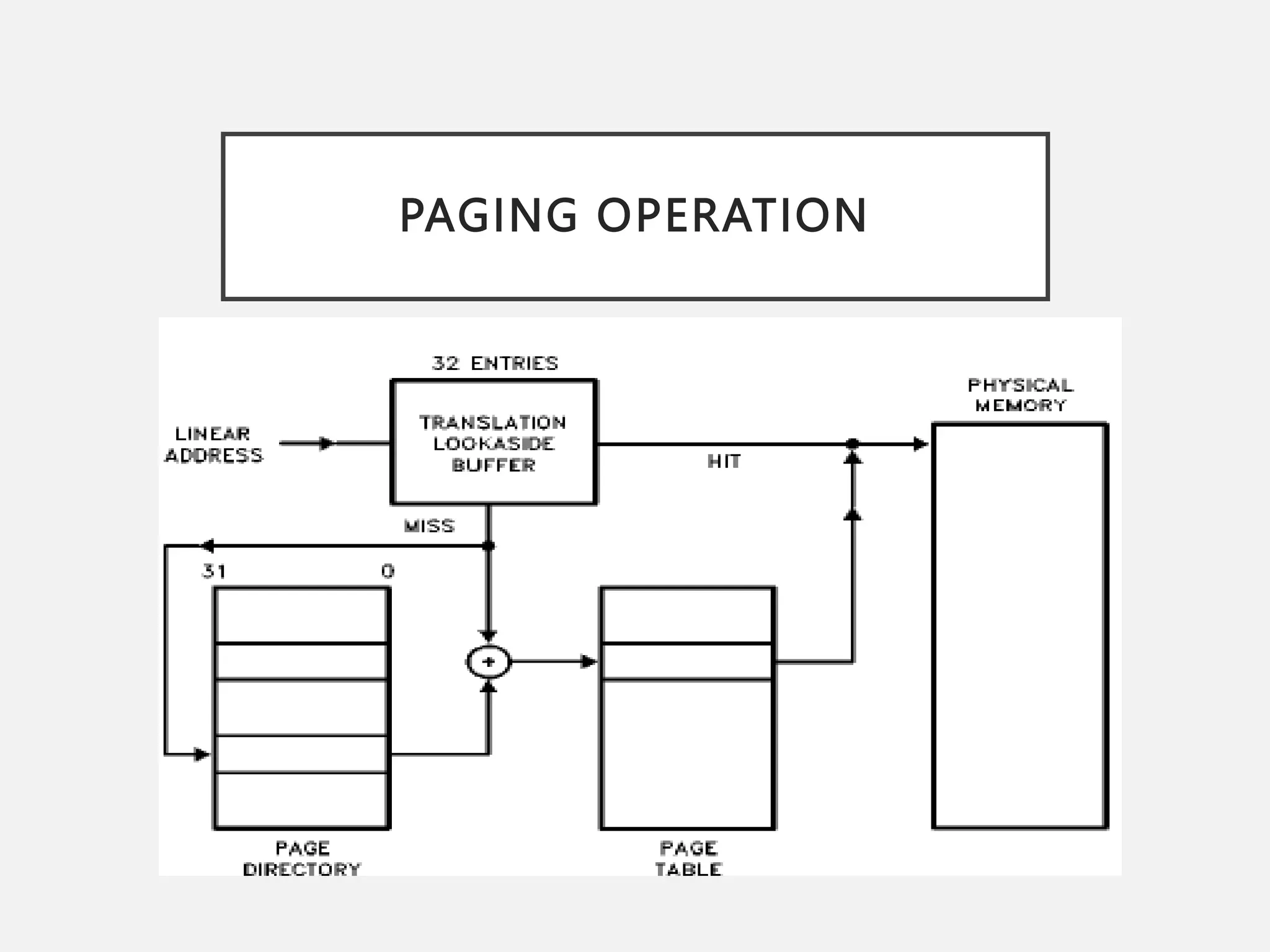

The document summarizes the address translation mechanism of the Intel 80386 processor. It describes how the 80386 uses a two-level address translation process, including segment translation to convert a logical address to a linear address, and page translation to convert the linear address to a physical address. It provides details on how the 80386 uses page directories and page tables, along with a translation lookaside buffer (TLB) cache, to efficiently map linear addresses to physical addresses during the page translation process.