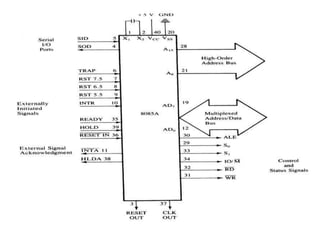

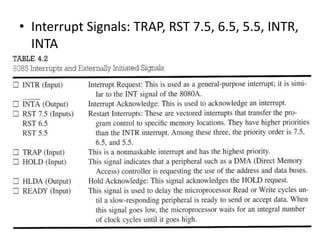

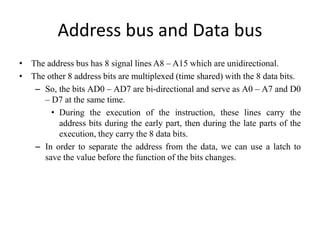

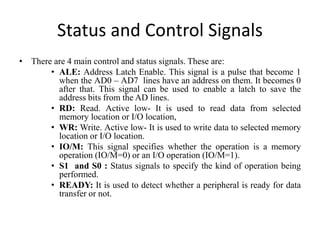

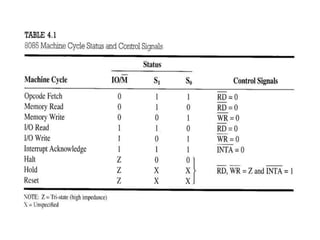

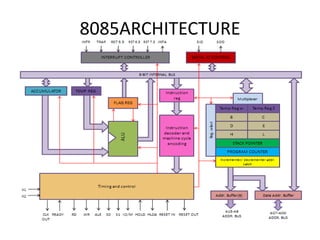

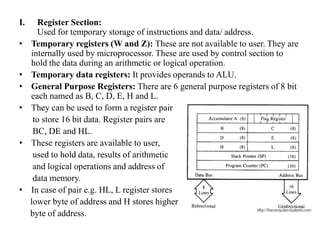

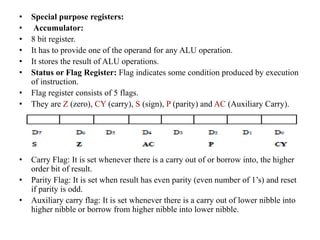

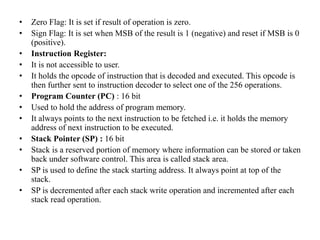

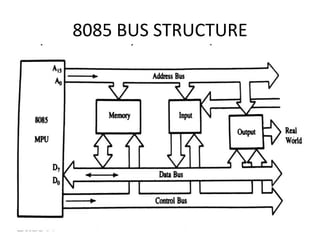

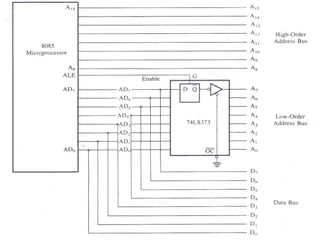

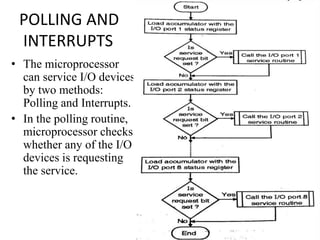

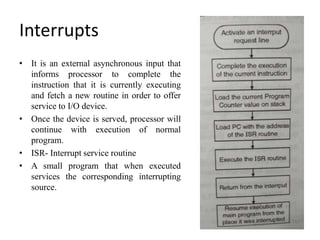

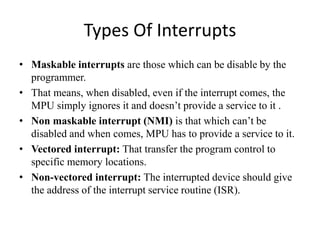

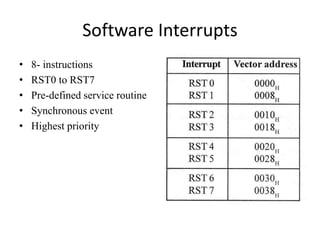

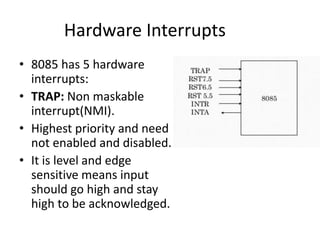

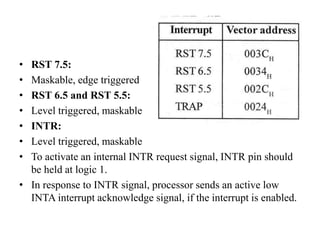

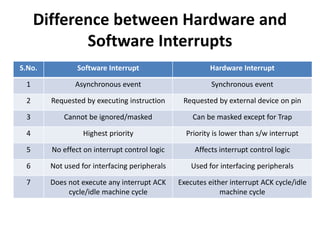

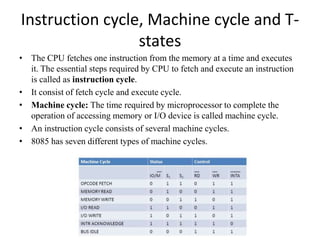

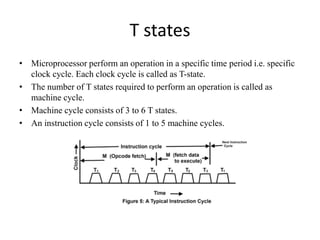

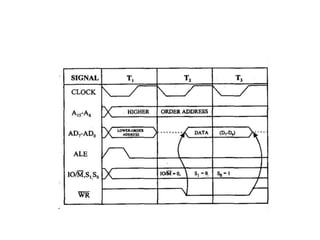

The 8085 microprocessor is an 8-bit CPU that can access 64KB of memory and has 40 pins. It has internal clock generation and 16 address lines. The pins are grouped into address bus, data bus, control signals, power/clock, external signals, and serial I/O. The document describes the architecture of the 8085 including its registers, ALU, instruction decoder, buses, and interrupt handling. It can perform memory and I/O operations using polling or interrupts.