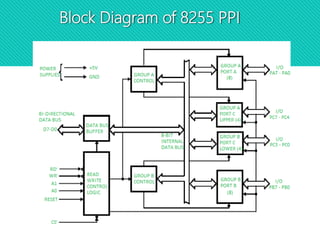

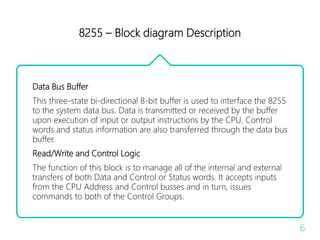

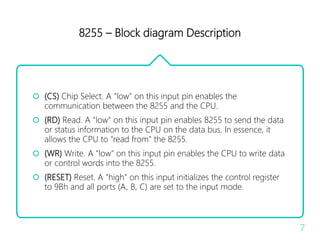

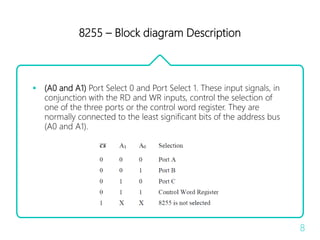

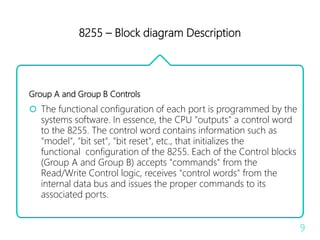

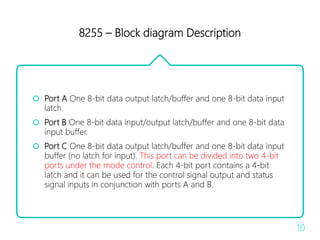

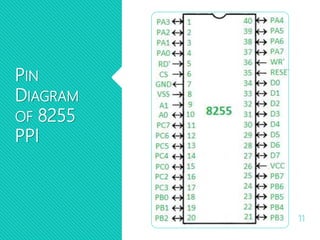

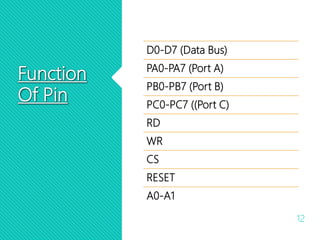

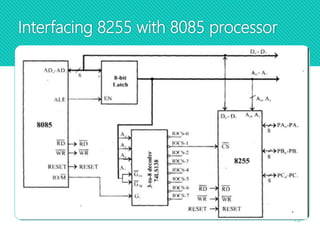

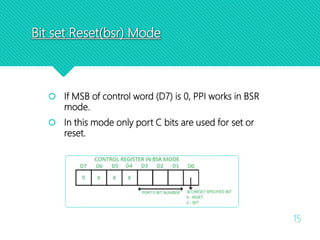

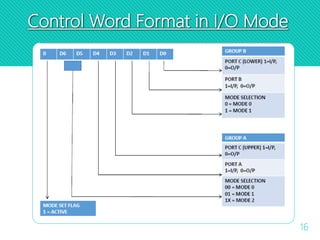

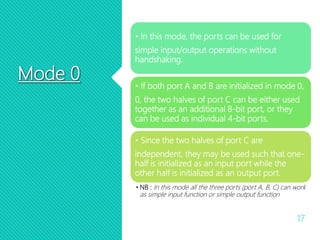

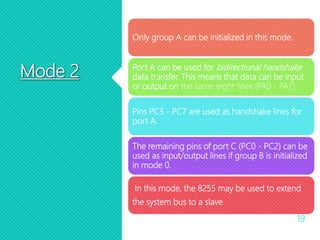

The document provides a detailed overview of the Intel 8255 programmable peripheral interface (PPI), which consists of 40 pins and is designed to facilitate communication between peripheral devices and microprocessors. It describes the block diagram, pin functions, operational modes (input/output, bit set/reset), and the control word format necessary for its configuration and operation. Each of the three 8-bit parallel I/O ports can be operated in various modes, catering to different input/output requirements.