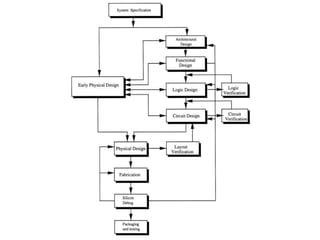

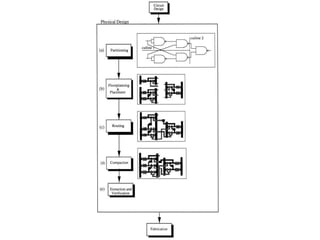

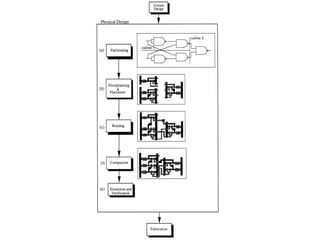

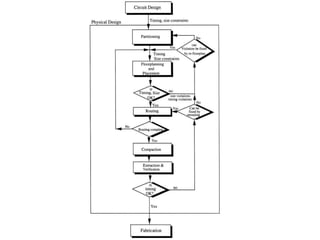

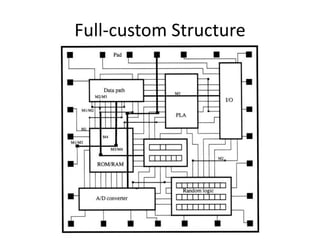

The document discusses VLSI design automation which involves converting an electrical circuit specification into a geometric layout using computers. The layout consists of geometric shapes in different layers which are used to produce photolithographic masks for fabricating chips. Physical design is the process of converting a circuit into a layout and involves steps like logic design, circuit design and placement and routing of components on the layout. Automation tools help implement the complex physical design process.