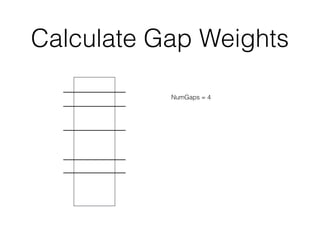

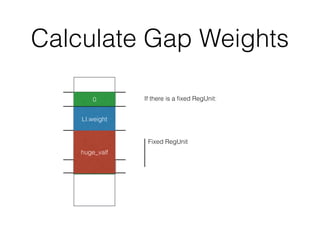

The document discusses register allocation in LLVM. It begins with an introduction to the register allocation problem and describes LLVM's base register allocation interface. It then provides more details on LLVM's basic register allocation approach and its greedy register allocation approach. The greedy approach uses techniques like live range splitting to improve register allocation.

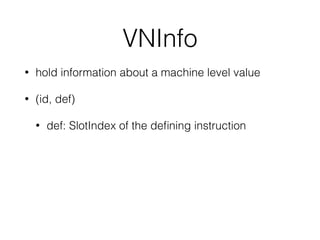

![int main()

{

int i, j;

int answer;

for (i = 1; i < 10; i++)

for (j = 1; j < 10; j++) {

answer = i * j;

}

return 0;

}

_main:

@ BB#0:

sub sp, #16

movs r0, #0

str r0, [sp, #12]

movs r0, #1

str r0, [sp, #8]

b LBB0_2

LBB0_1:

adds r1, #1

str r1, [sp, #8]

LBB0_2:

ldr r1, [sp, #8]

cmp r1, #9

bgt LBB0_6

@ BB#3:

str r0, [sp, #4]

b LBB0_5

LBB0_4:

ldr r2, [sp, #4]

muls r1, r2, r1

str r1, [sp]

ldr r1, [sp, #4]

adds r1, #1](https://image.slidesharecdn.com/llvmregisterallocation-160322143918/85/LLVM-Register-Allocation-4-320.jpg)

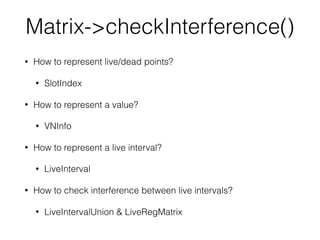

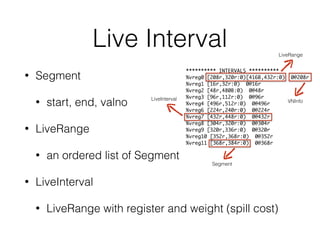

![Numbering of Machine

Instruction

0B BB#0: derived from LLVM BB %entry

16B %vreg1<def> = t2MOVi 0, pred:14, pred:%noreg, opt:%noreg; rGPR:%vreg1

32B t2STRi12 %vreg1, <fi#0>, 0, pred:14, pred:%noreg; mem:ST4[%retval] rGPR:%vreg1

48B %vreg2<def> = t2MOVi 1, pred:14, pred:%noreg, opt:%noreg; rGPR:%vreg2

64B t2STRi12 %vreg2, <fi#1>, 0, pred:14, pred:%noreg; mem:ST4[%i] rGPR:%vreg2

Successors according to CFG: BB#1

for (MachineBasicBlock::iterator miItr = mbb->begin(), miEnd = mbb->end();

miItr != miEnd; ++miItr) {

MachineInstr *mi = miItr;

if (mi->isDebugValue())

continue;

// Insert a store index for the instr.

indexList.push_back(createEntry(mi, index += SlotIndex::InstrDist));

// Save this base index in the maps.

mi2iMap.insert(std::make_pair(mi, SlotIndex(&indexList.back(),

SlotIndex::Slot_Block)));

}](https://image.slidesharecdn.com/llvmregisterallocation-160322143918/85/LLVM-Register-Allocation-18-320.jpg)

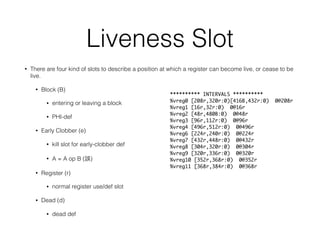

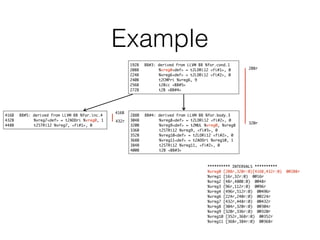

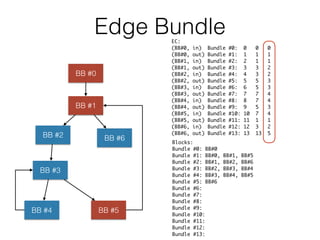

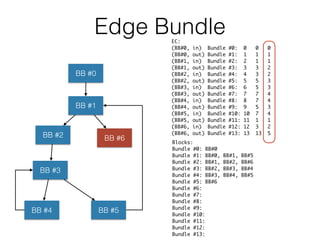

![Edge Bundle

BB #0

BB #1

BB #3

BB #2

BB #4 BB #5

BB #6

// Join the outgoing bundle with the ingoing bundles of all successors.

for (MachineBasicBlock::const_succ_iterator SI = MBB.succ_begin(),

SE = MBB.succ_end(); SI != SE; ++SI)

EC.join(OutE, 2 * (*SI)->getNumber());

EC:

(BB#0, in) Bundle #0: 0 0 0

(BB#0, out) Bundle #1: 1 1 1

(BB#1, in) Bundle #2: 2 1 1

(BB#1, out) Bundle #3: 3 3 2

(BB#2, in) Bundle #4: 4 3 2

(BB#2, out) Bundle #5: 5 5 3

(BB#3, in) Bundle #6: 6 5 3

(BB#3, out) Bundle #7: 7 7 4

(BB#4, in) Bundle #8: 8 7 4

(BB#4, out) Bundle #9: 9 5 3

(BB#5, in) Bundle #10: 10 7 4

(BB#5, out) Bundle #11: 11 1 1

(BB#6, in) Bundle #12: 12 3 2

(BB#6, out) Bundle #13: 13 13 5

void join(unsigned a, unsigned b) {

unsigned eca = EC[a];

unsigned ecb = EC[b];

while (eca != ecb)

if (eca < ecb)

EC[b] = eca, b = ecb, ecb = EC[b];

else

EC[a] = ecb, a = eca, eca = EC[a];

}](https://image.slidesharecdn.com/llvmregisterallocation-160322143918/85/LLVM-Register-Allocation-51-320.jpg)

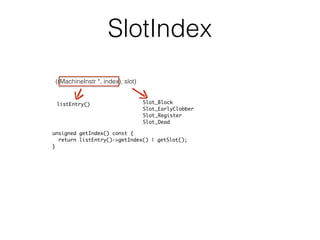

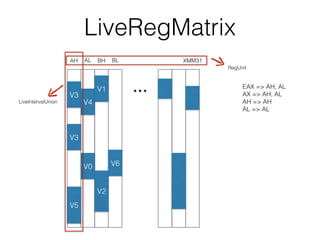

![SpillPlacement::iterate

for (unsigned iteration = 0; iteration != 10; ++iteration) {

bool Changed = false;

for (SmallVectorImpl<unsigned>::const_reverse_iterator I =

iteration == 0 ? Linked.rbegin() : std::next(Linked.rbegin()),

E = Linked.rend(); I != E; ++I) {

unsigned n = *I;

if (nodes[n].update(nodes, Threshold)) {

Changed = true;

if (nodes[n].preferReg())

RecentPositive.push_back(n);

}

}

if (!Changed || !RecentPositive.empty())

return;

Changed = false;

for (SmallVectorImpl<unsigned>::const_iterator I =

std::next(Linked.begin()), E = Linked.end(); I != E; ++I) {

unsigned n = *I;

if (nodes[n].update(nodes, Threshold)) {

Changed = true;

if (nodes[n].preferReg())

RecentPositive.push_back(n);

}

}

if (!Changed || !RecentPositive.empty())

return;

}](https://image.slidesharecdn.com/llvmregisterallocation-160322143918/85/LLVM-Register-Allocation-63-320.jpg)