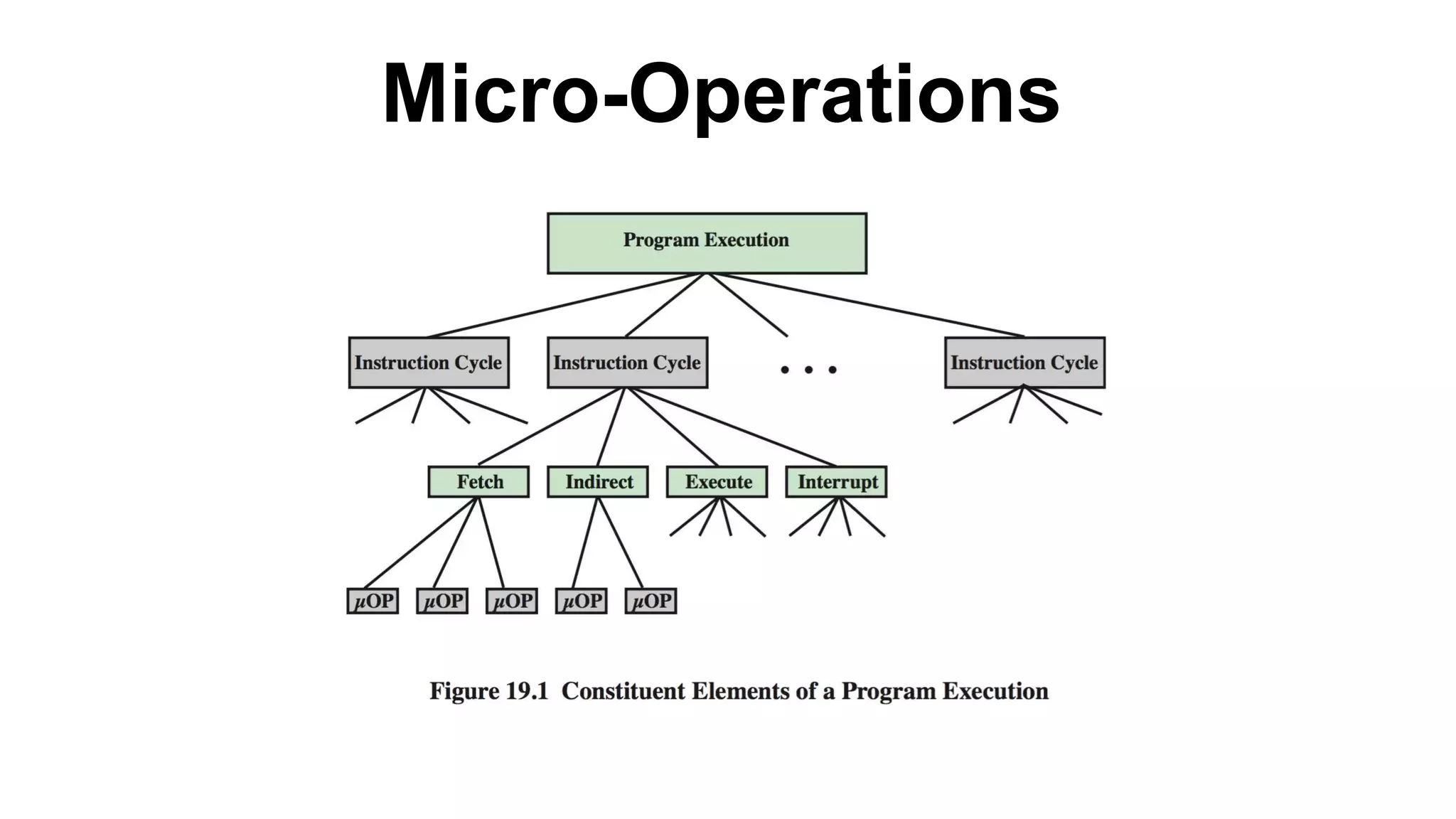

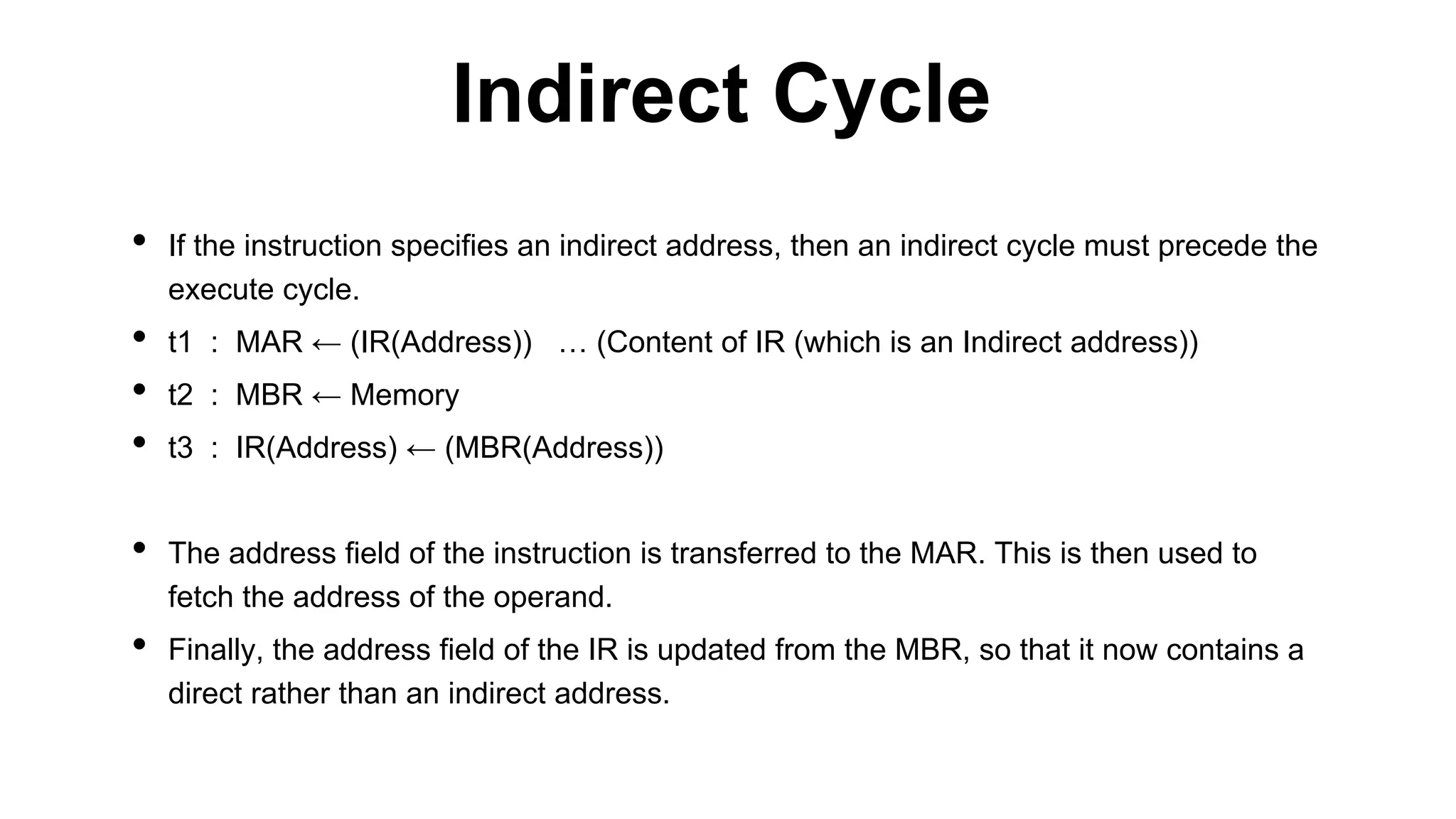

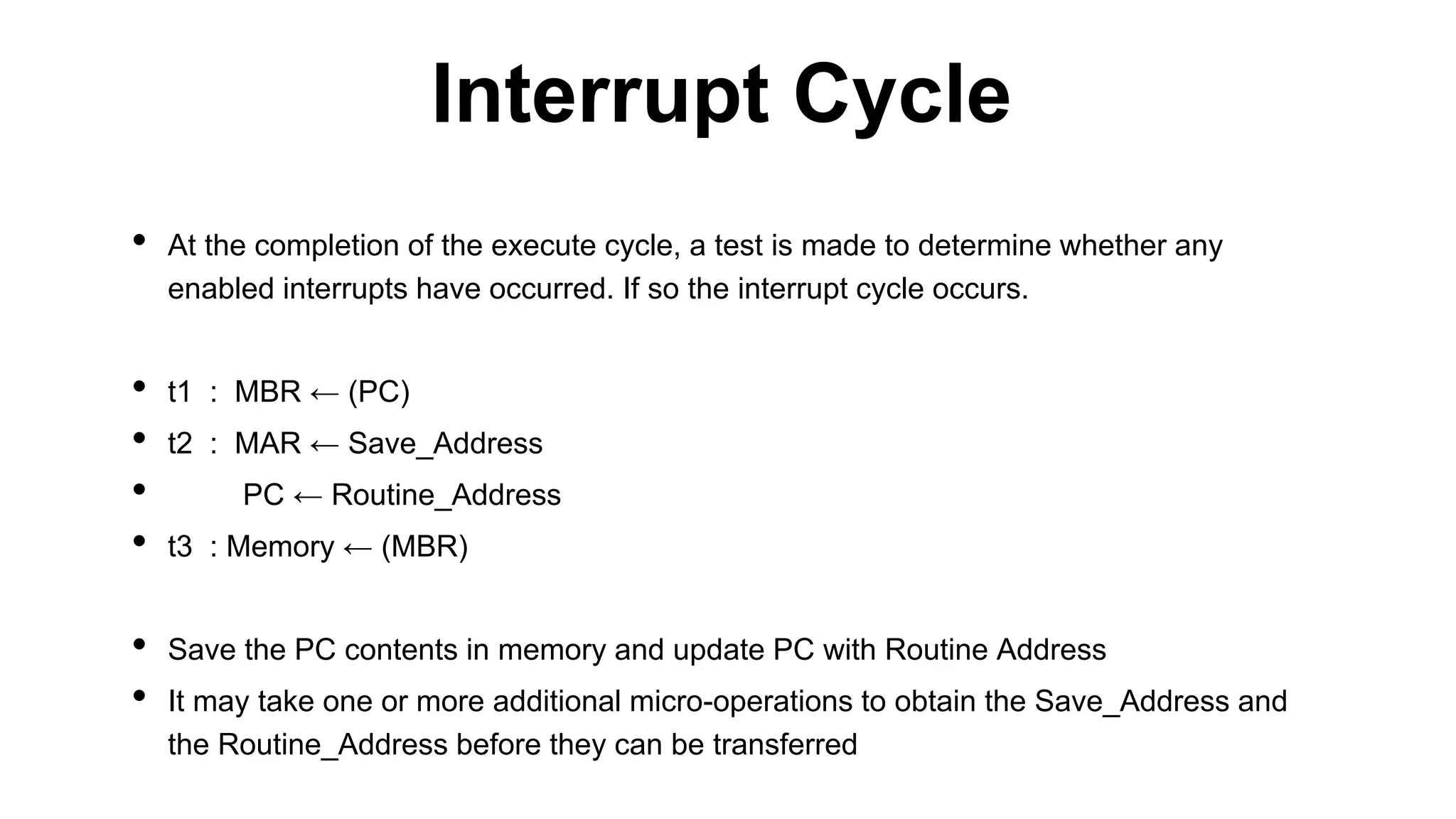

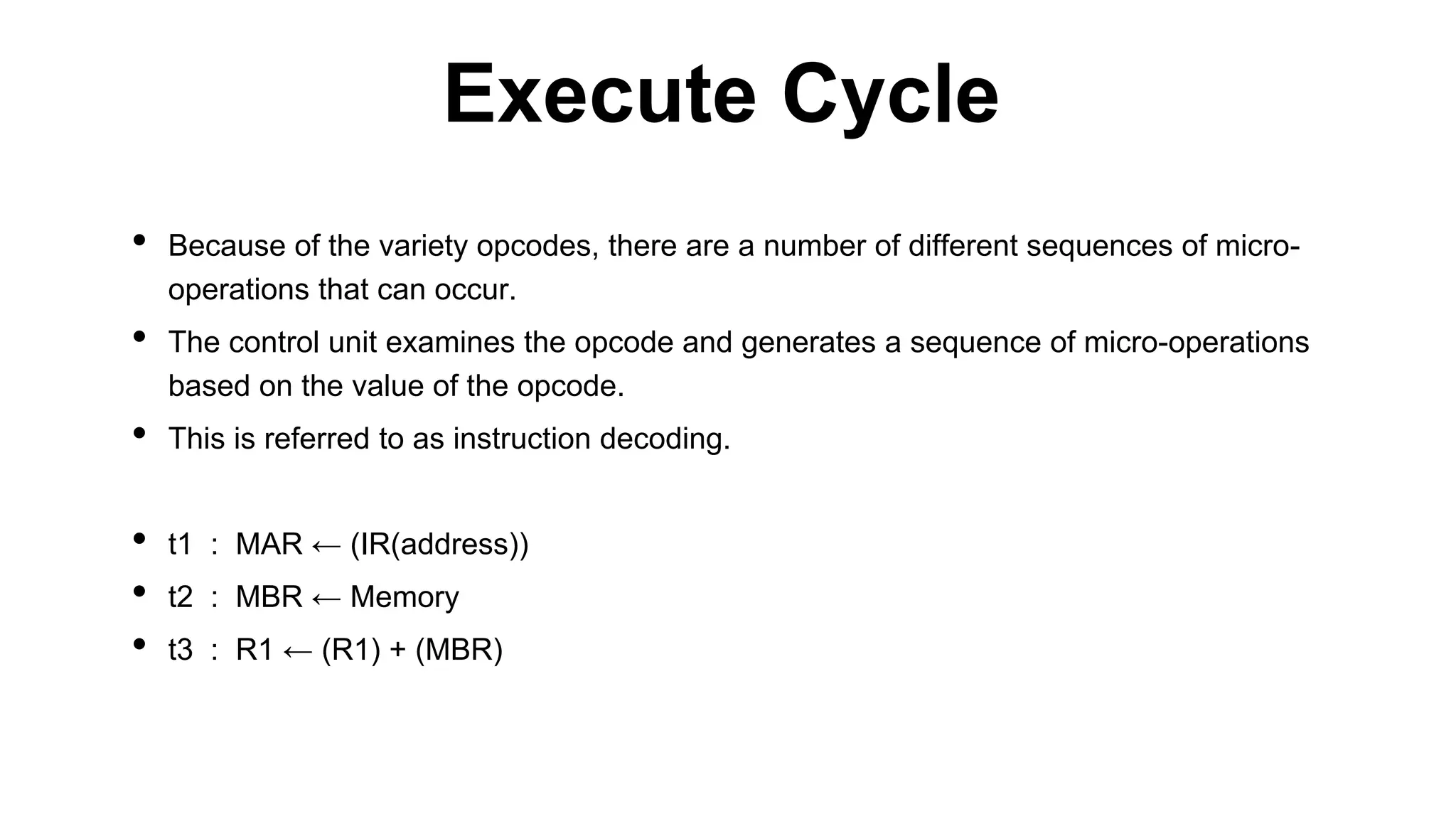

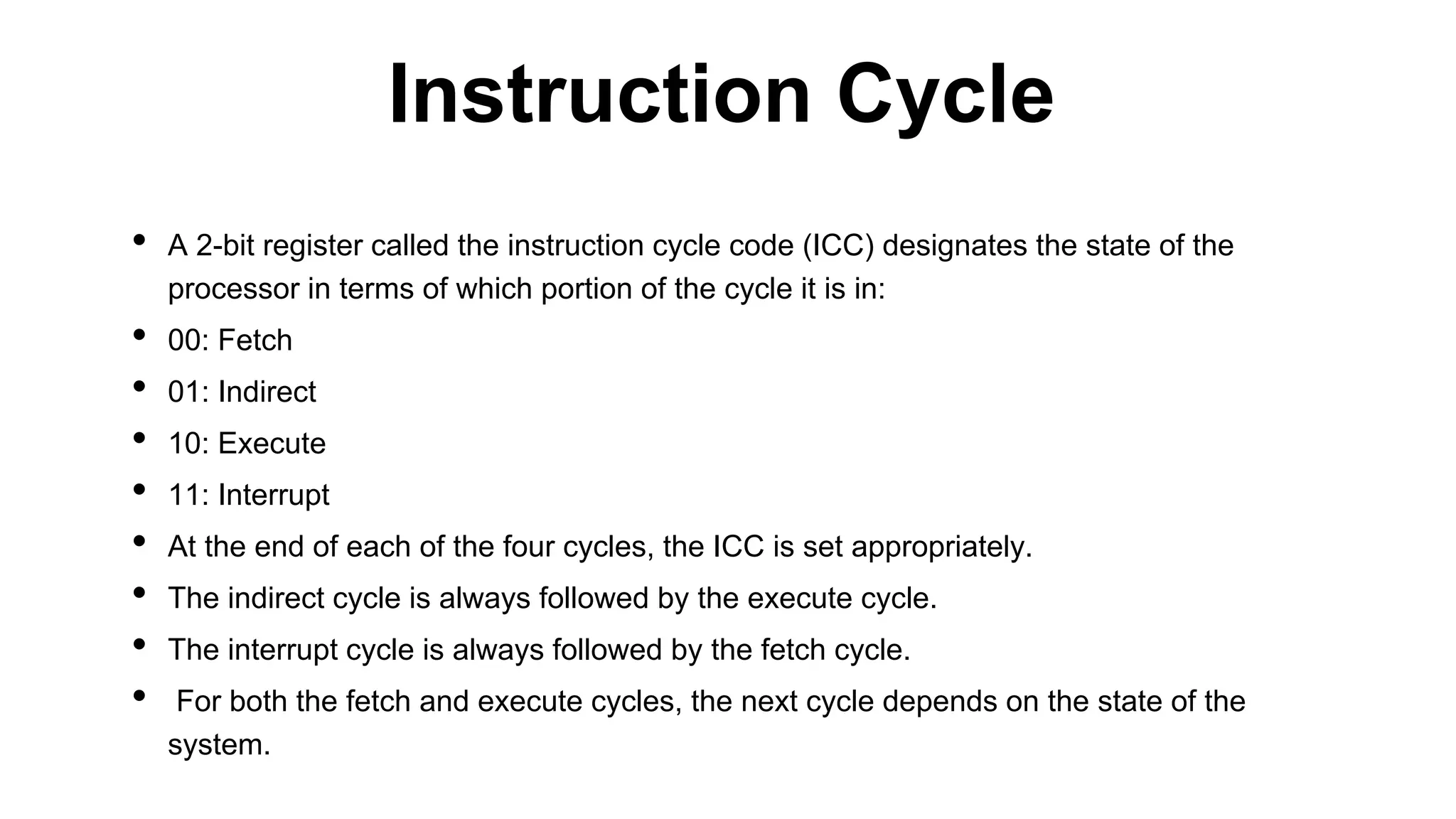

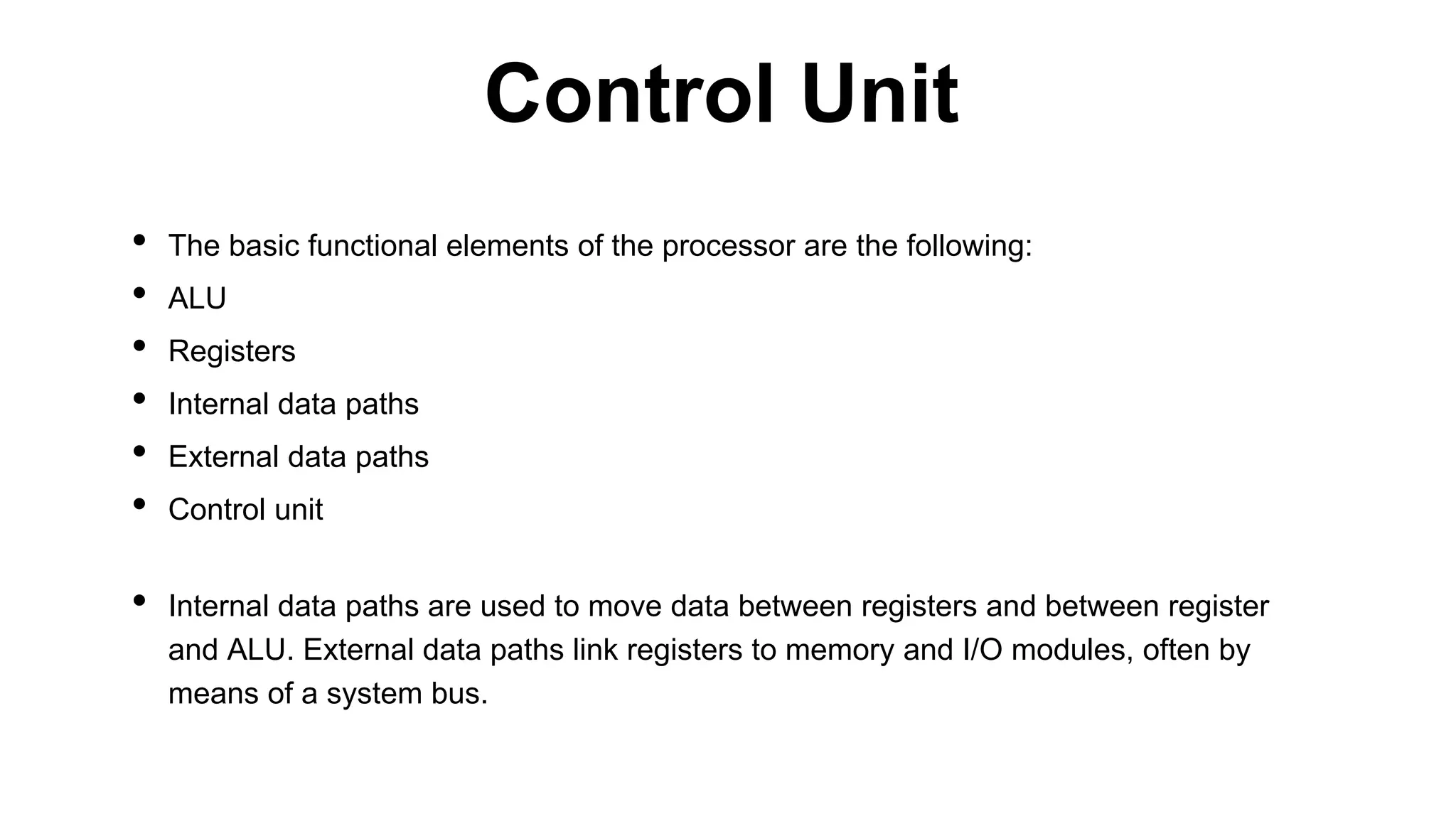

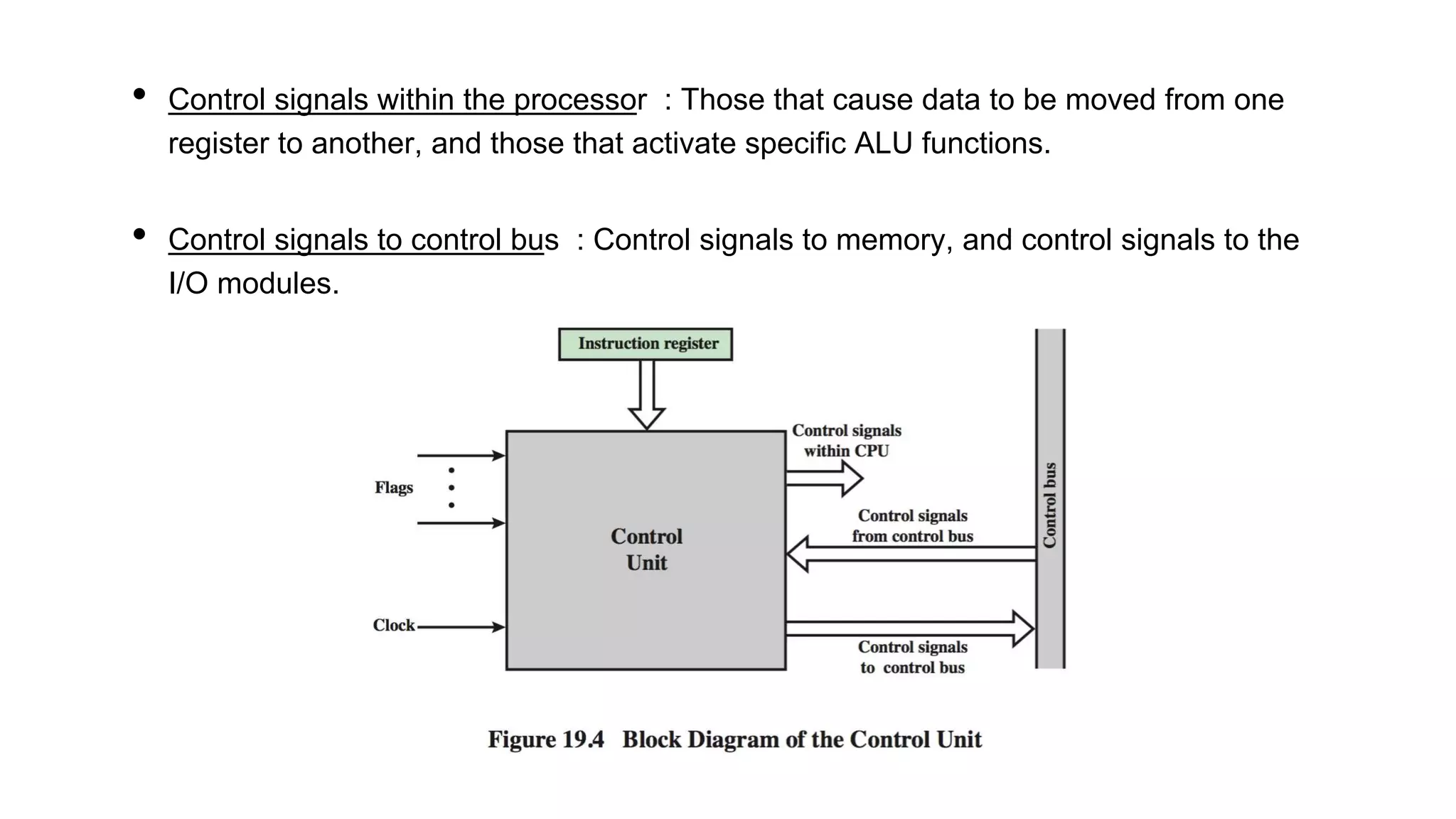

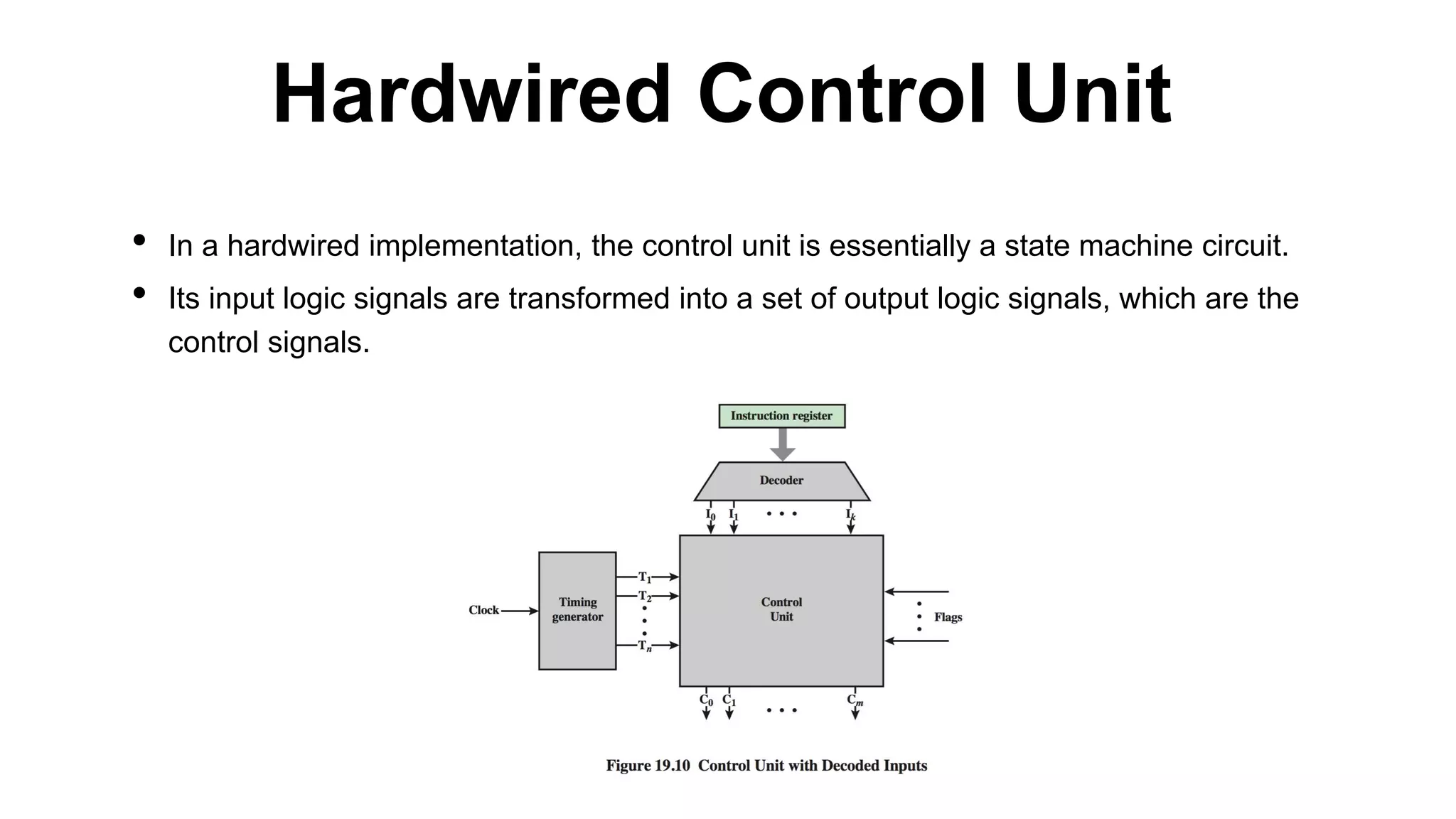

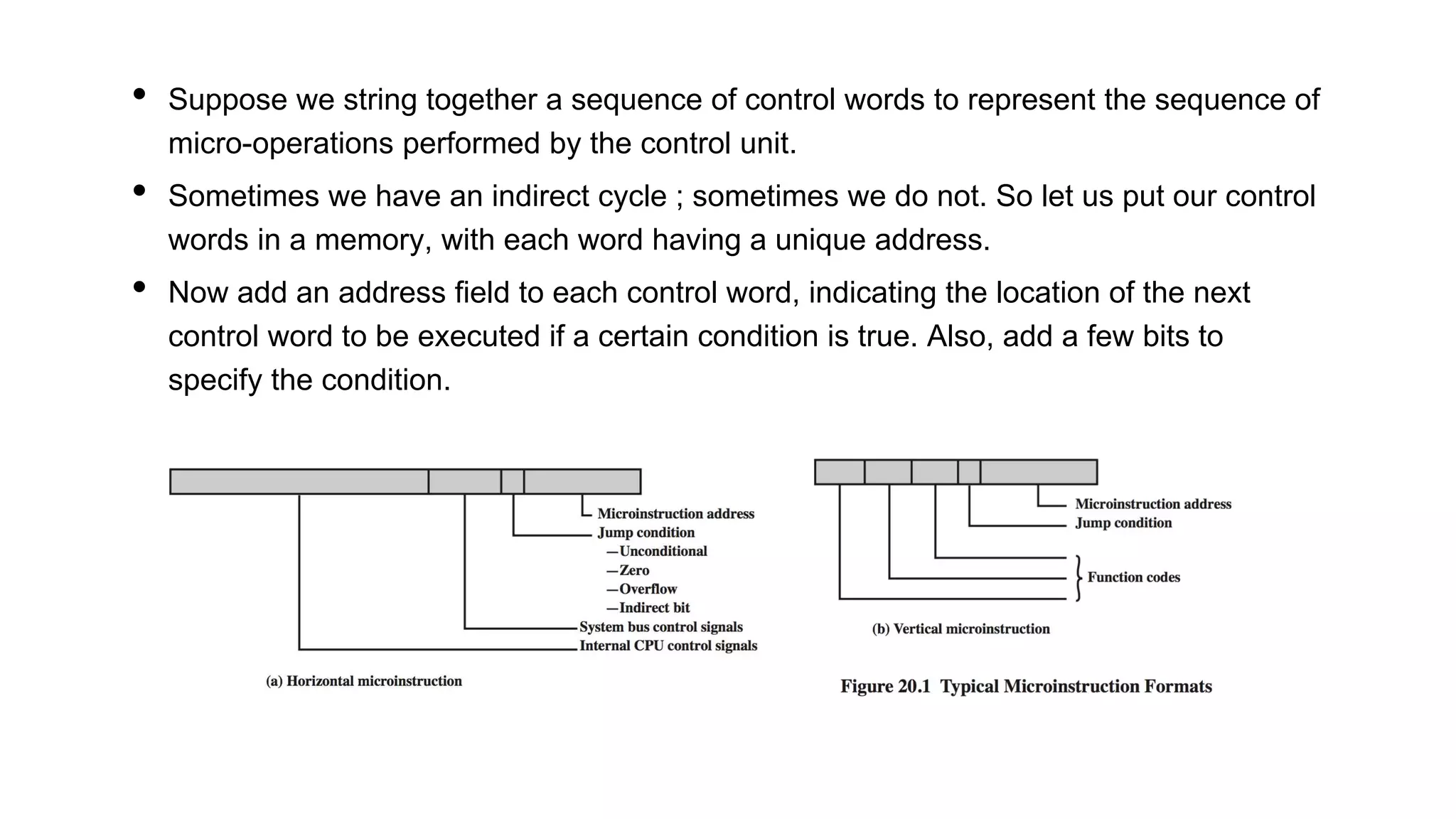

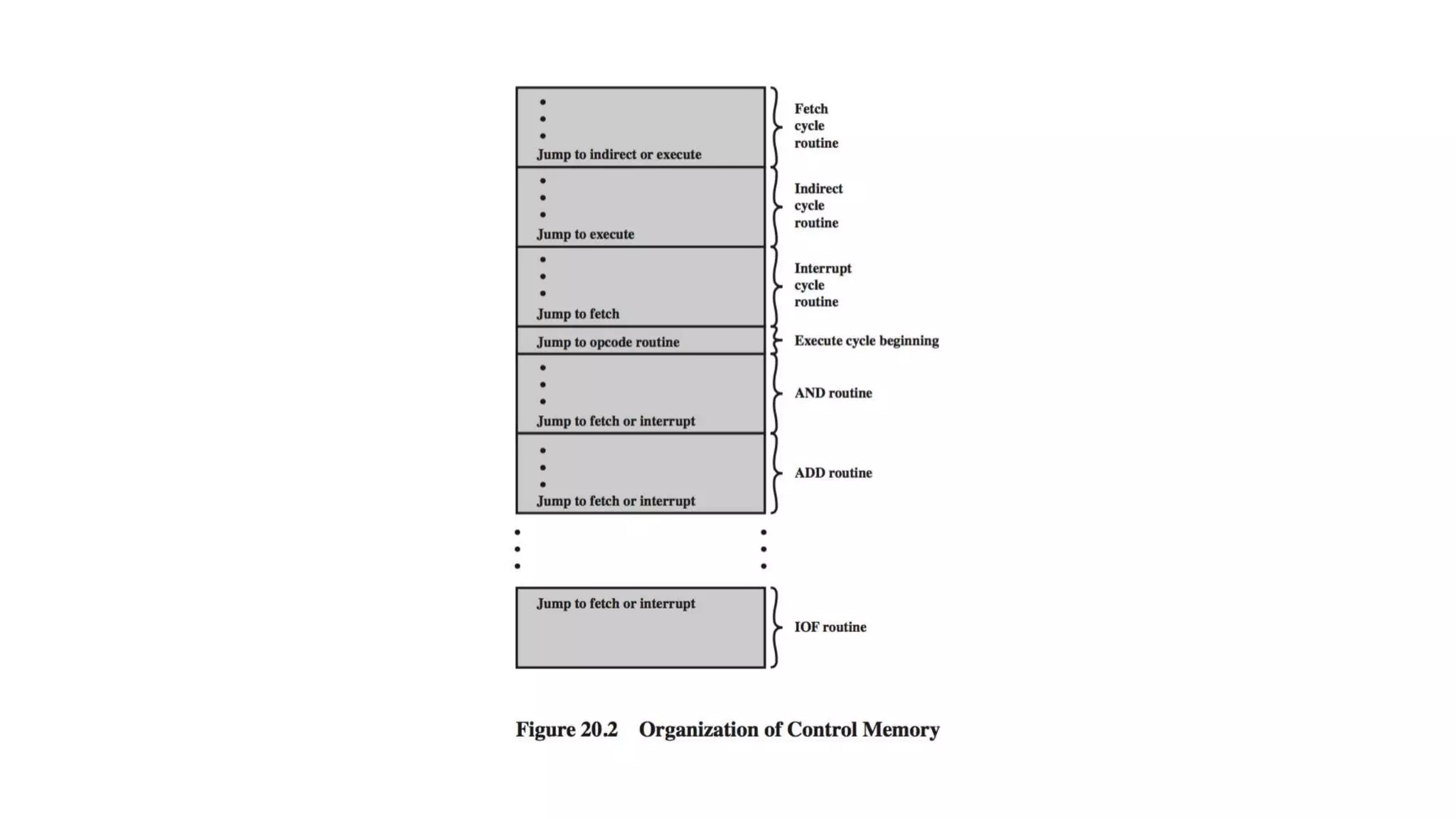

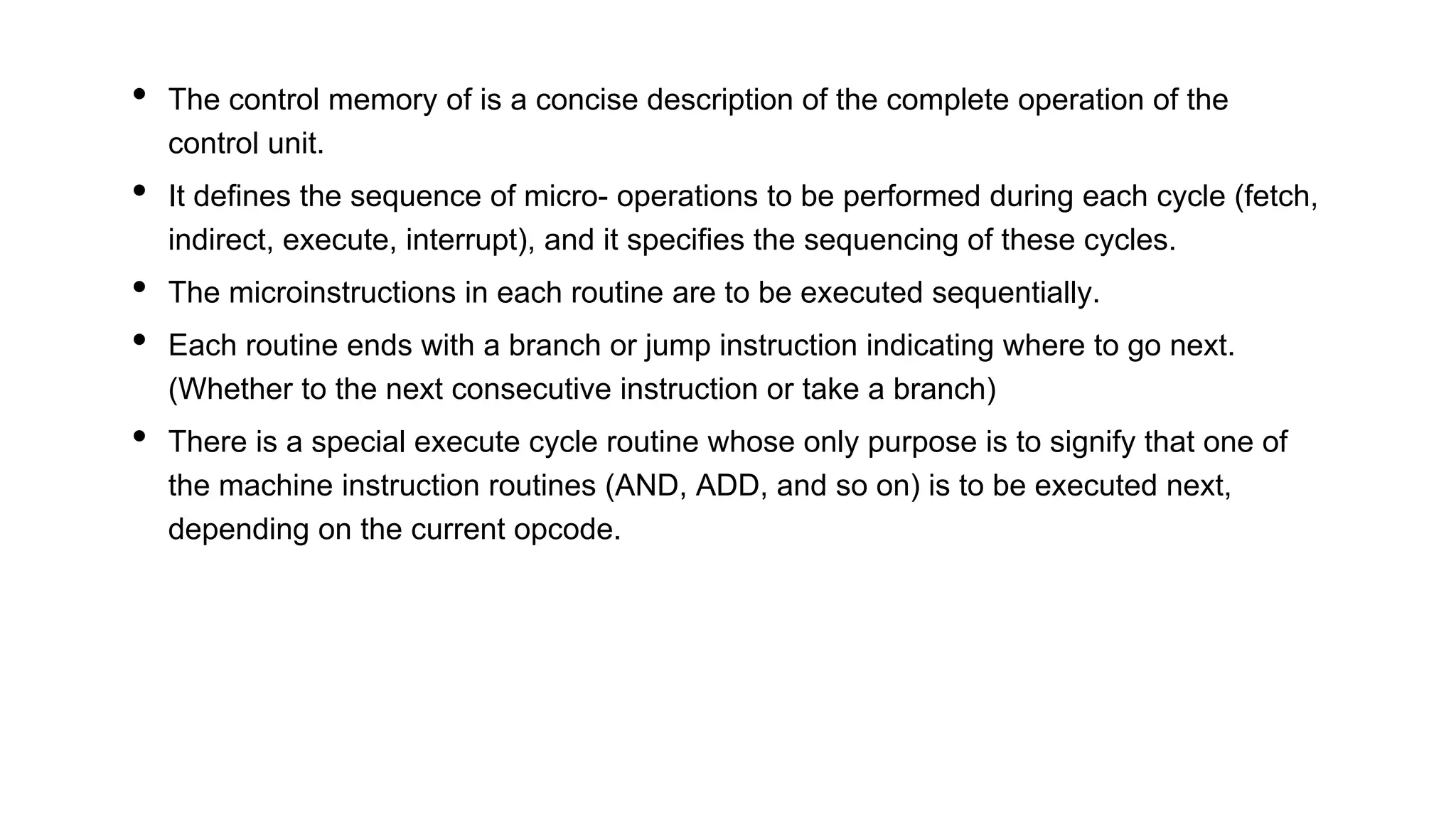

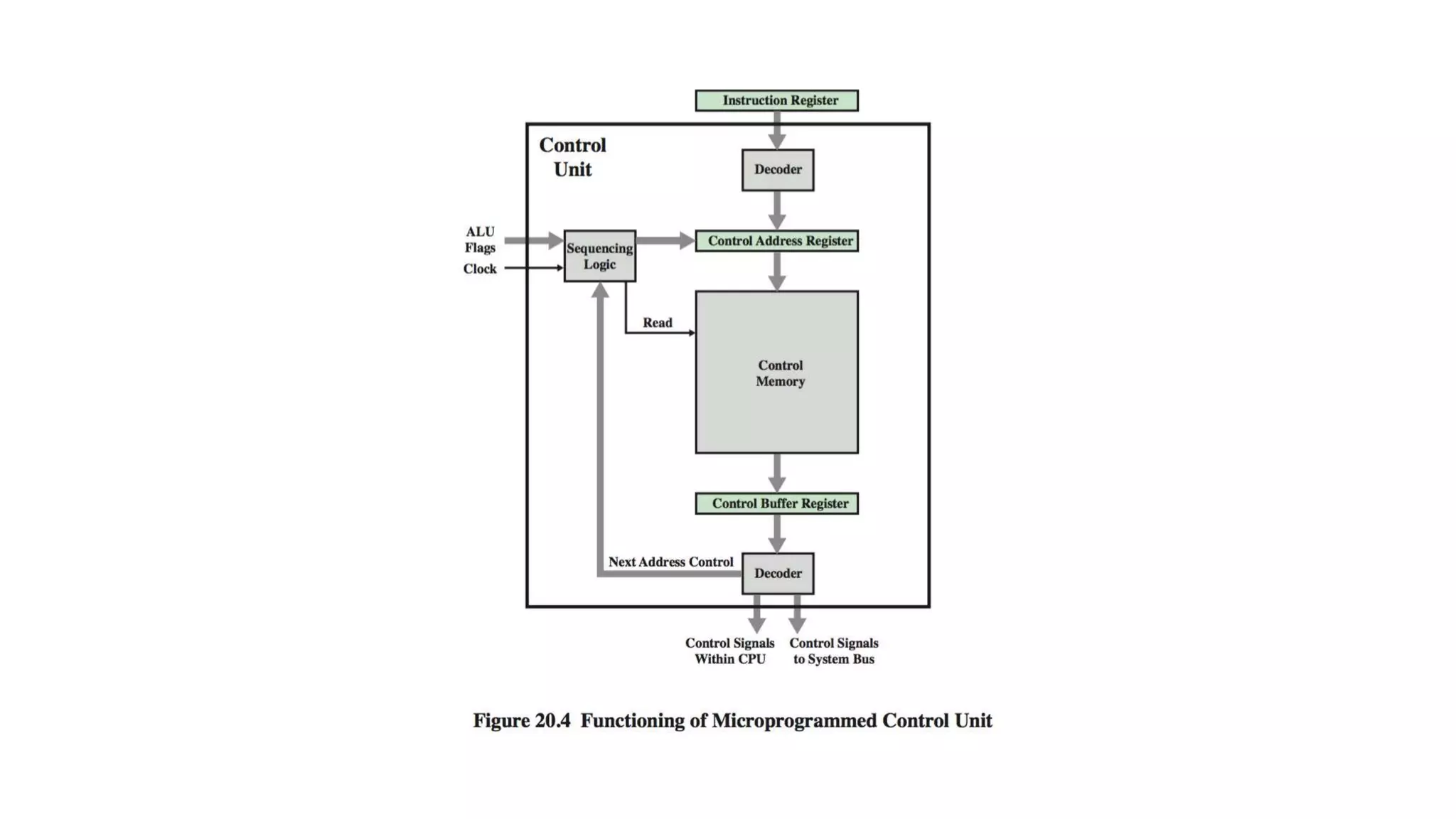

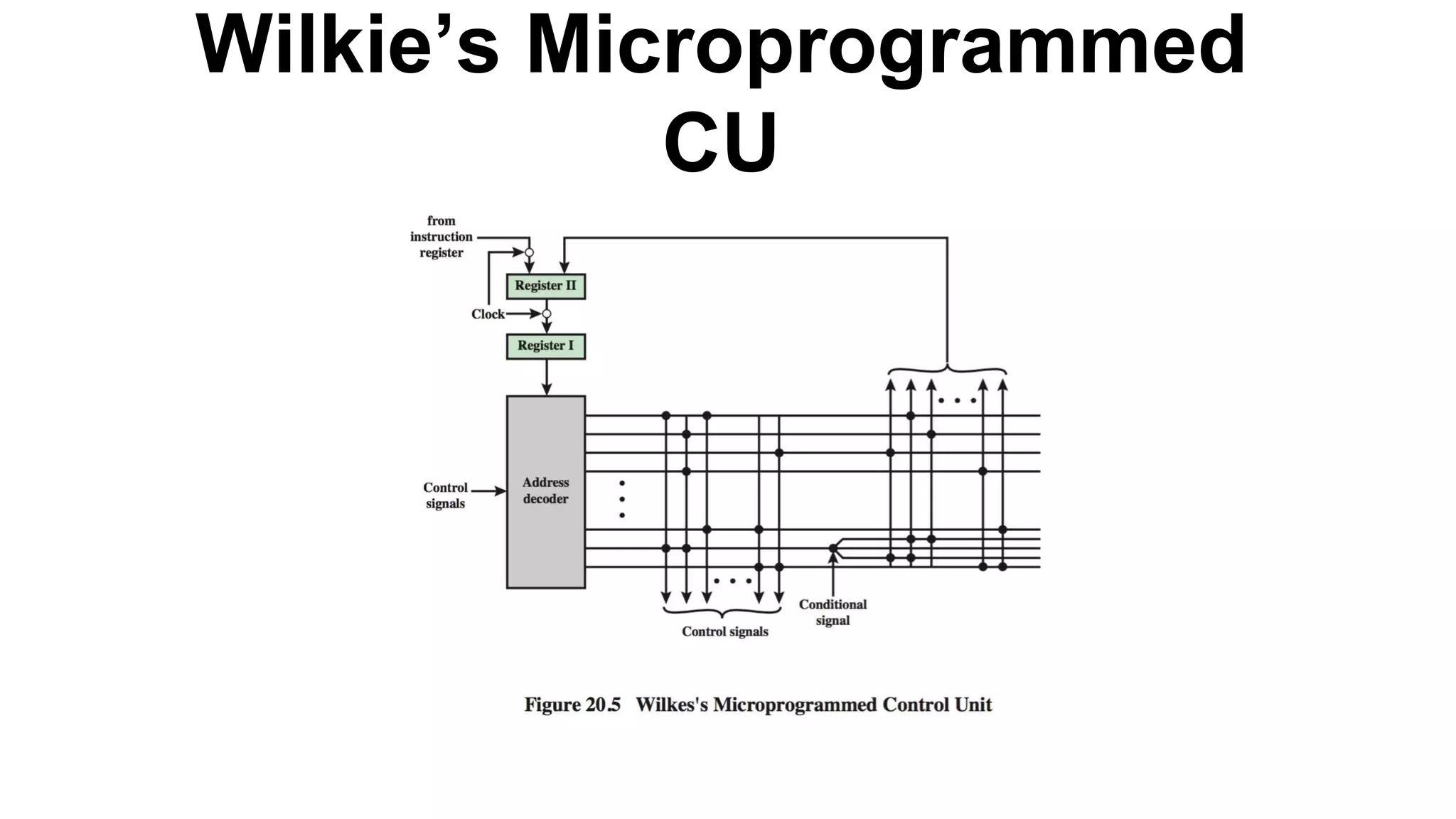

The document details the operation of a control unit in a computer system, outlining the steps involved in instruction fetching, execution, and handling interrupts through various cycles. It contrasts hardwired and microprogrammed control units, highlighting the advantages of speed and power efficiency in hardwired units against their inflexibility, while microprogrammed units are easier to design but typically slower. The document also describes the roles of the instruction cycle code and control signals in managing the sequencing of operations within the processor.