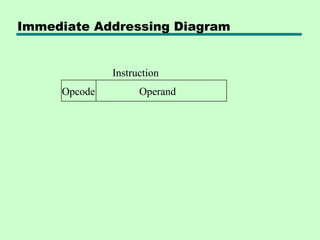

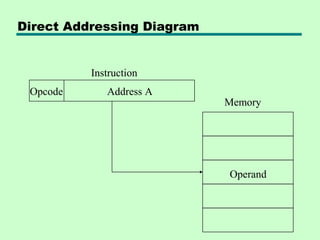

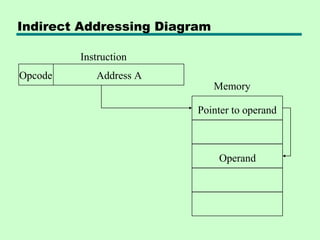

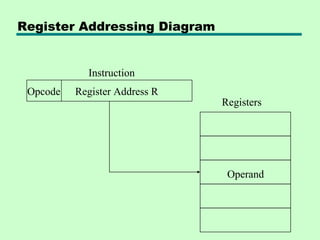

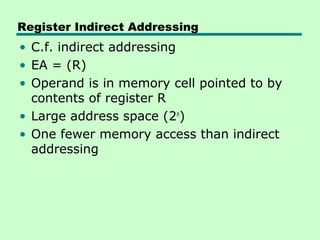

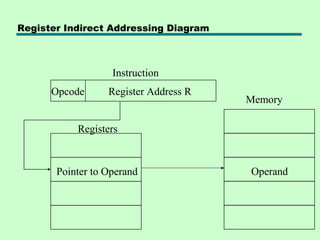

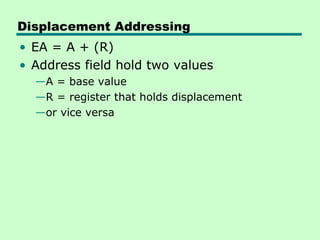

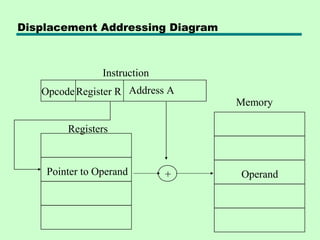

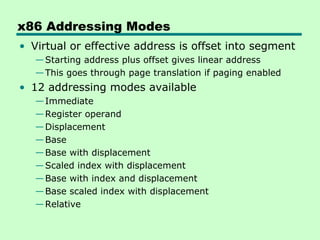

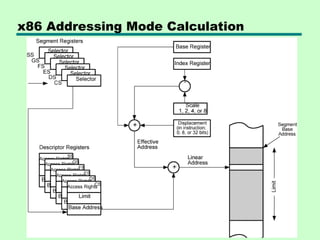

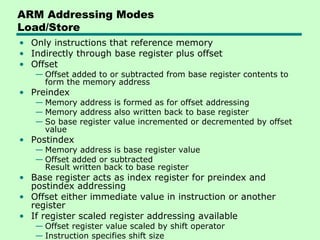

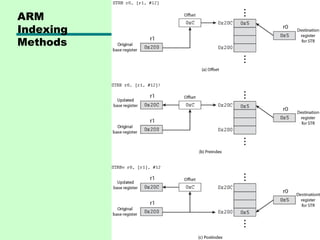

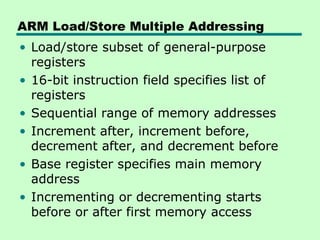

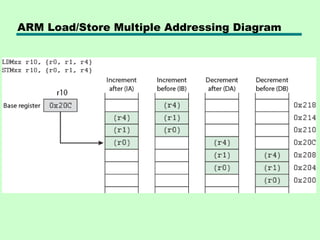

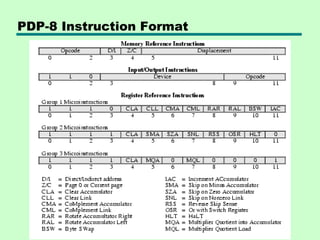

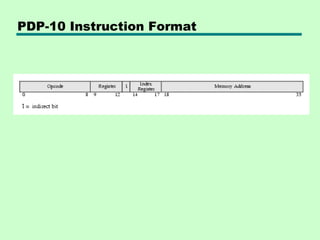

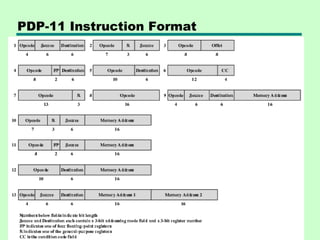

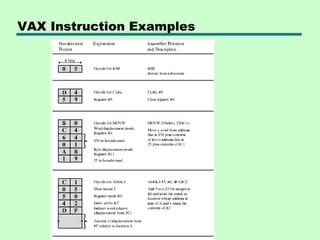

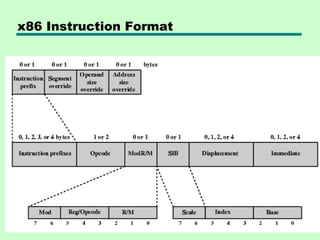

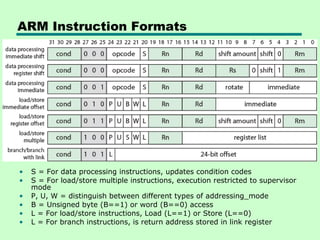

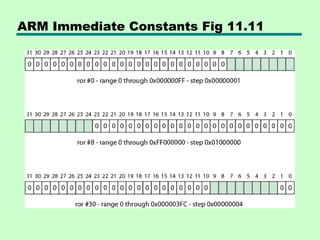

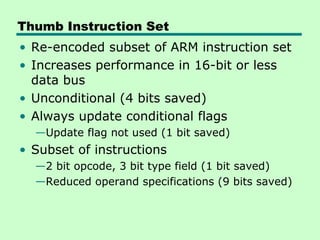

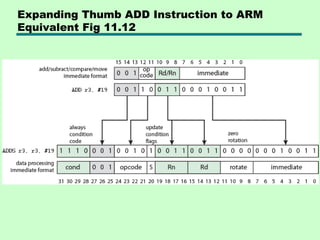

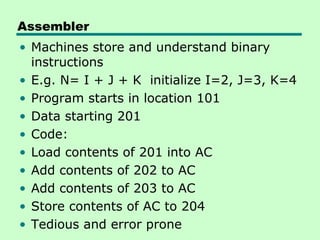

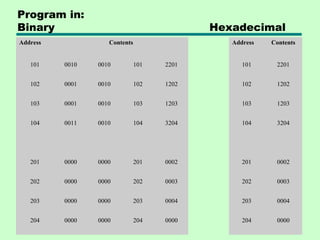

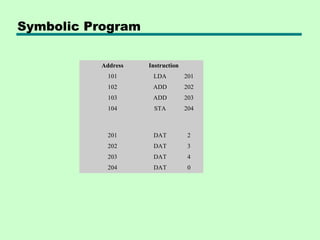

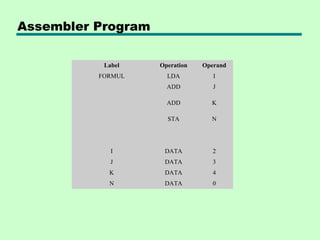

This chapter discusses instruction sets and addressing modes. It covers common addressing modes like immediate, direct, indirect, register, register indirect, displacement, and stack addressing. It provides examples and diagrams to illustrate each addressing mode. The chapter also discusses instruction formats for different architectures like PDP-8, PDP-10, PDP-11, VAX, x86, and ARM. It covers ARM's load/store multiple addressing and thumb instruction set. The chapter concludes with an overview of assemblers and a simple example program.