Embed presentation

Downloaded 148 times

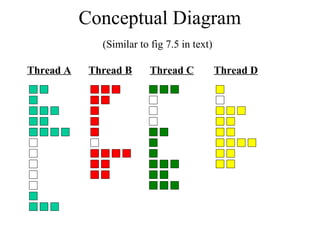

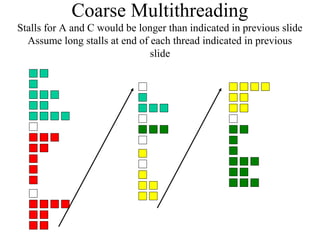

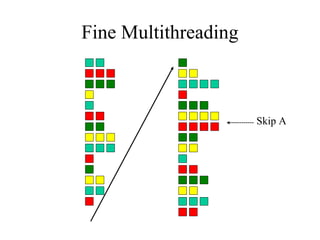

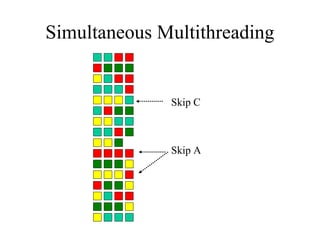

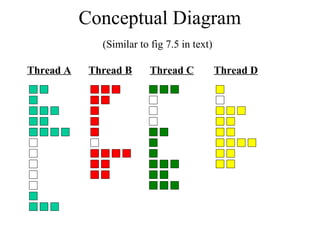

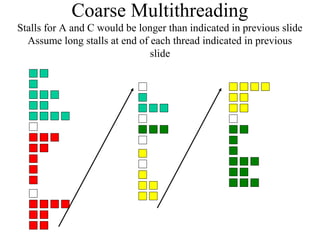

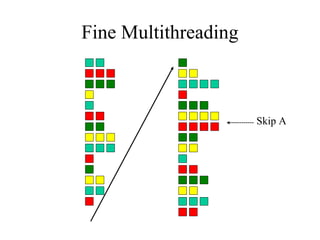

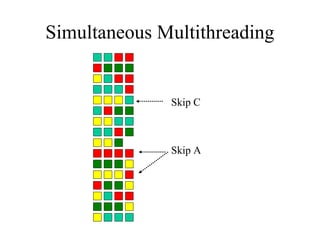

This document discusses three types of hardware multithreading: coarse-grained, fine-grained, and simultaneous multithreading (SMT). Coarse-grained multithreading allows another thread to run during long stalls of the first thread. Fine-grained multithreading interleaves instructions from multiple threads in a round-robin fashion to hide stalls. SMT issues instructions from multiple threads in the same cycle by using register renaming and dynamic scheduling to maximize utilization.