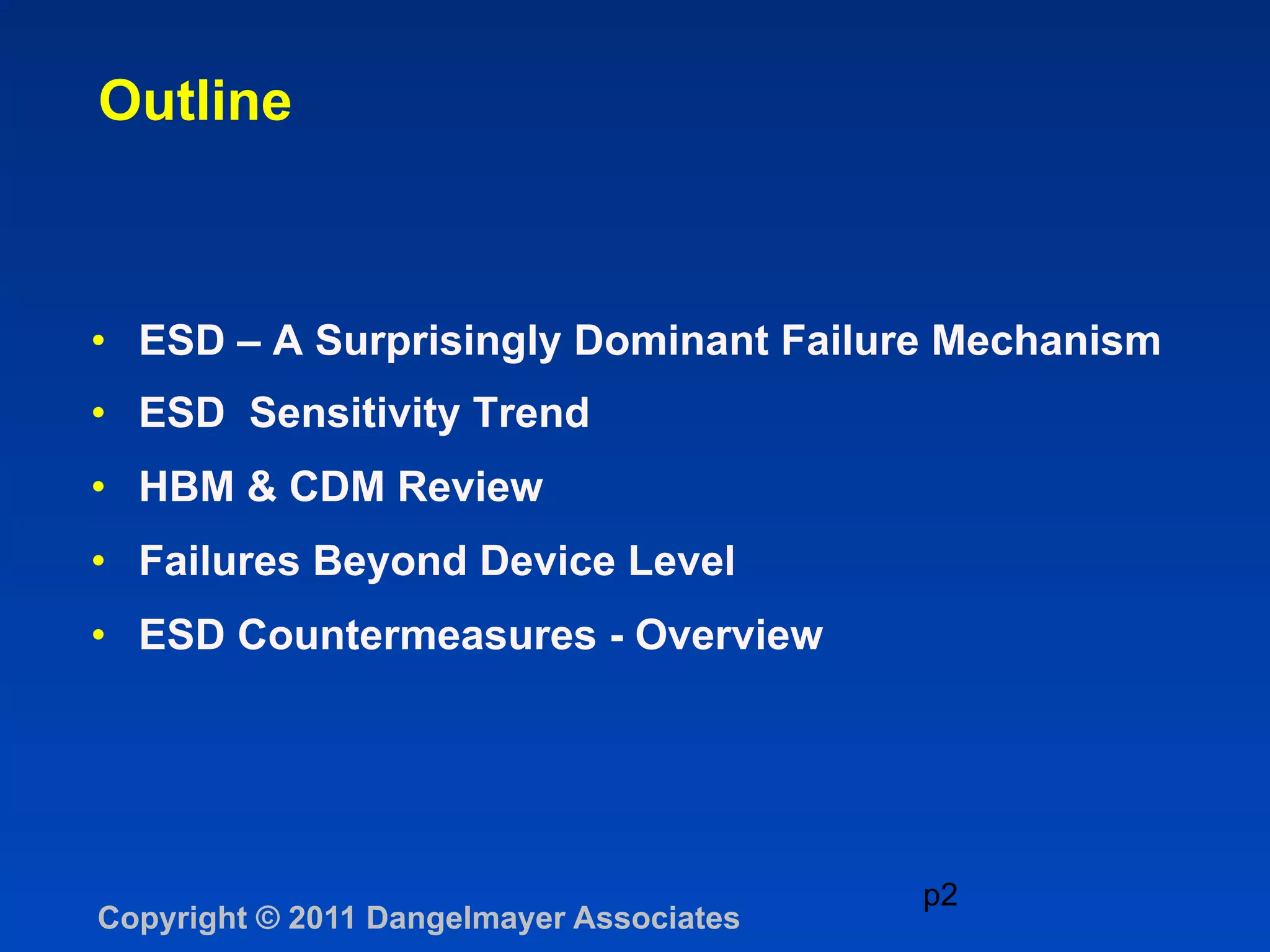

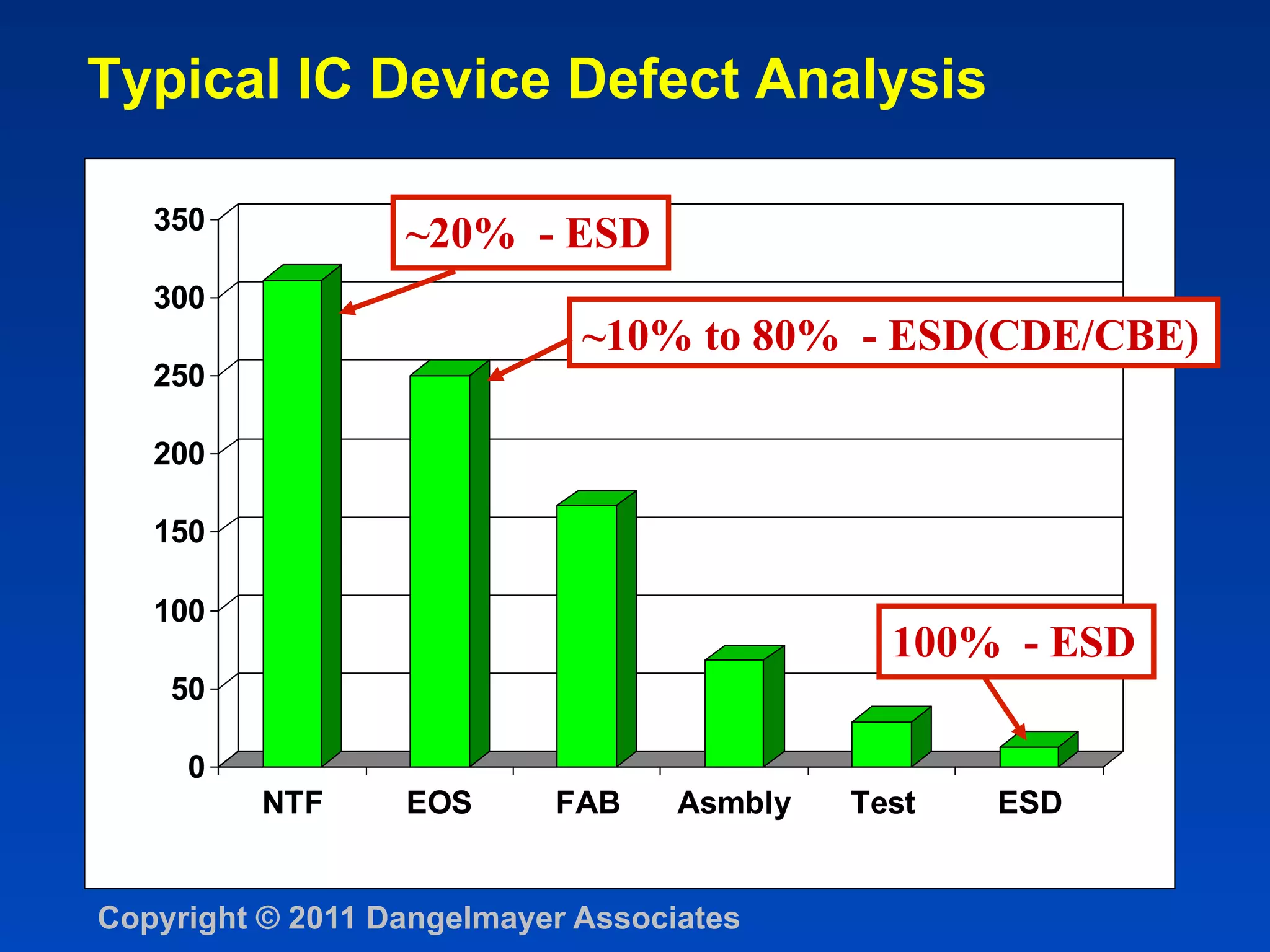

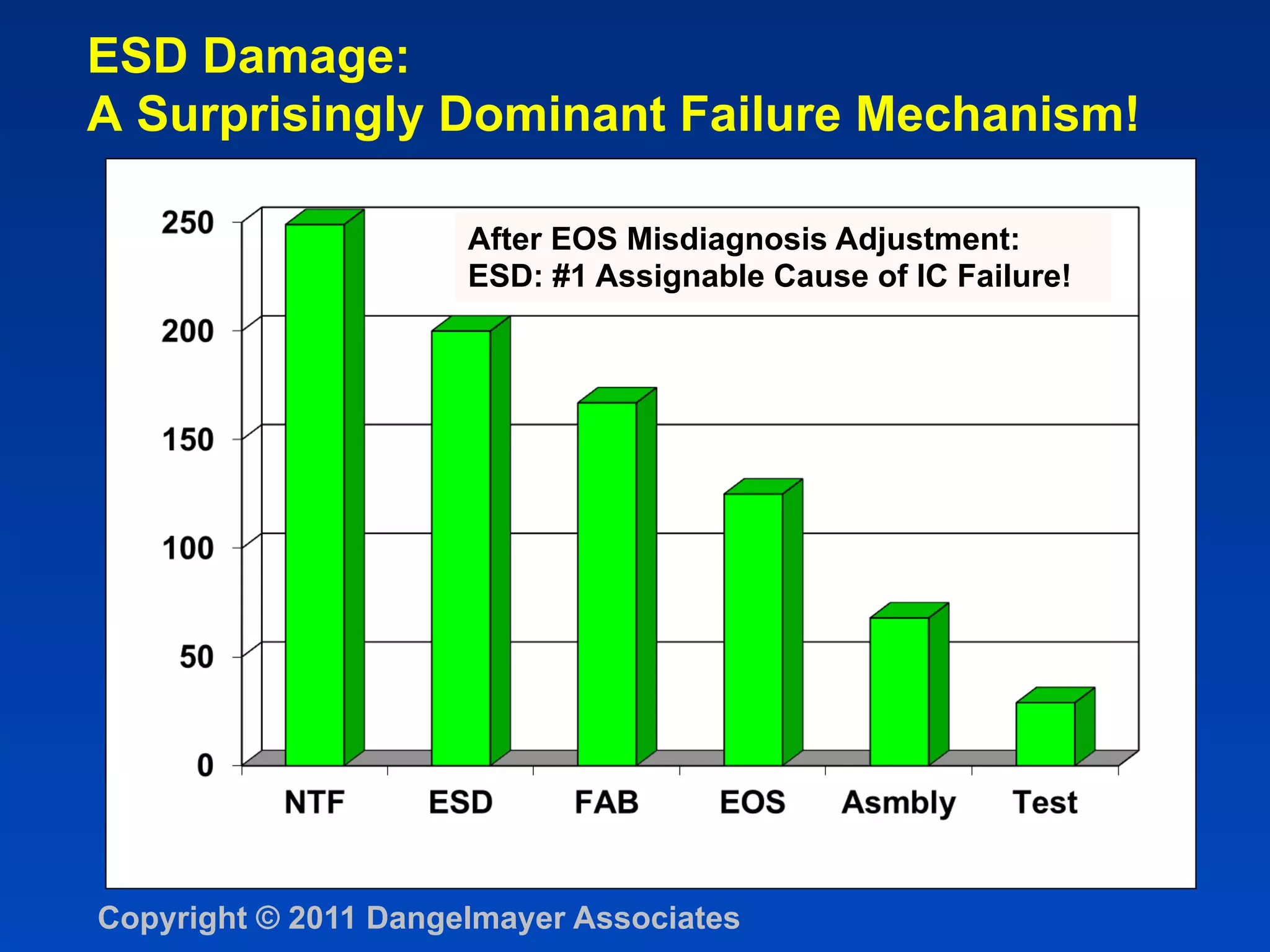

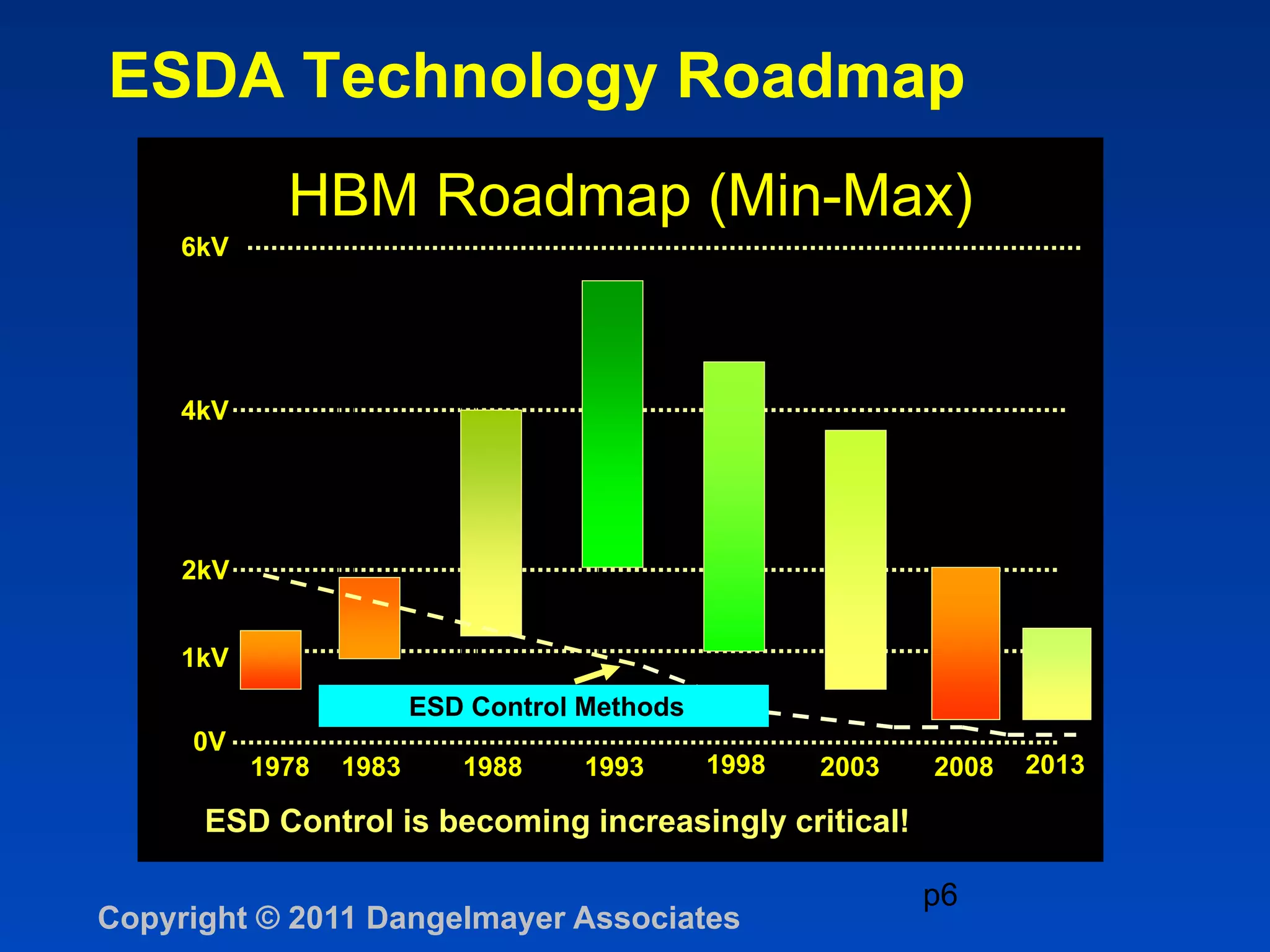

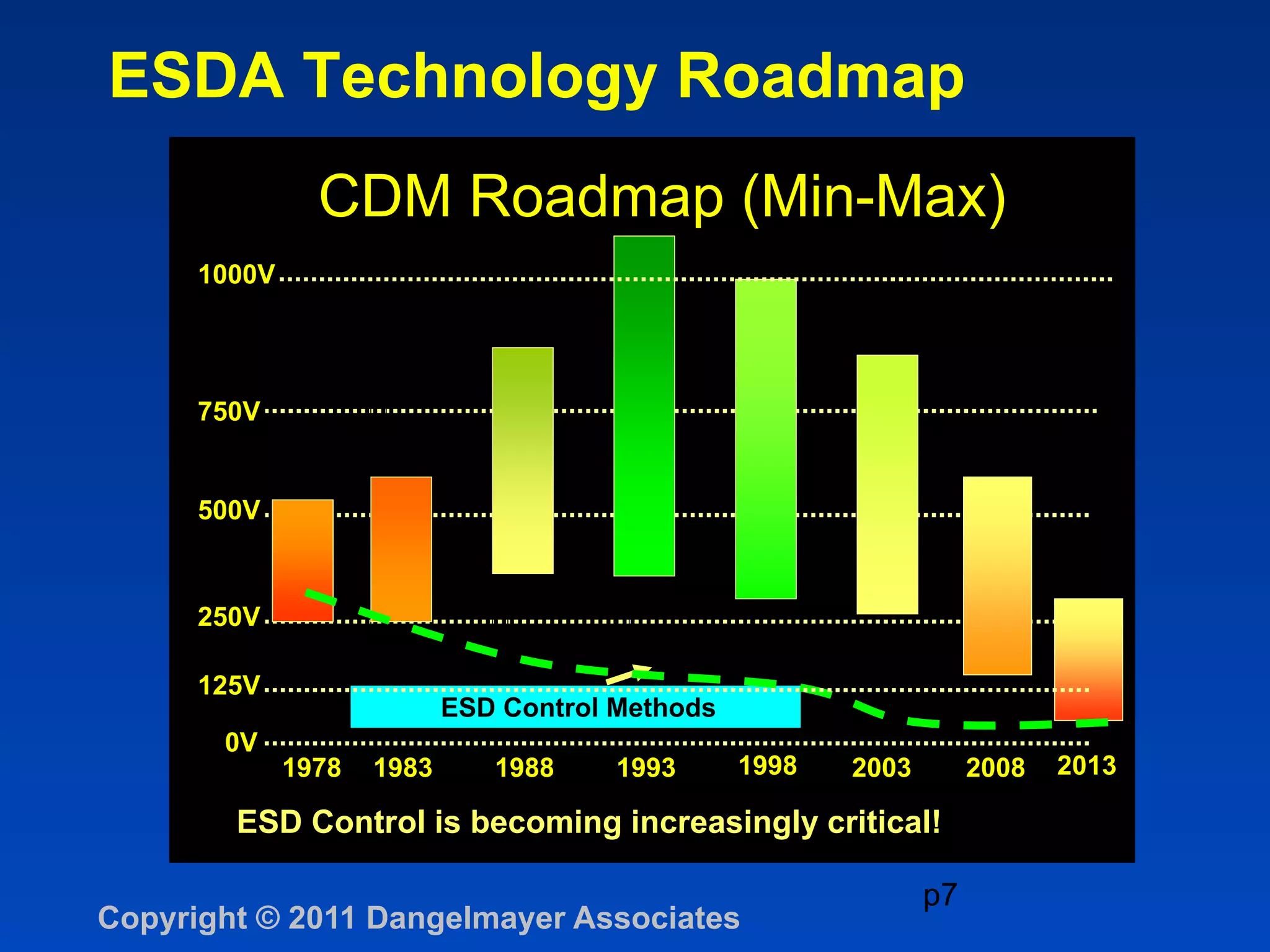

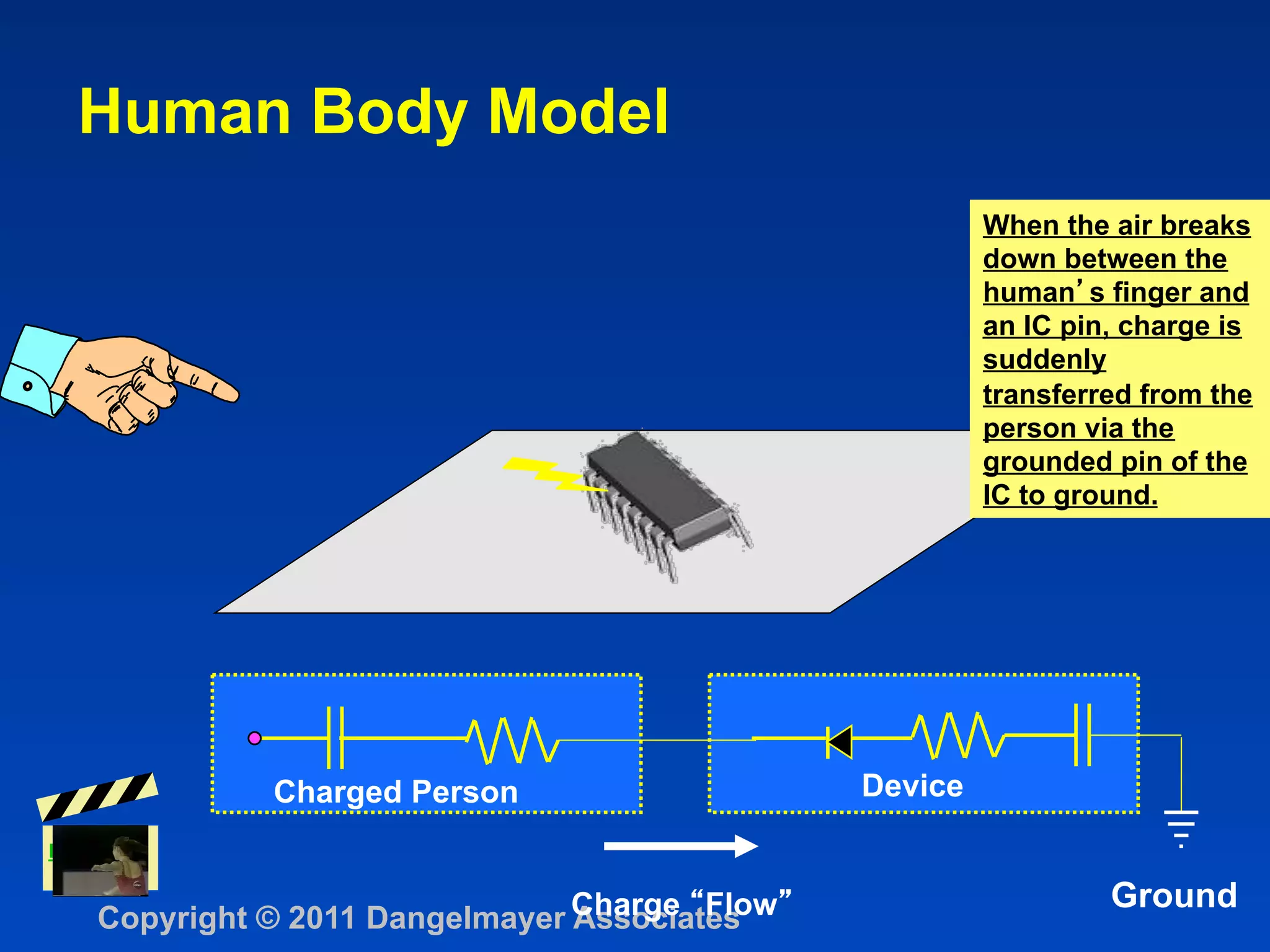

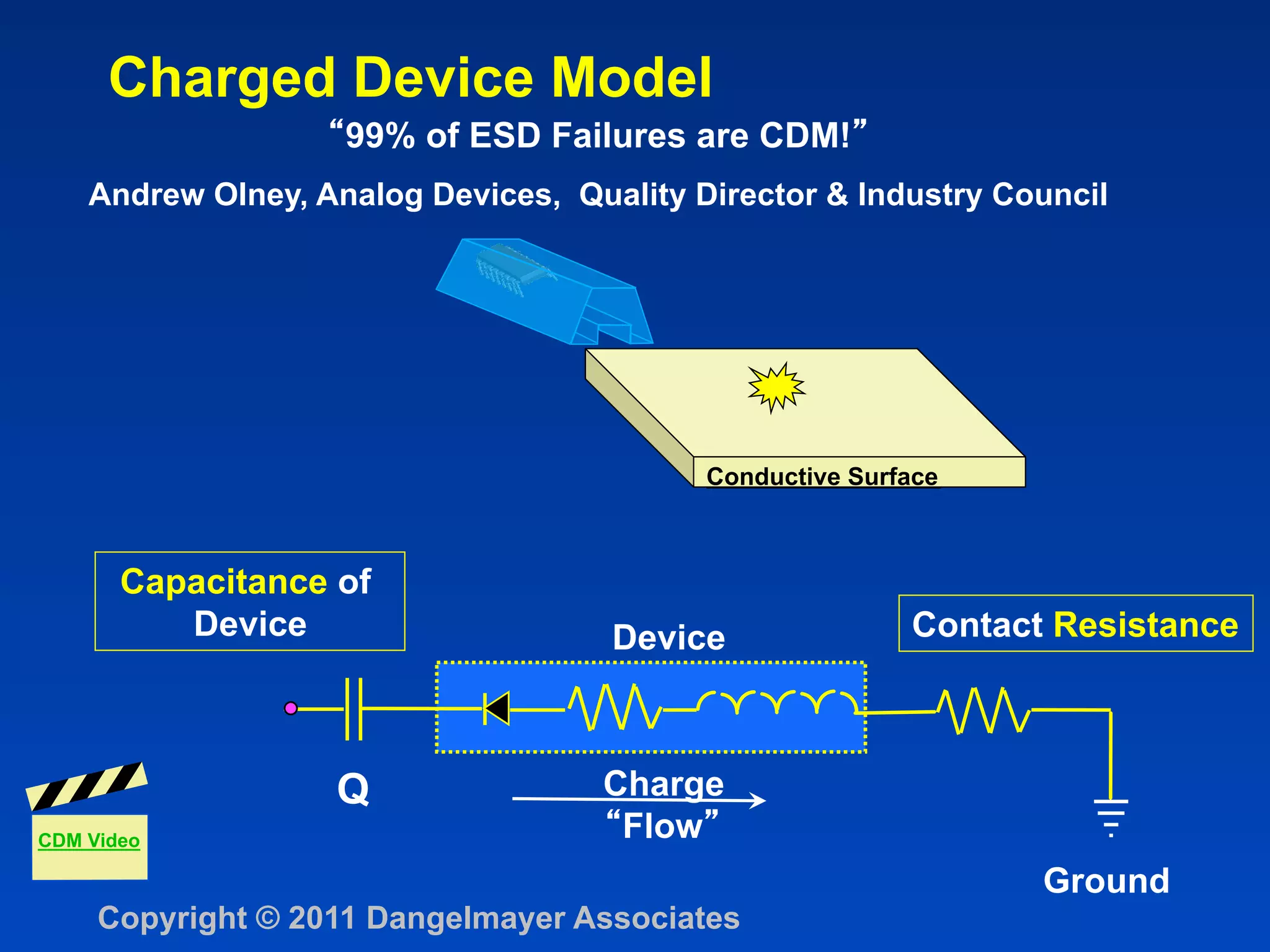

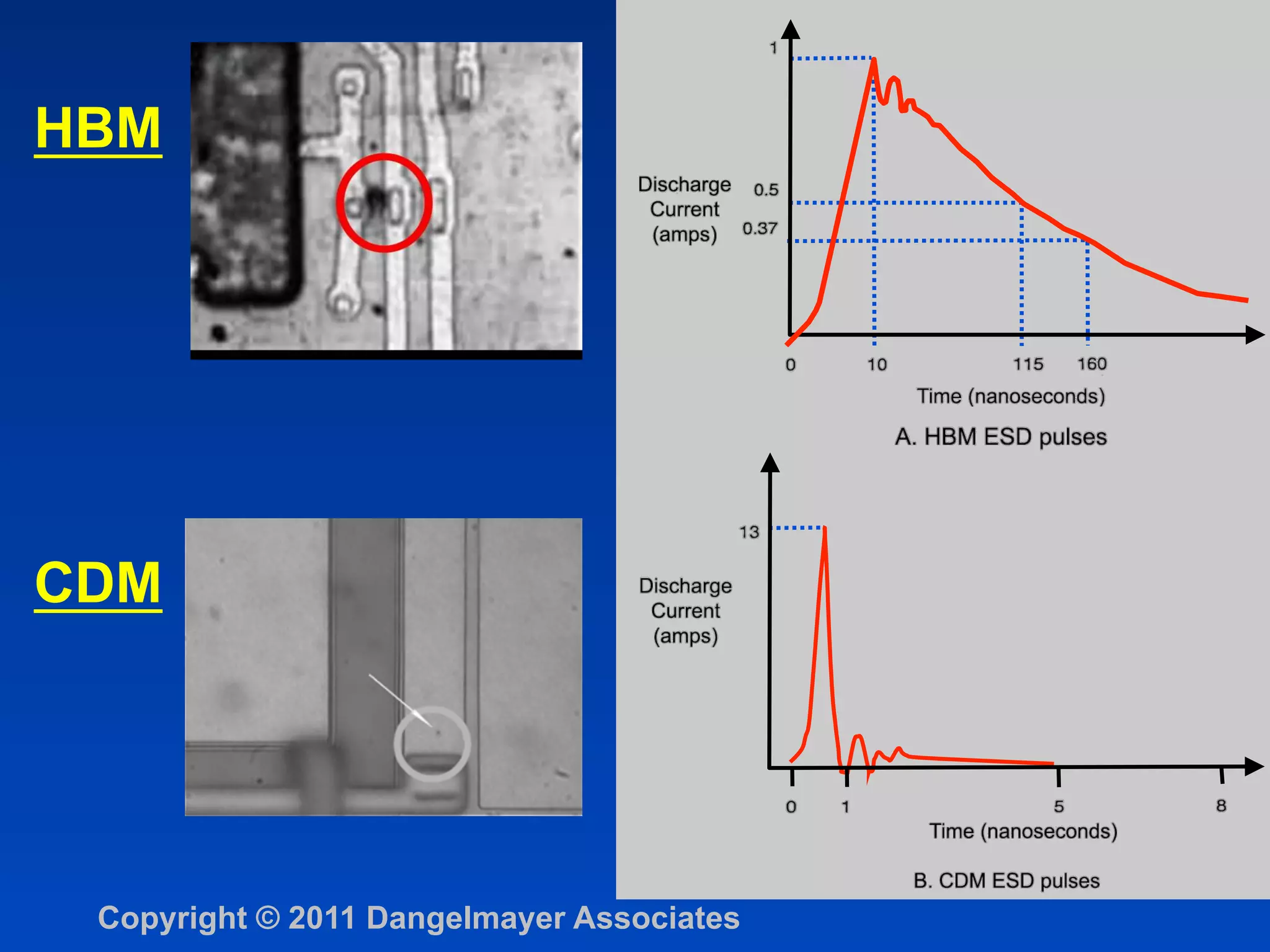

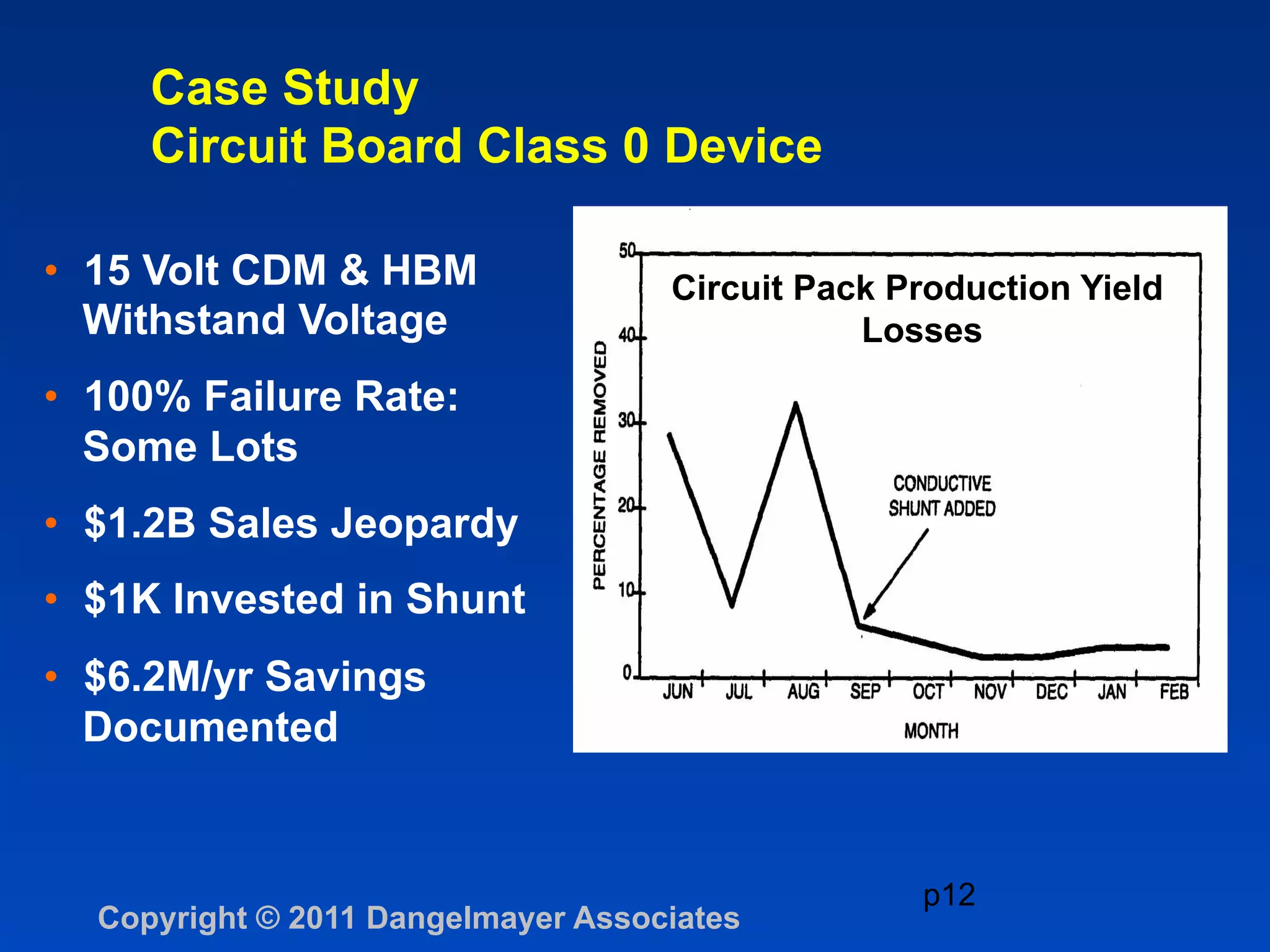

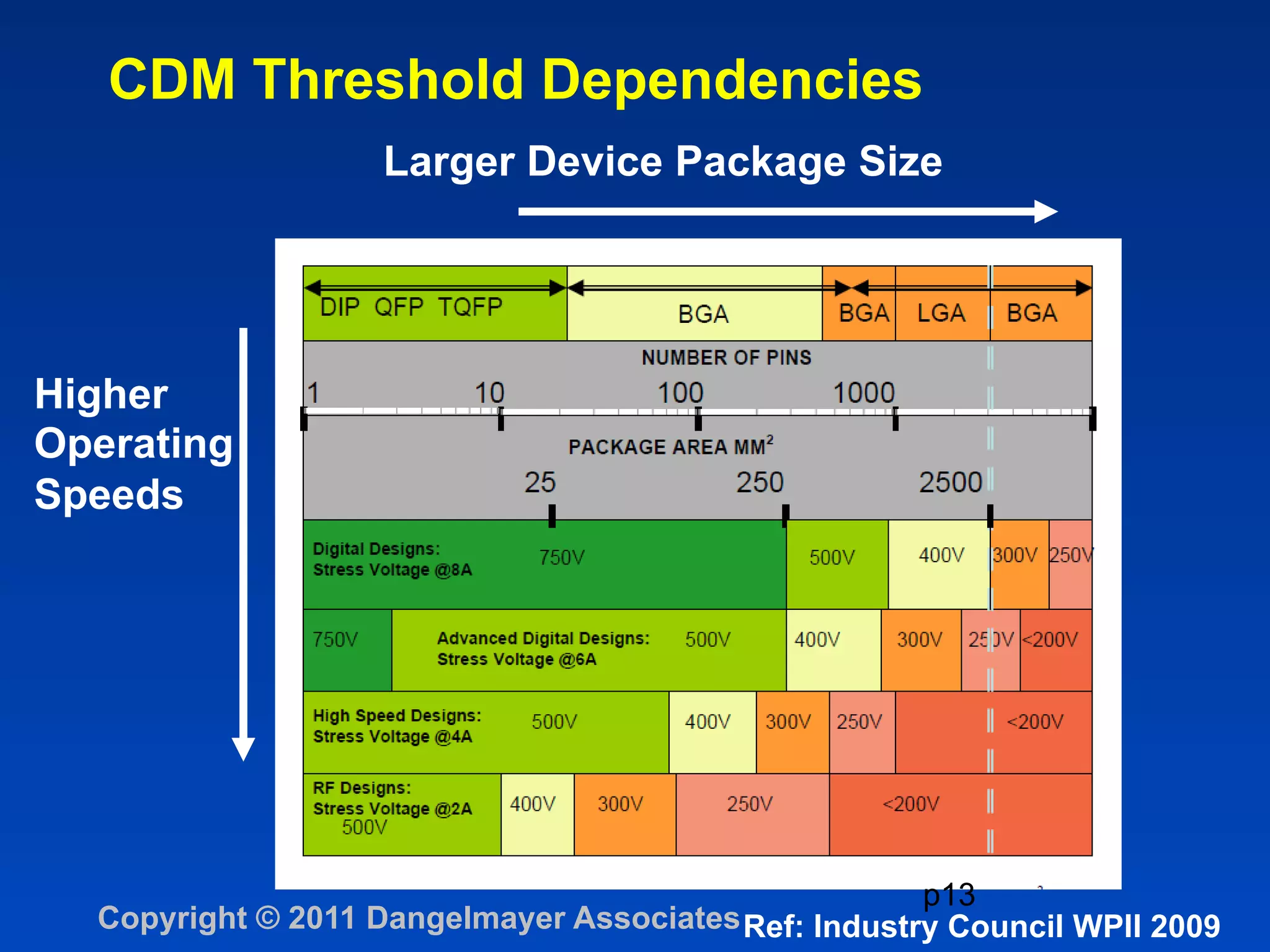

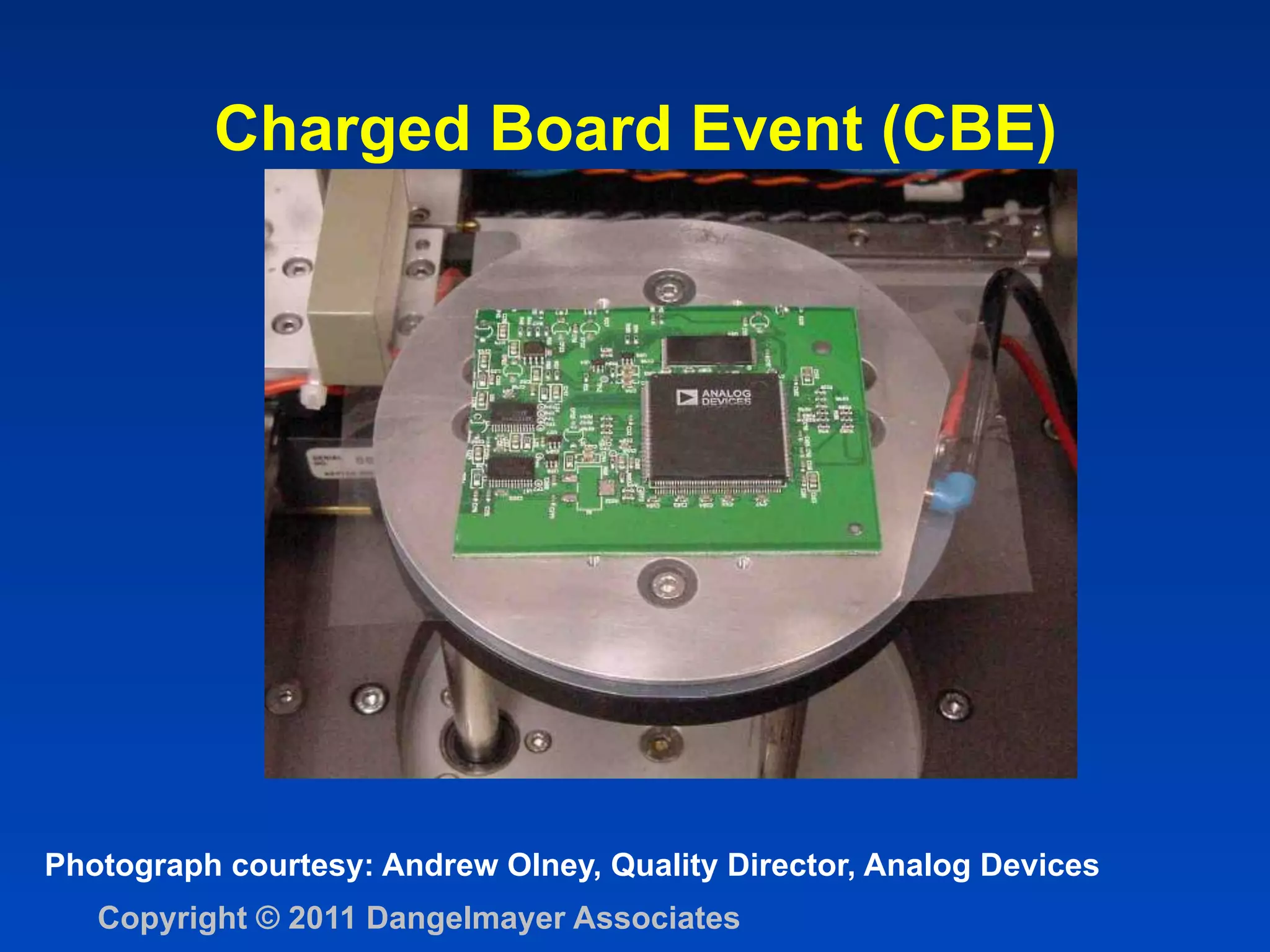

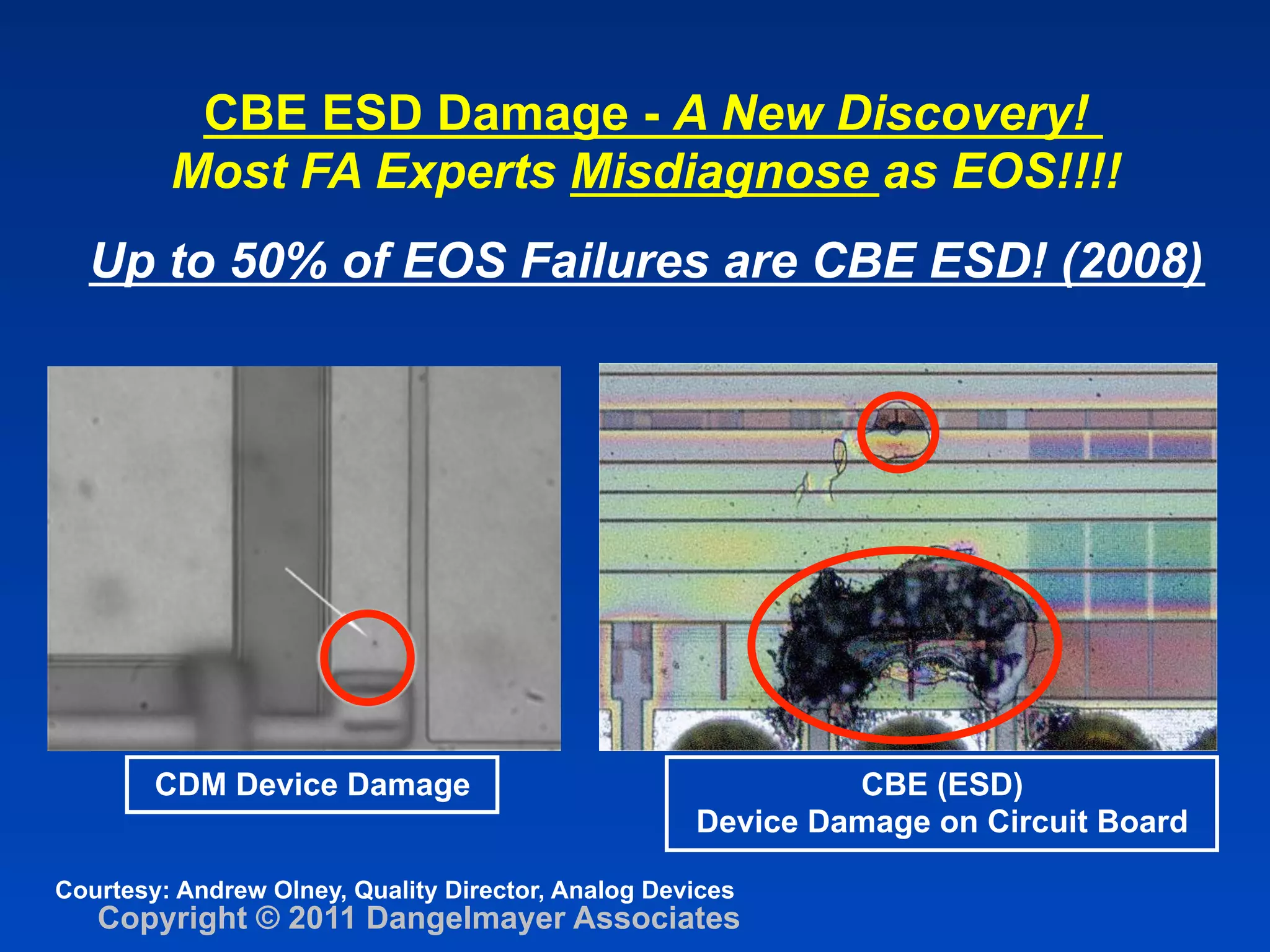

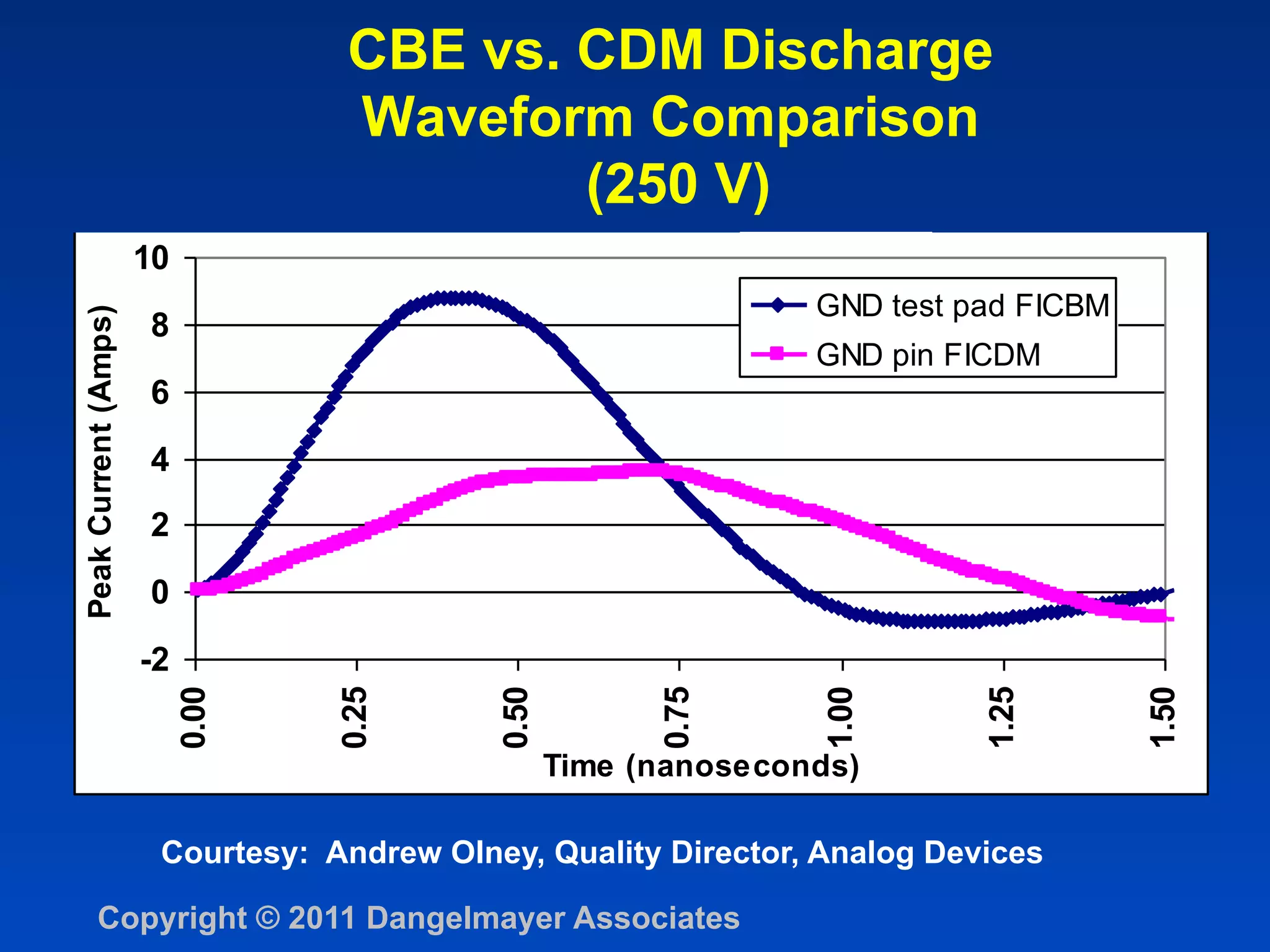

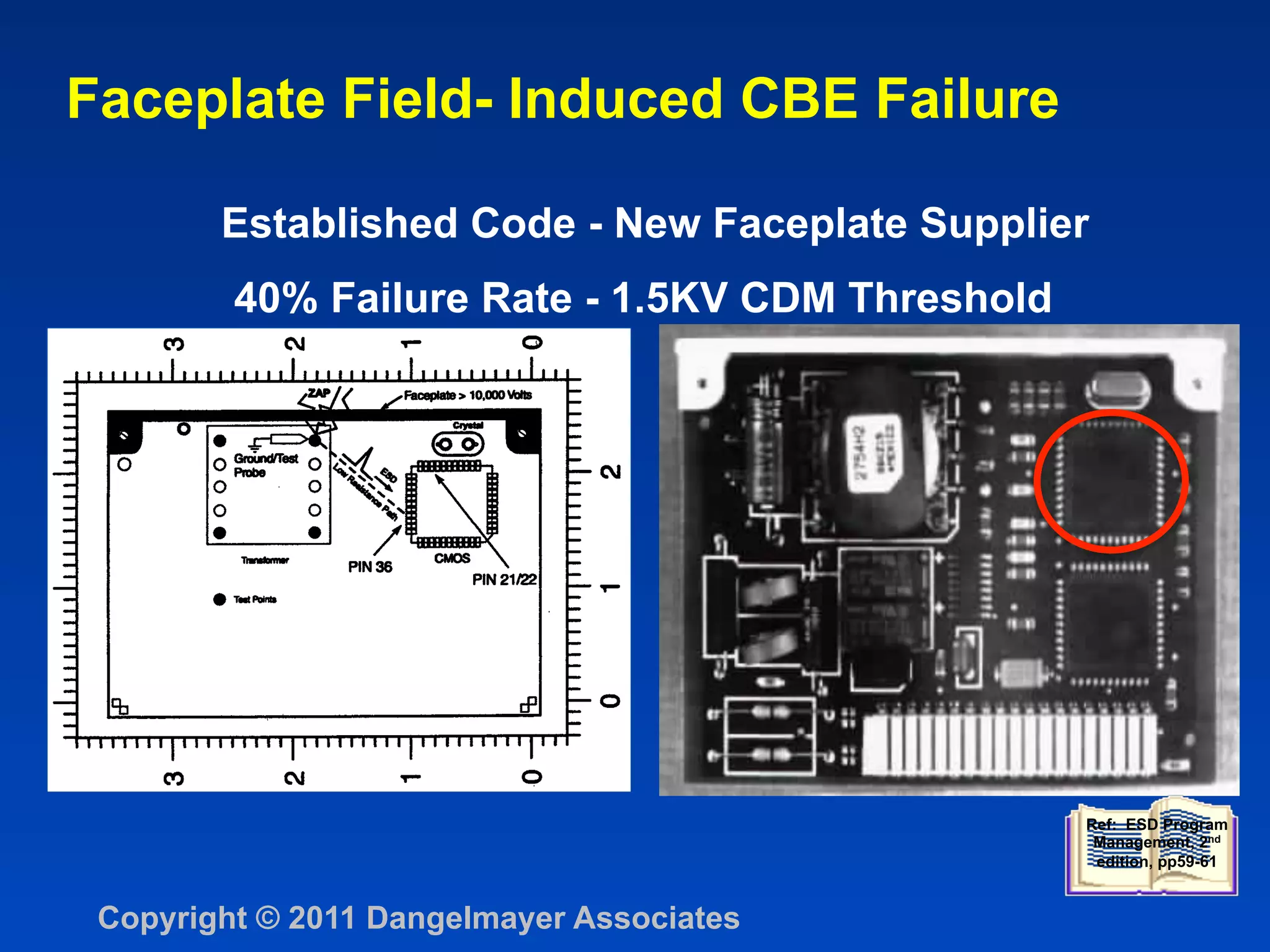

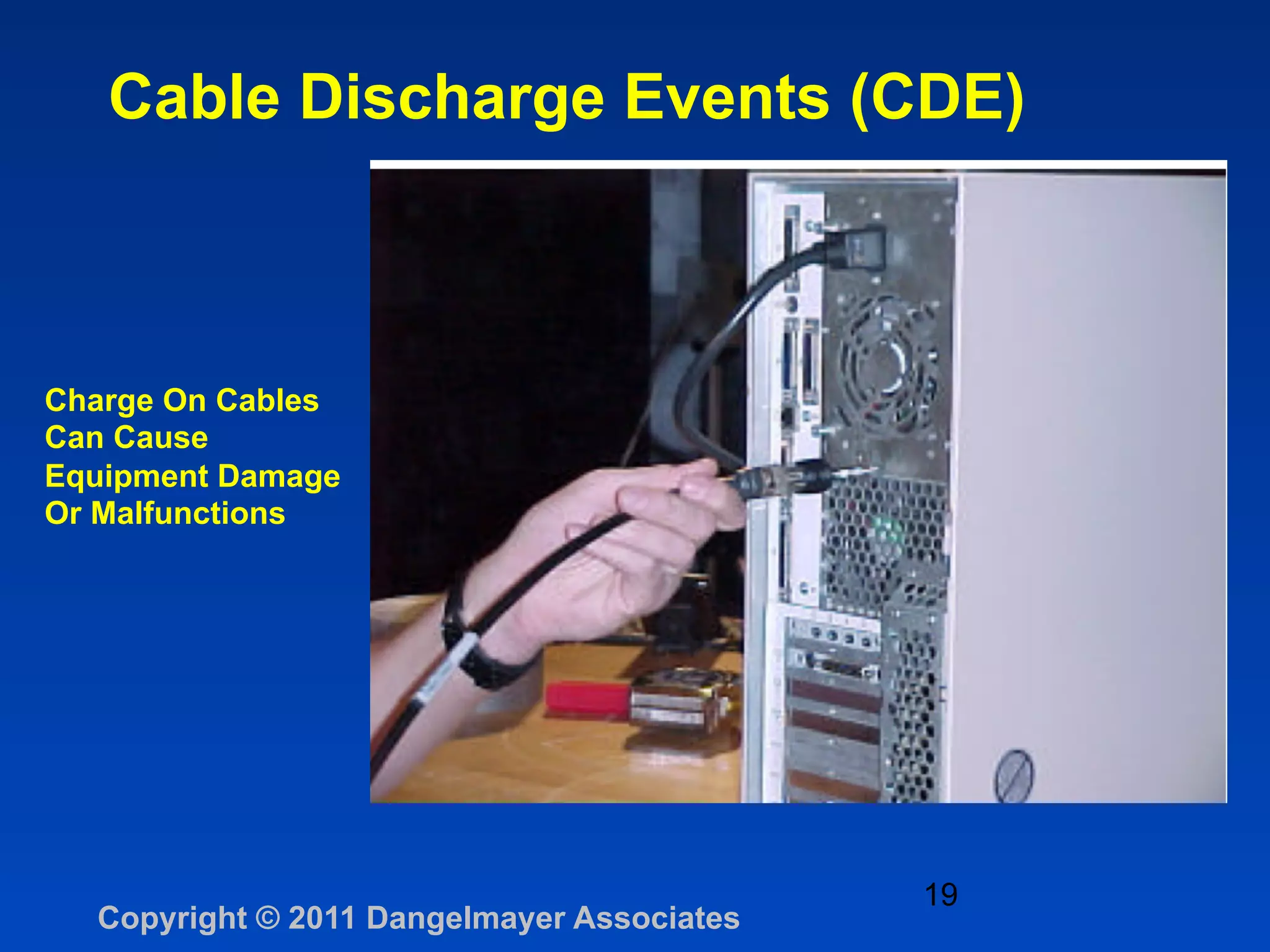

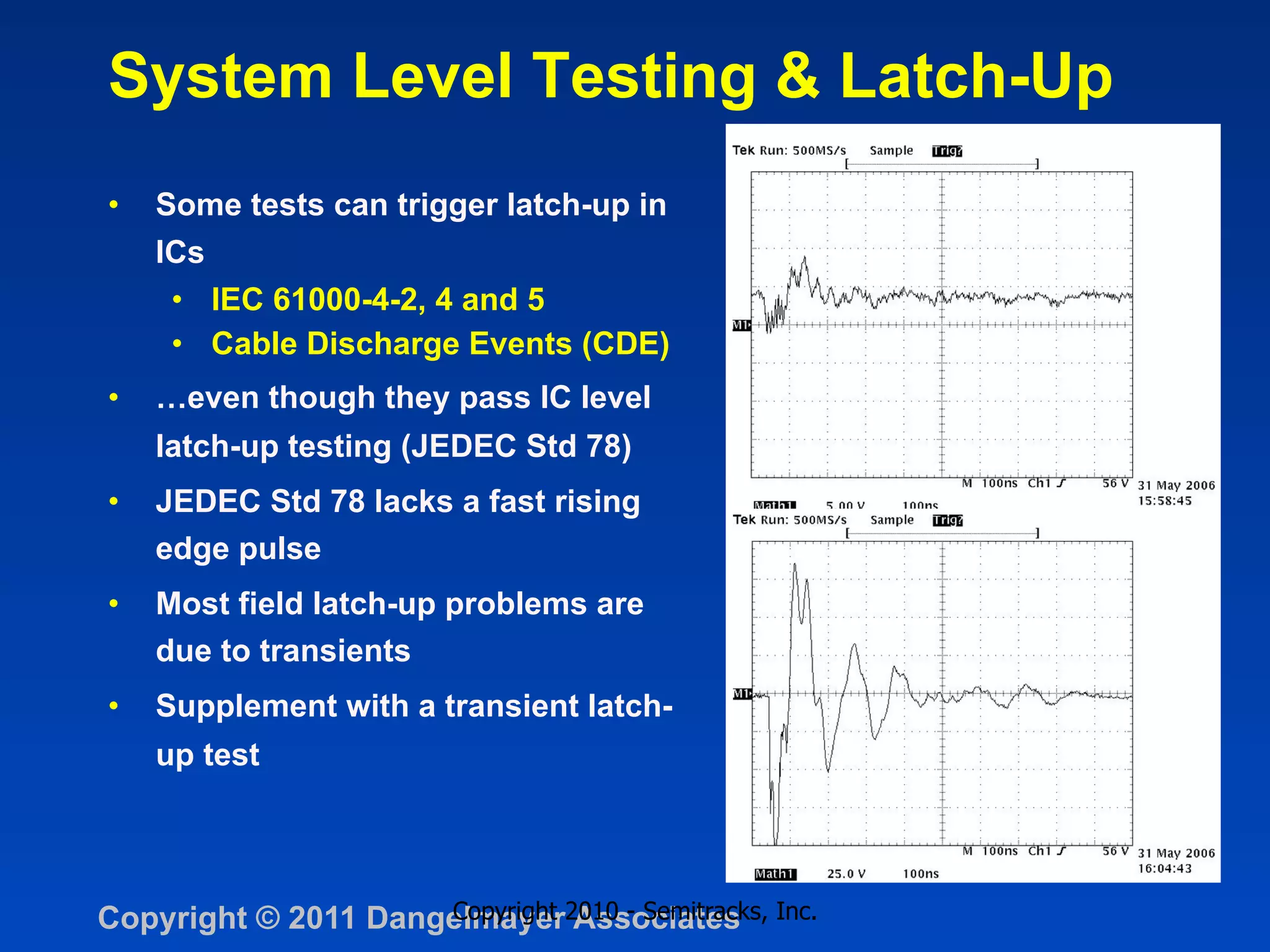

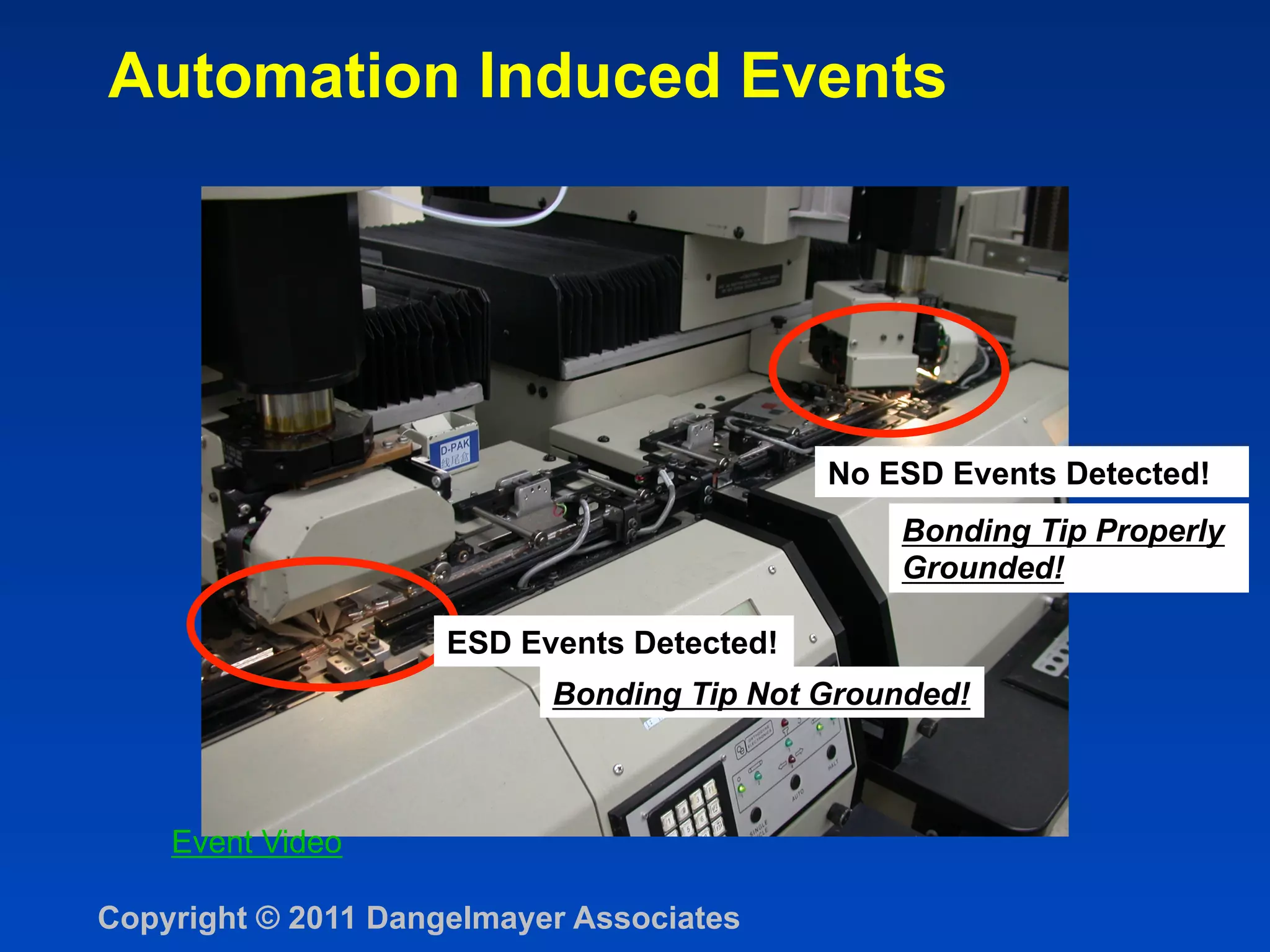

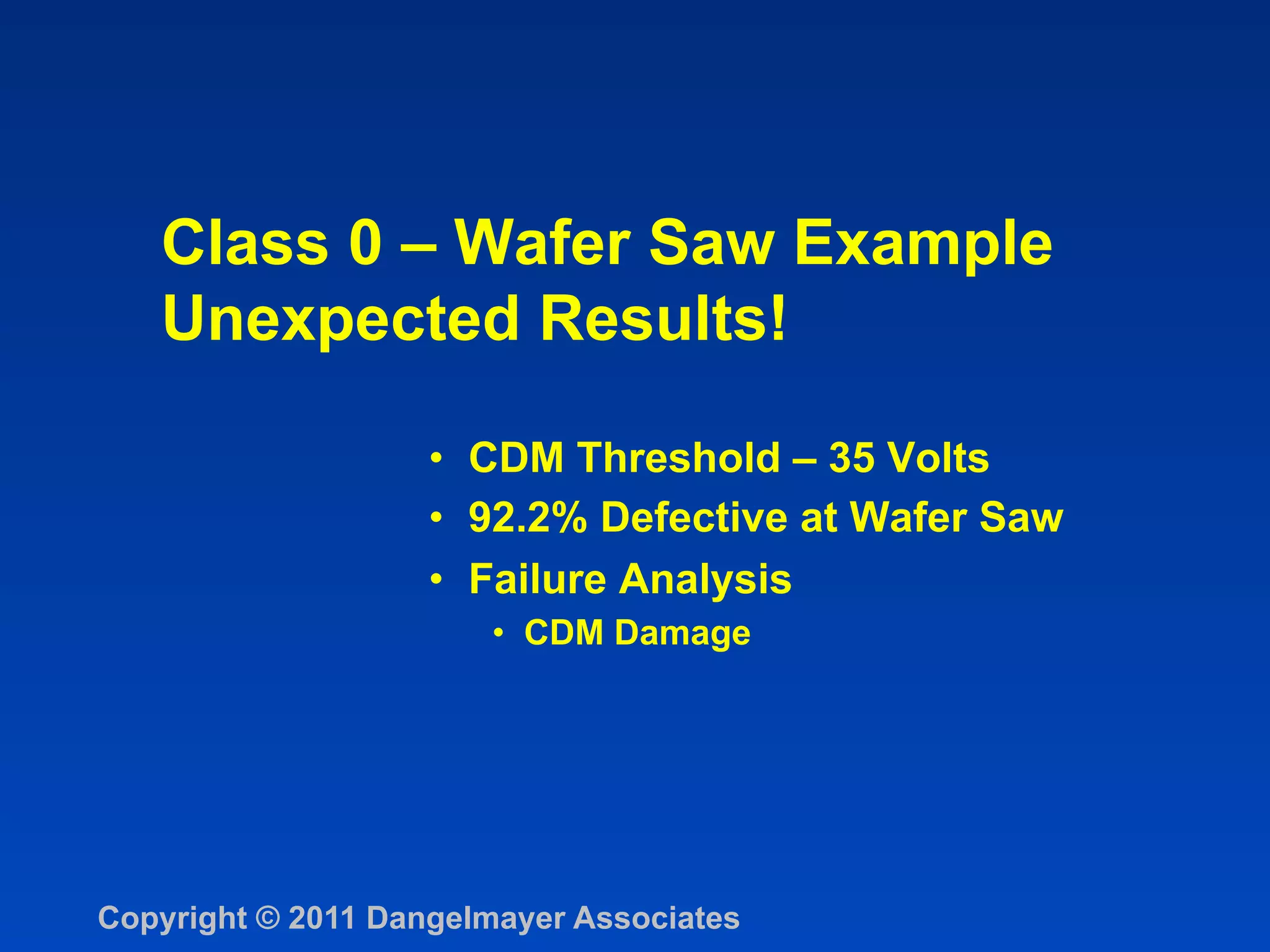

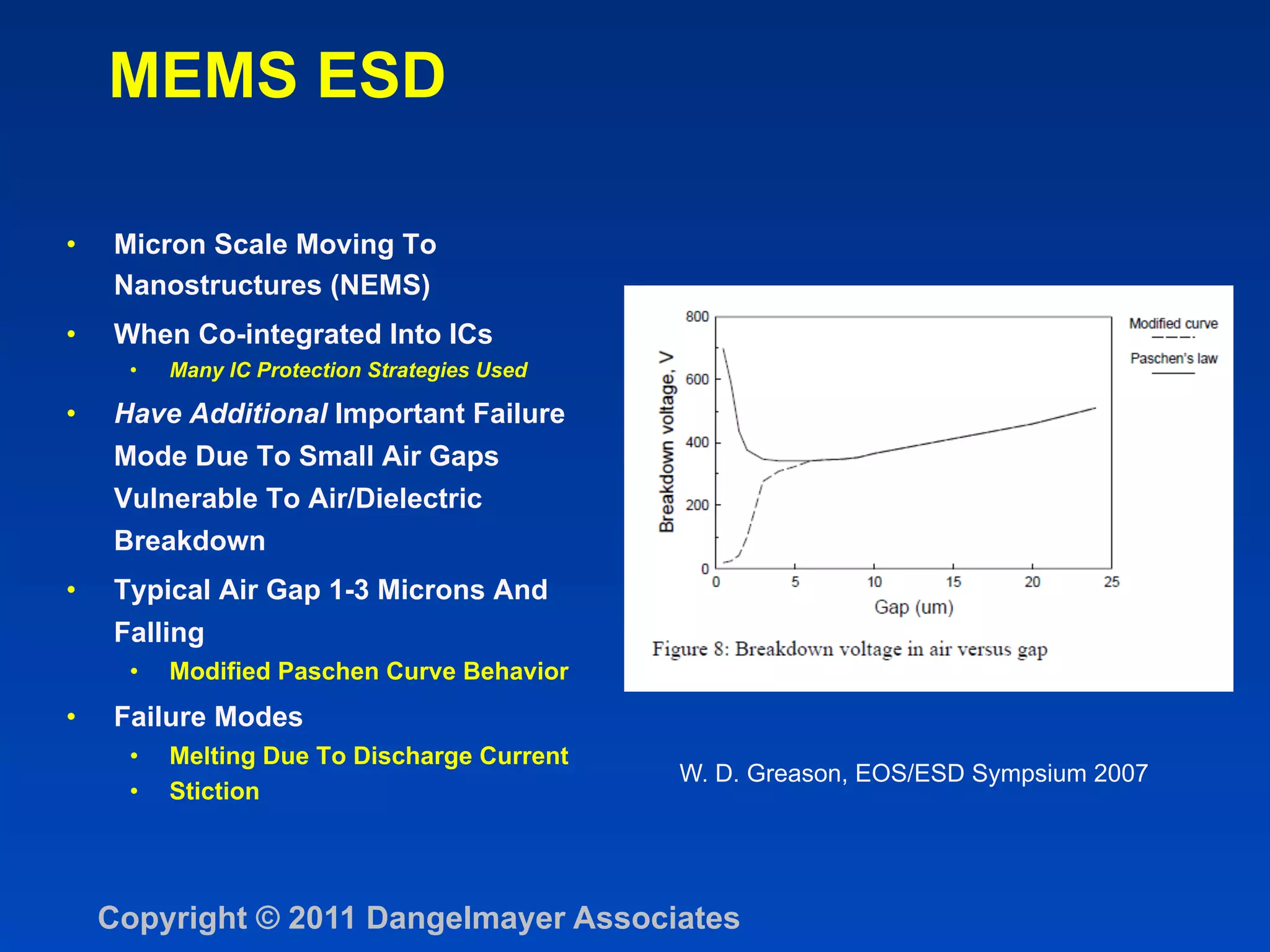

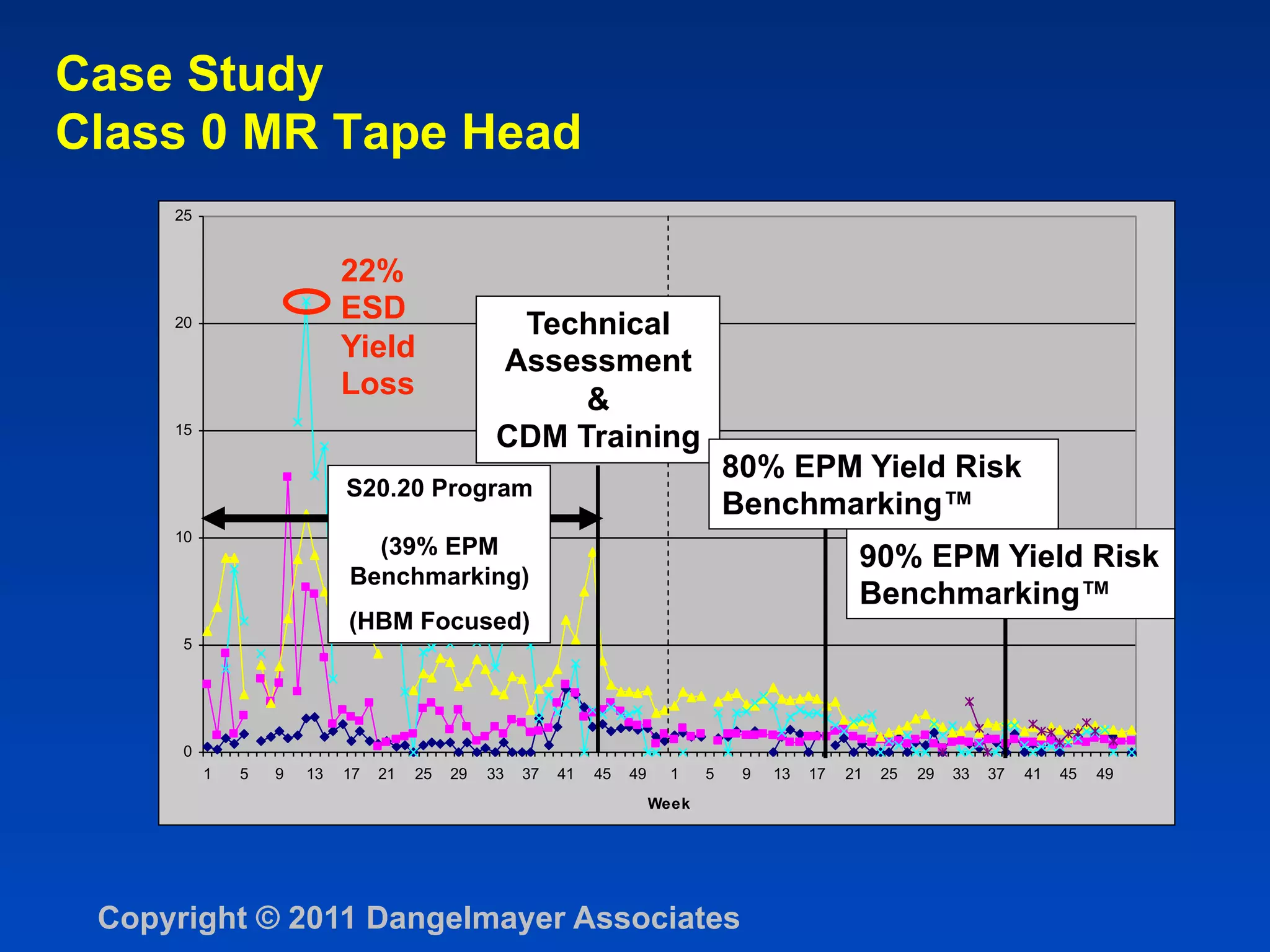

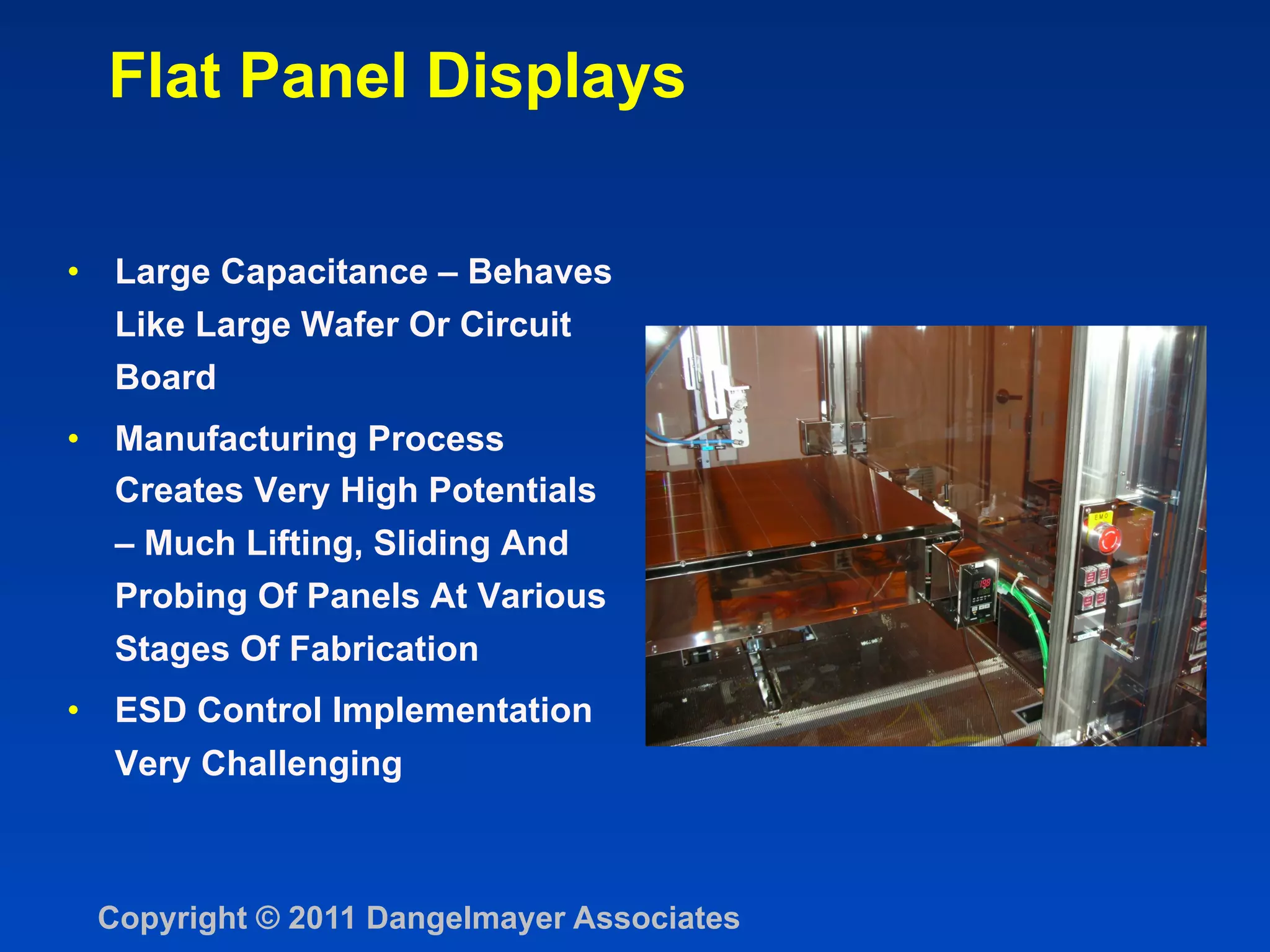

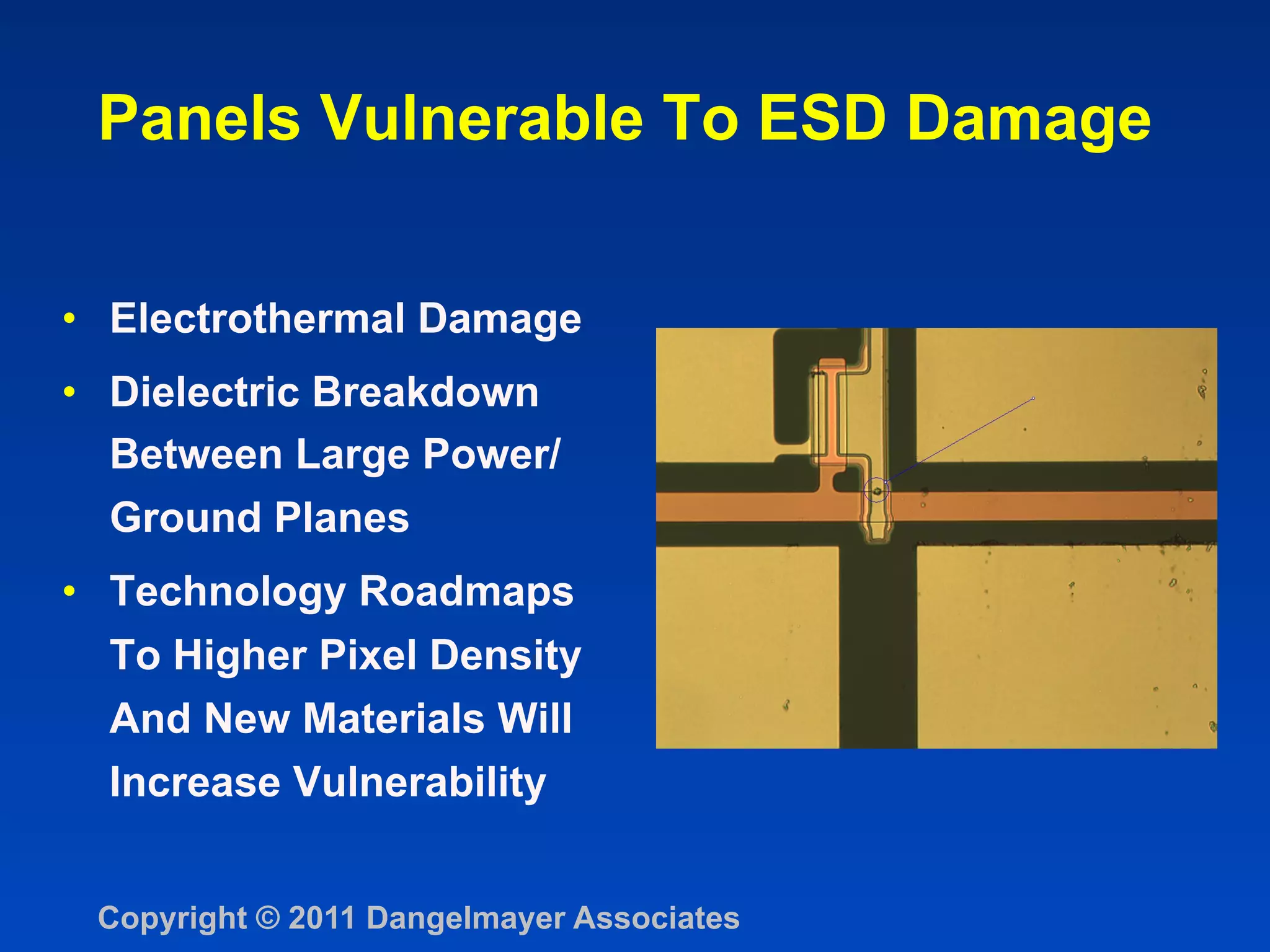

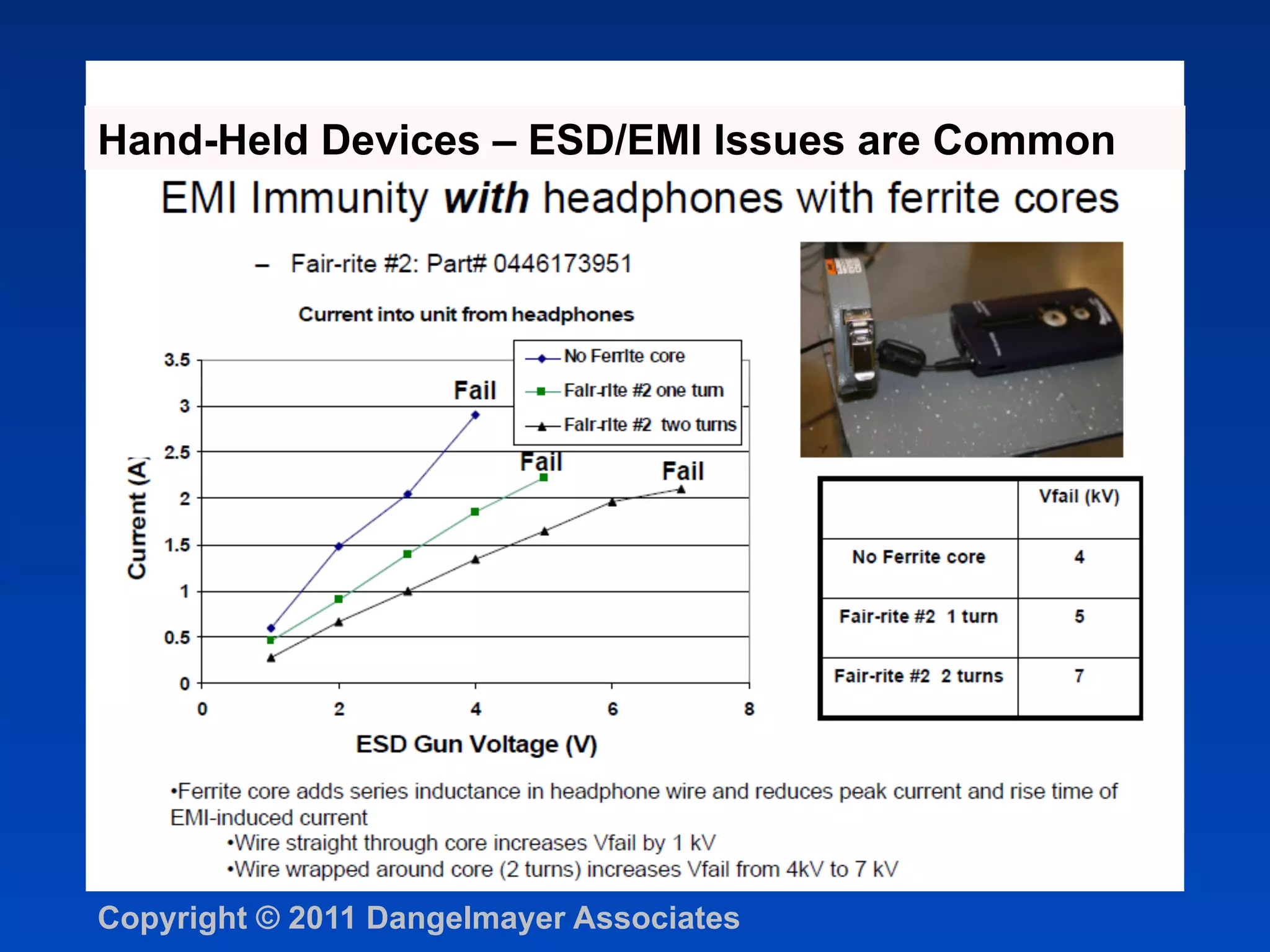

The document discusses the significant impact of electrostatic discharge (ESD) on product quality and reliability, identifying it as a leading cause of integrated circuit failures. It presents trends in ESD sensitivity, reviews different discharge models, and outlines the necessity for effective ESD countermeasures across various device types and assembly processes. Key findings include the importance of addressing failures beyond the device level, including charged board events and system-level testing, as part of ESD management strategies.