MOS and CMOS circuit design involves several key concepts:

1. Circuits are formed from diffusion, polysilicon, and metal layers isolated by silicon dioxide. Transistors form where polysilicon crosses diffusion regions.

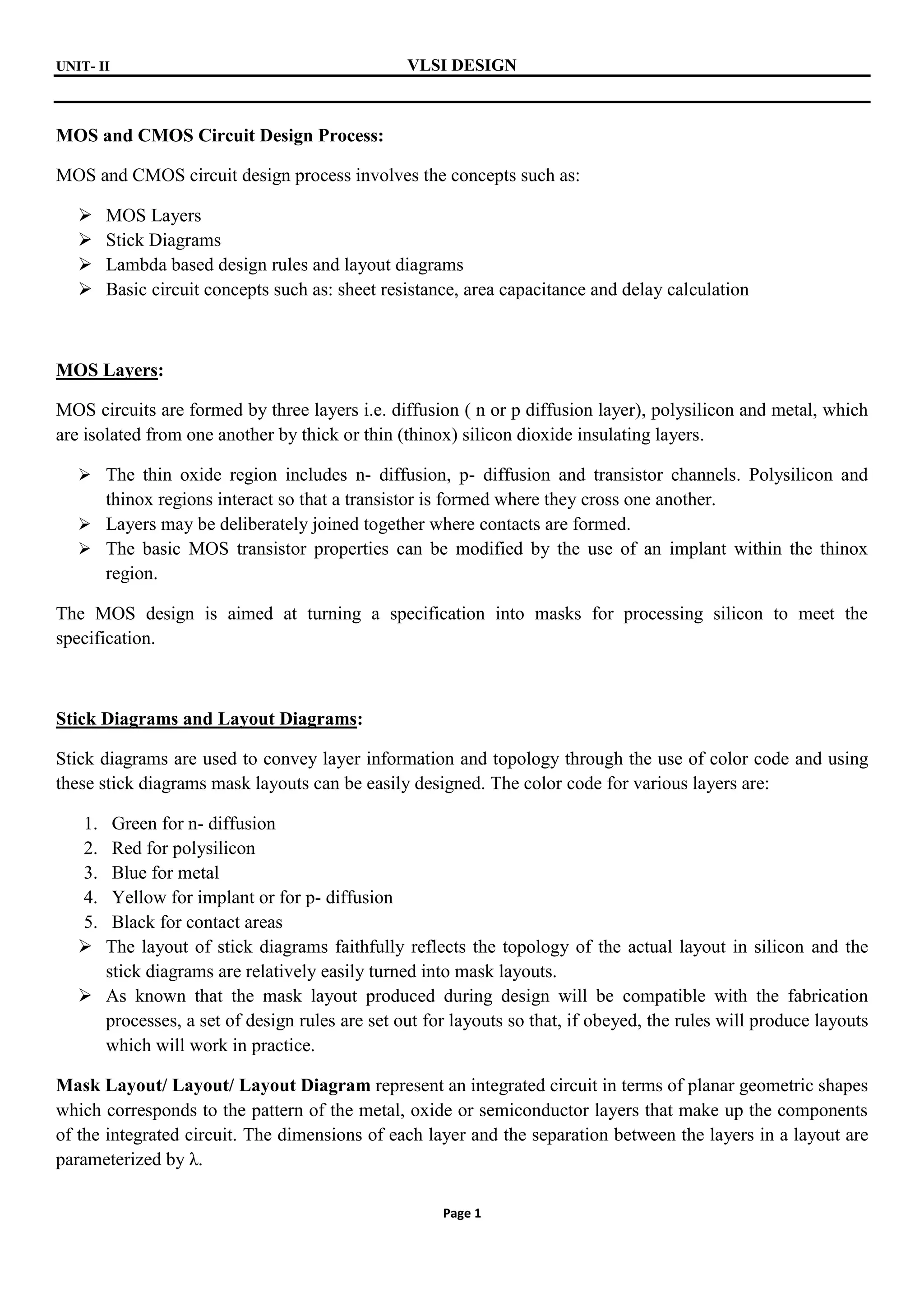

2. Stick diagrams use colors to represent layers and convey topology. Layout diagrams translate stick diagrams into mask patterns matching silicon topology.

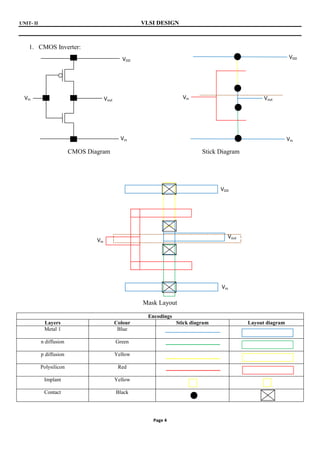

3. Design rules parameterized by λ ensure mask layouts produce working circuits across fabrication processes by specifying minimum widths, separations, and extensions in units of λ.