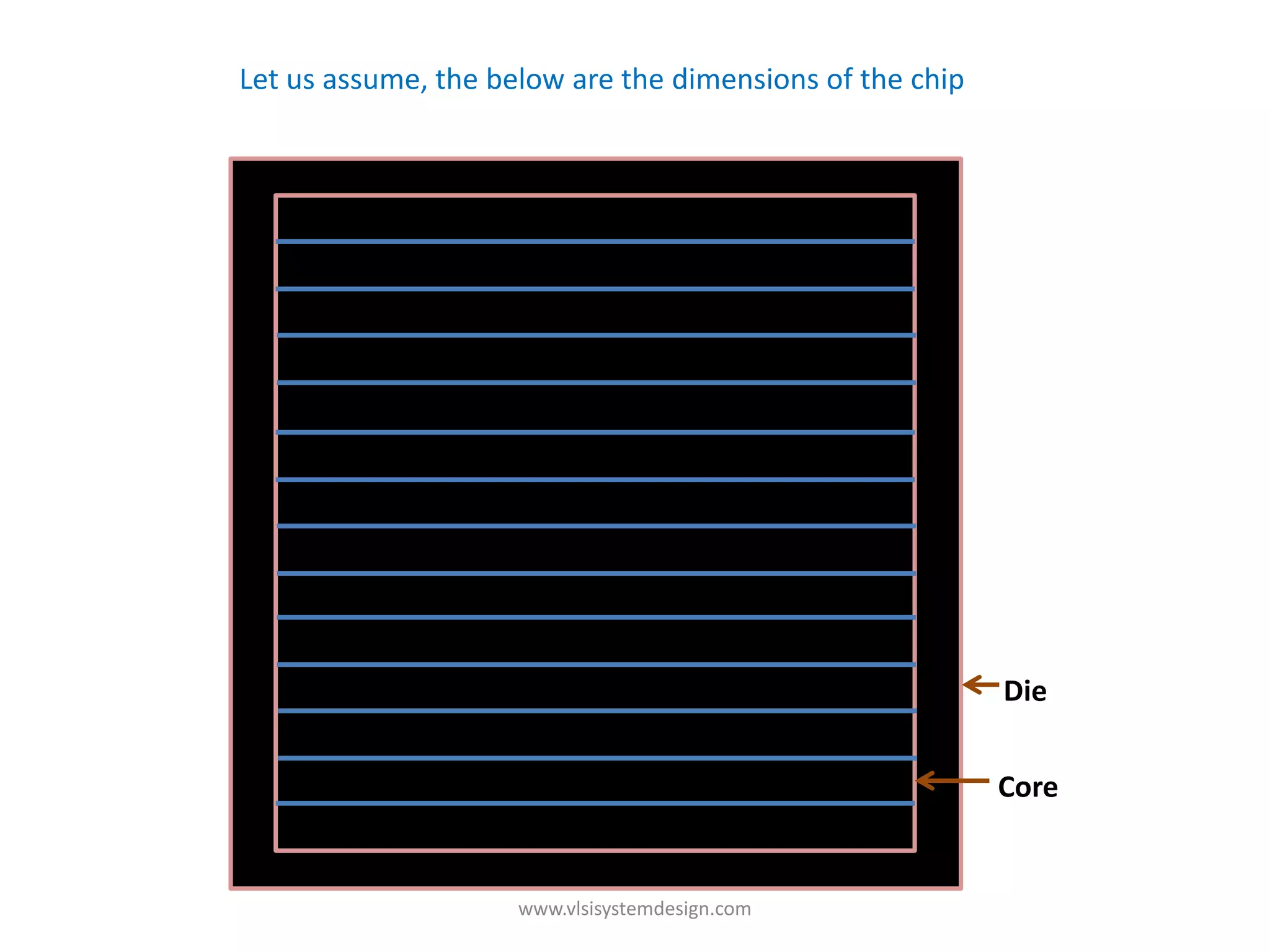

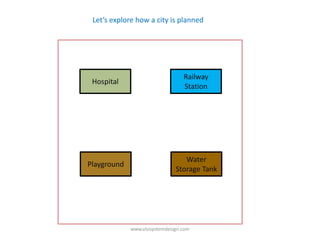

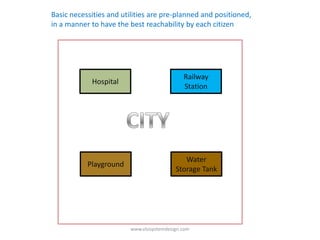

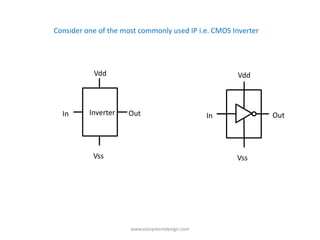

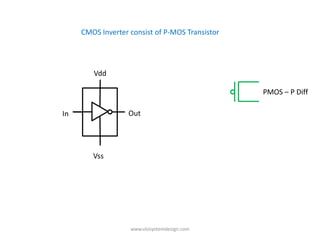

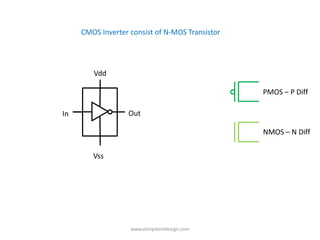

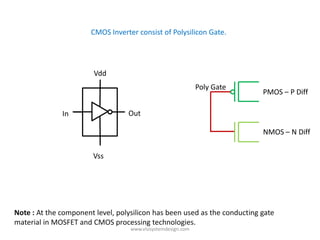

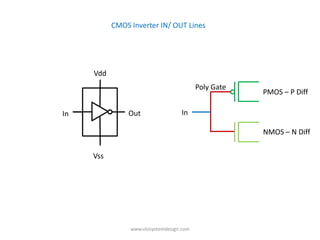

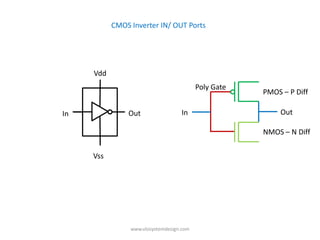

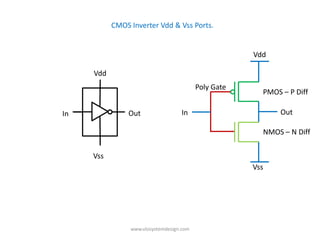

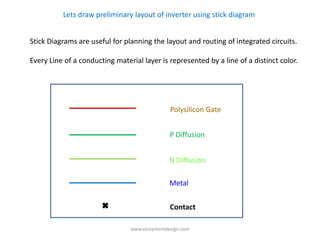

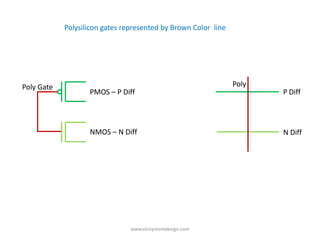

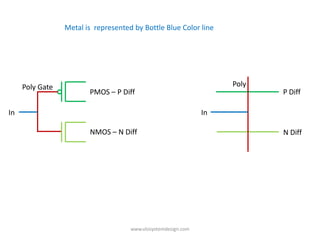

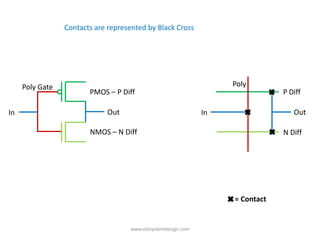

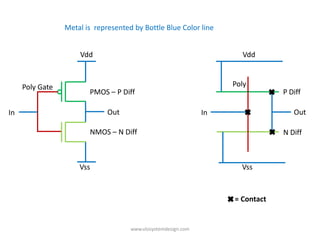

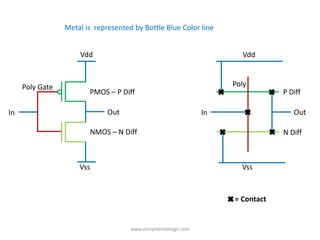

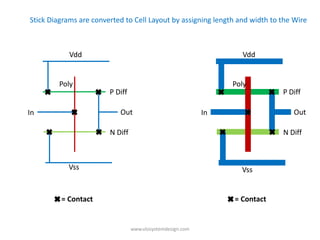

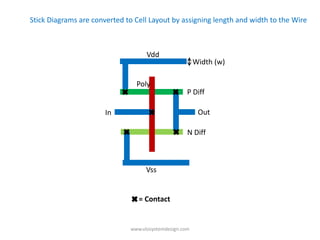

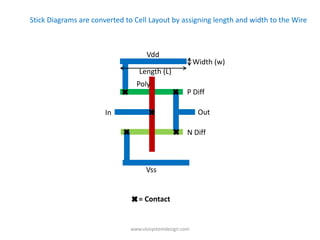

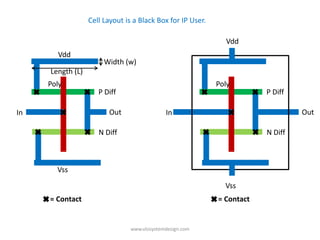

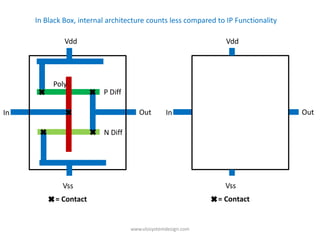

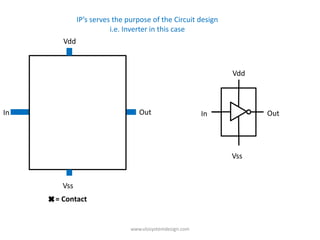

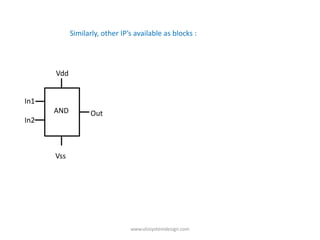

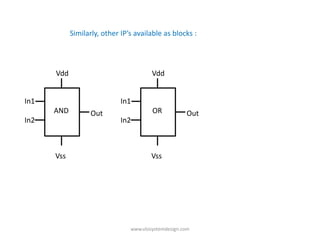

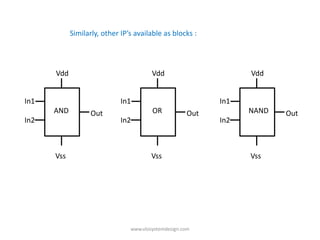

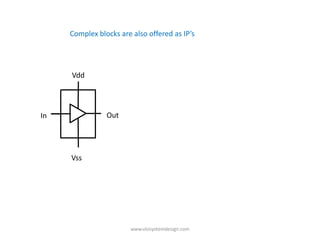

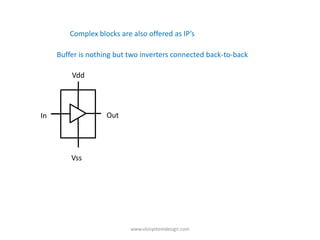

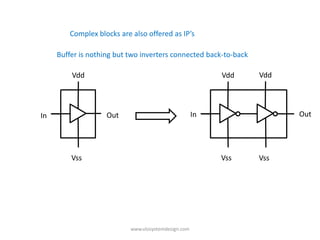

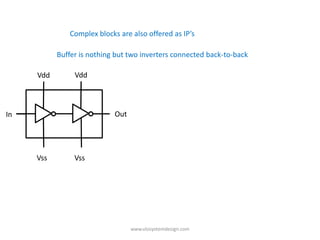

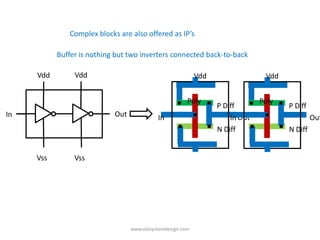

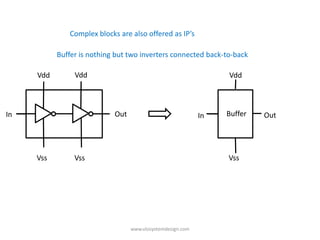

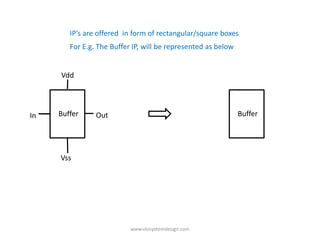

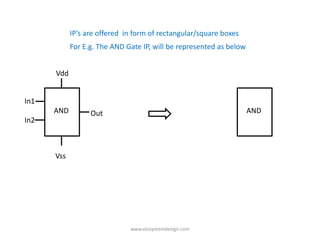

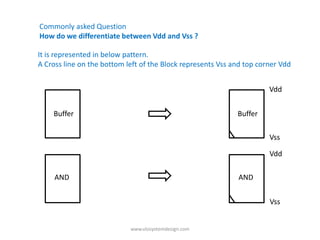

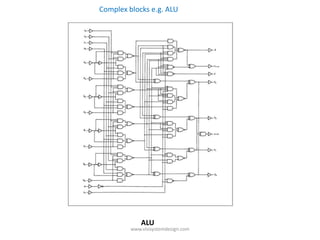

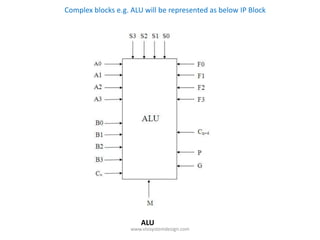

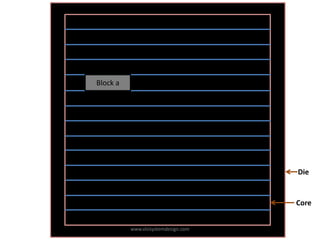

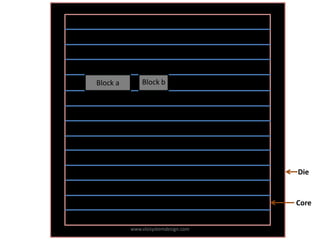

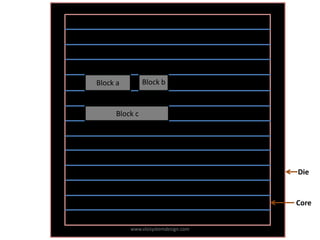

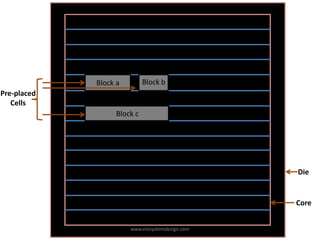

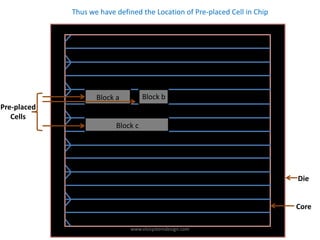

The document discusses the planning and design of chip layouts, emphasizing the importance of positioning critical cells like IPs and standard cells for optimal accessibility. It explains the architecture of CMOS inverters and the use of stick diagrams for integrated circuit layout, highlighting how these diagrams aid in planning physical design. Additionally, it covers the concept of pre-placed cells on a die core to ensure proper placement during automated design processes.