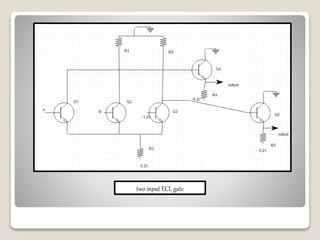

This document provides an overview of digital components including integrated circuits, decoders, encoders, multiplexers, registers, shift registers, binary counters, and memory units. It describes the basic functions and operations of these components. Integrated circuits contain electronic components on a small silicon chip. Digital logic families include TTL, ECL, MOS, and CMOS. Decoders and encoders convert between binary and decoded representations. Registers store binary data and shift registers can shift data serially or in parallel. Counters sequence through binary numbers. Memory units like RAM and ROM store and retrieve binary words from addresses.