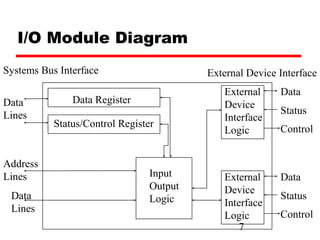

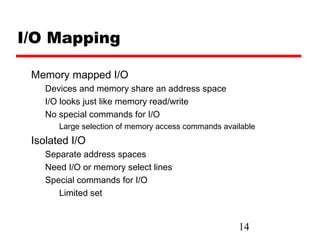

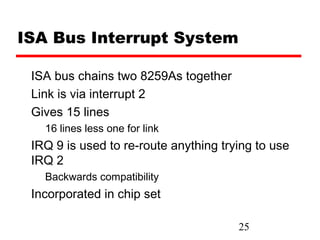

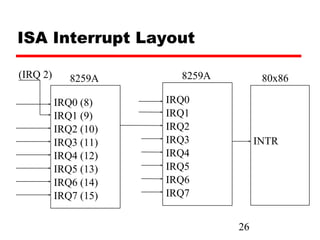

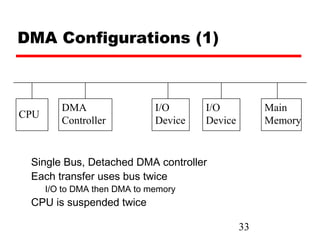

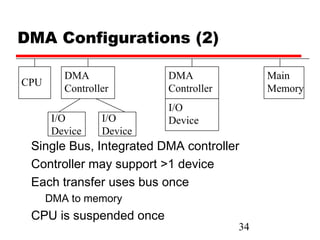

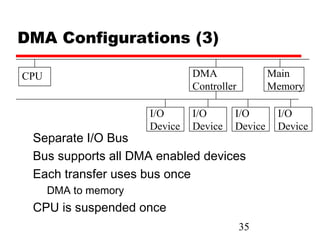

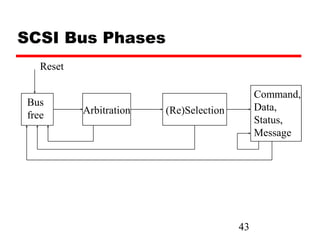

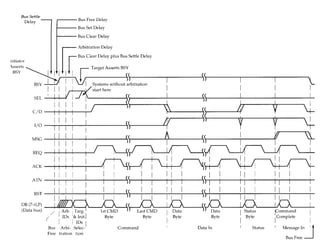

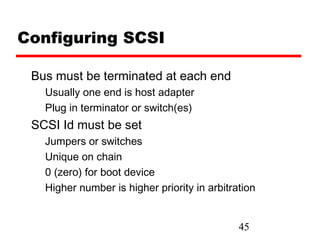

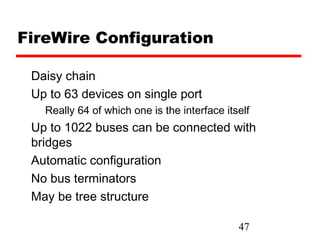

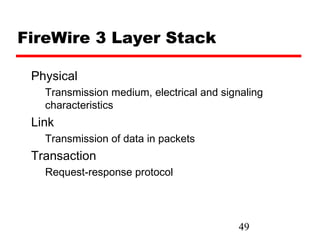

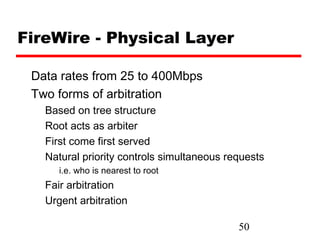

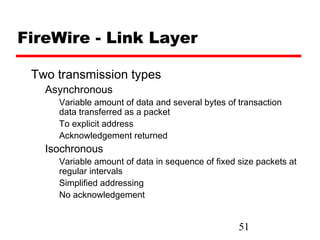

The document discusses input/output (I/O) in computer systems. It describes various I/O techniques including programmed I/O, interrupt-driven I/O, and direct memory access (DMA). It also covers I/O modules, external devices, addressing schemes, and interface standards like SCSI and FireWire.