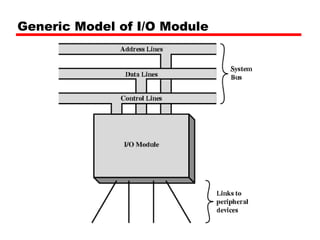

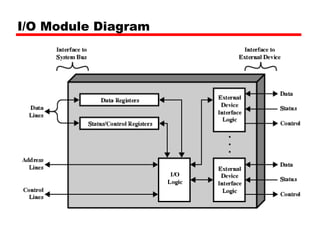

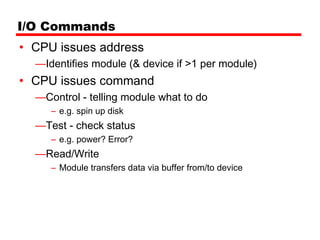

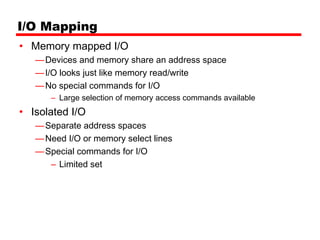

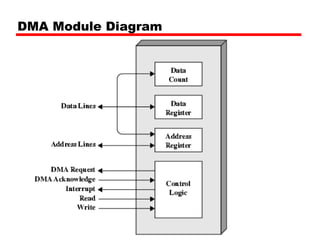

This document discusses computer input/output (I/O) architecture. It describes the challenges posed by peripherals that operate at different speeds and formats than the CPU. I/O modules interface between the CPU/memory and peripherals. They handle control, communication, buffering and error handling. Data can be transferred via programmed I/O where the CPU directly controls transfers, interrupt-driven I/O where devices interrupt the CPU, or direct memory access (DMA) where an I/O controller handles transfers without CPU involvement. Overall the document provides an overview of common I/O techniques and module designs used to interface peripherals with the computer system.