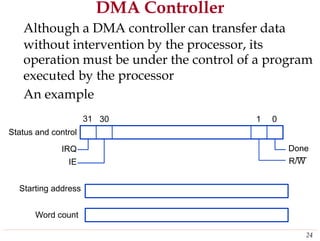

This document provides an overview of input/output organization in computers. It discusses how computers can communicate with external devices through buses and interfaces. It covers different I/O techniques like programmed I/O, interrupt-driven I/O, and direct memory access. Interrupts allow devices to signal the processor when they need service. DMA controllers can transfer data directly between devices and memory without processor involvement. The document also addresses handling multiple devices, interrupt priorities, and simultaneous interrupt requests.