This document summarizes key concepts about biasing BJTs:

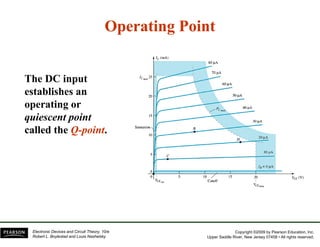

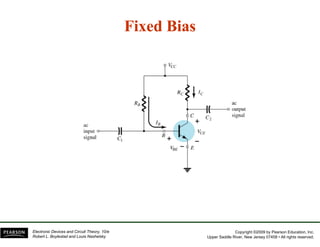

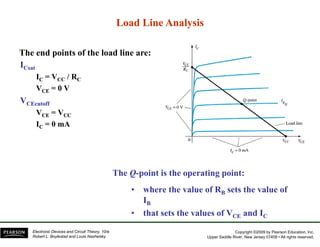

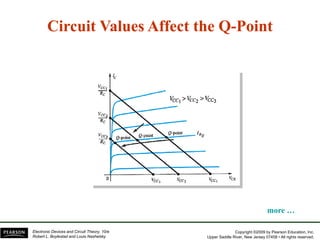

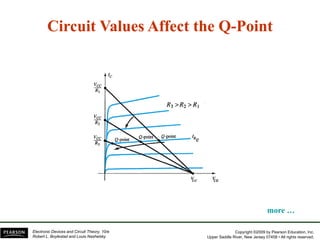

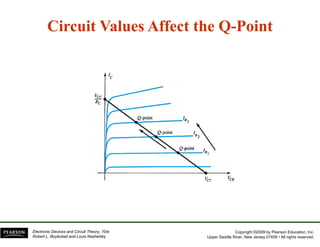

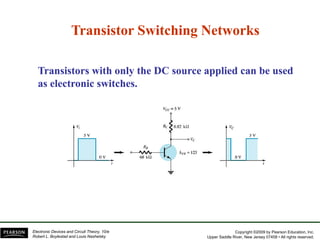

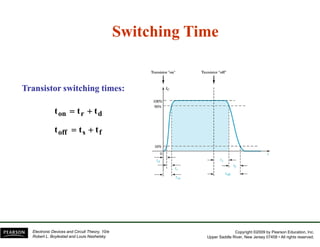

1) Biasing involves applying DC voltages to turn on a transistor so it can amplify an AC signal. This establishes an operating point called the Q-point.

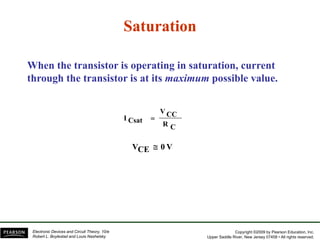

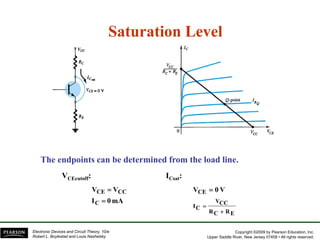

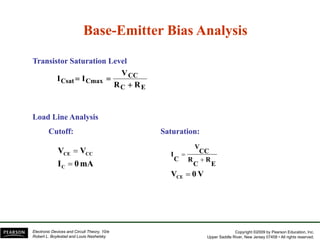

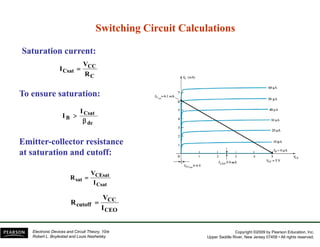

2) There are three regions of transistor operation depending on junction biases: active, cutoff, and saturation.

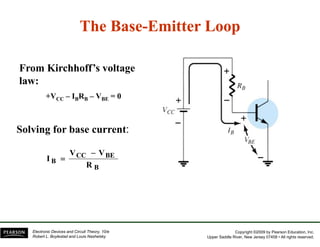

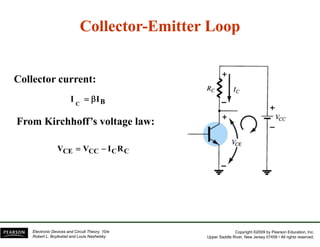

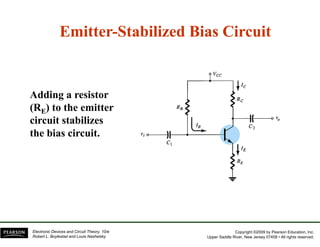

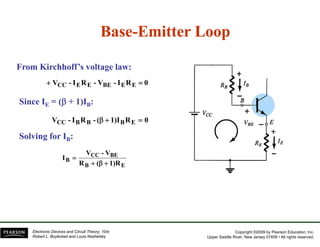

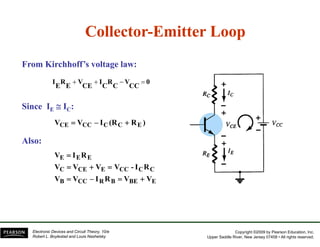

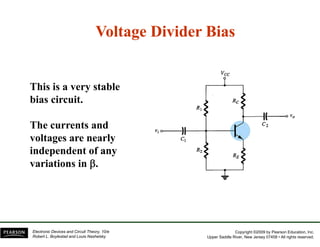

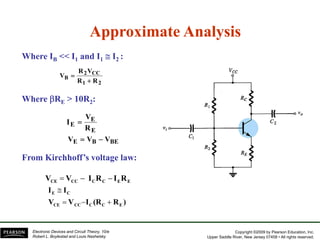

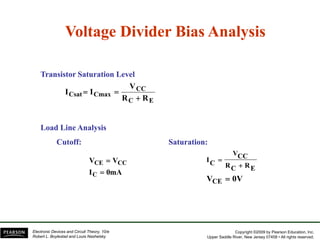

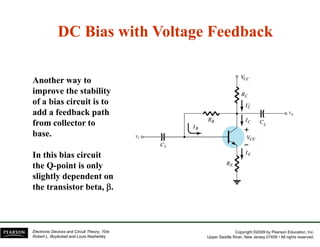

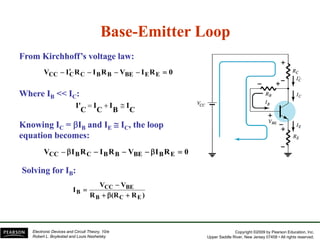

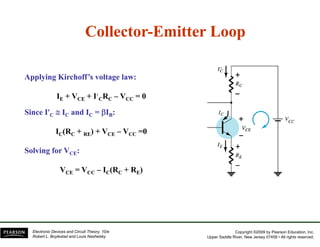

3) Common bias circuits include fixed bias, emitter-stabilized bias, and voltage divider bias. Adding a resistor to the emitter improves stability.