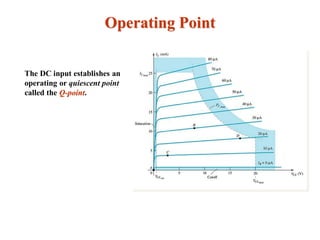

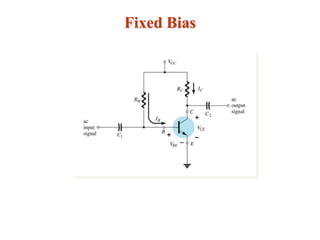

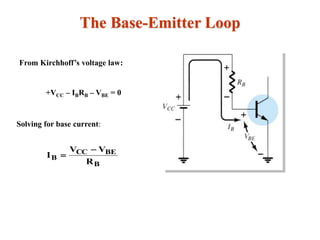

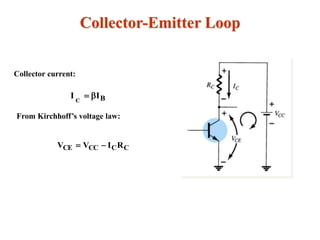

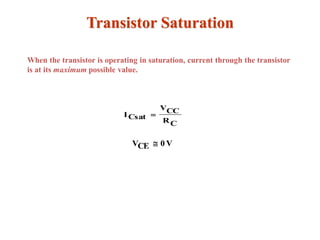

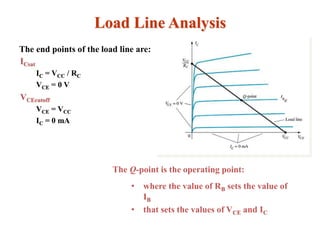

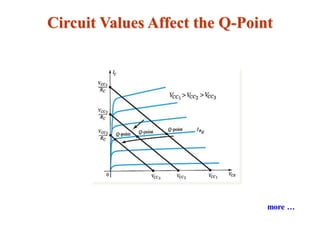

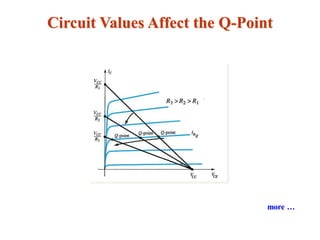

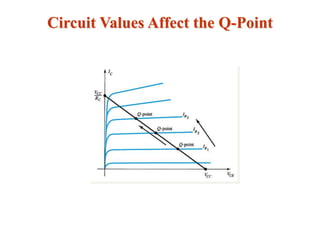

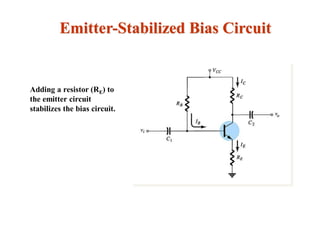

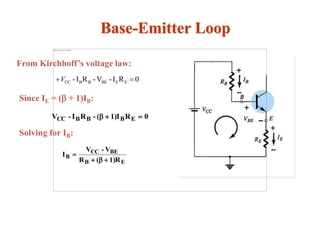

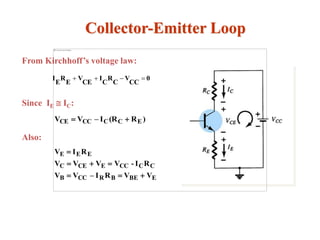

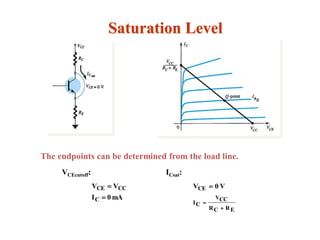

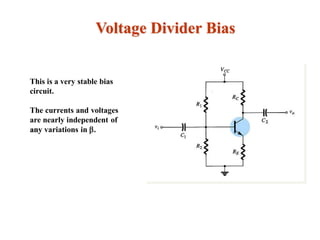

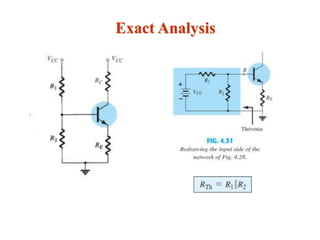

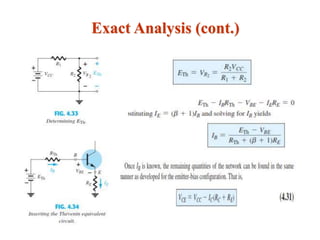

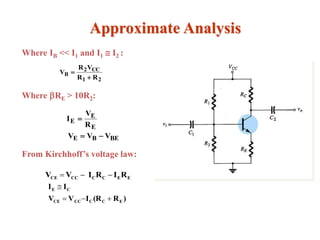

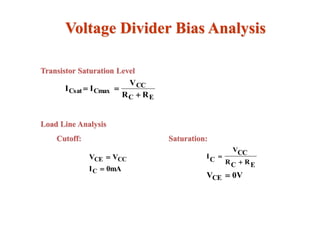

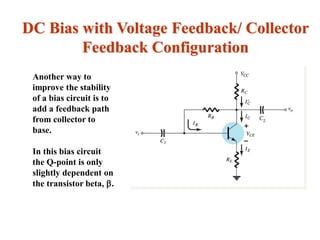

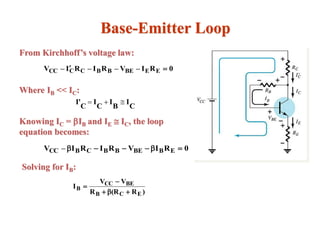

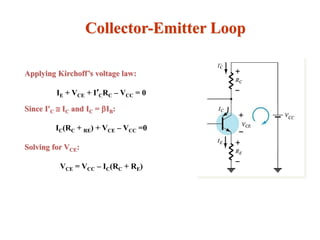

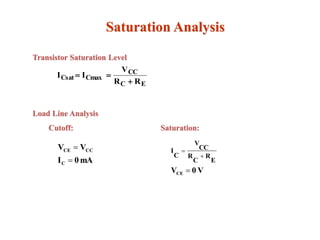

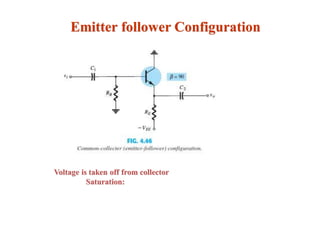

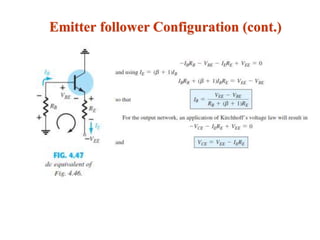

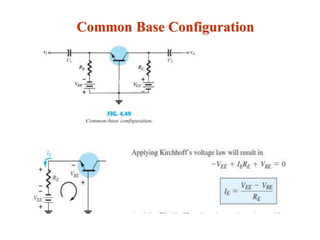

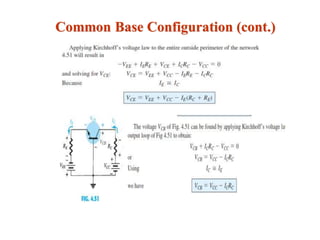

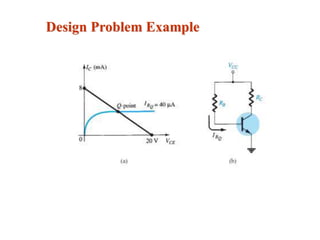

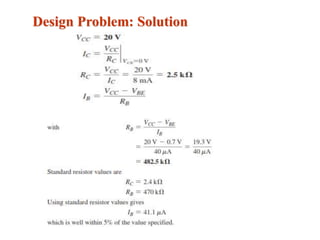

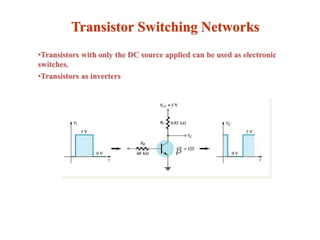

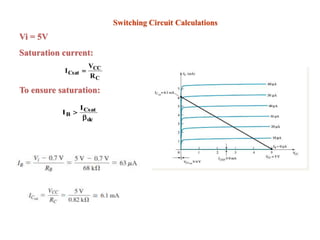

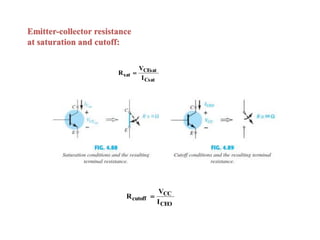

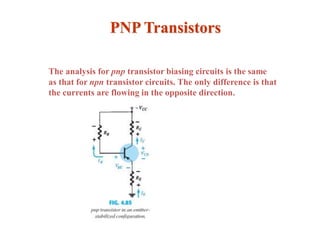

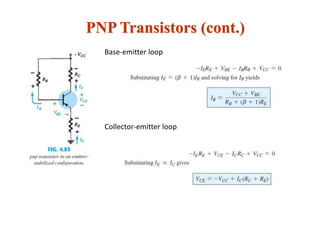

The document explains DC biasing techniques for bipolar junction transistors (BJTs) crucial for establishing operating points in various states (active, cutoff, saturation). It details different biasing circuits, such as fixed-bias, voltage divider bias, and emitter-stabilized bias, emphasizing stability and feedback mechanisms to enhance performance. Additionally, it covers analysis of transistor saturation and troubleshooting methods for biasing circuits.