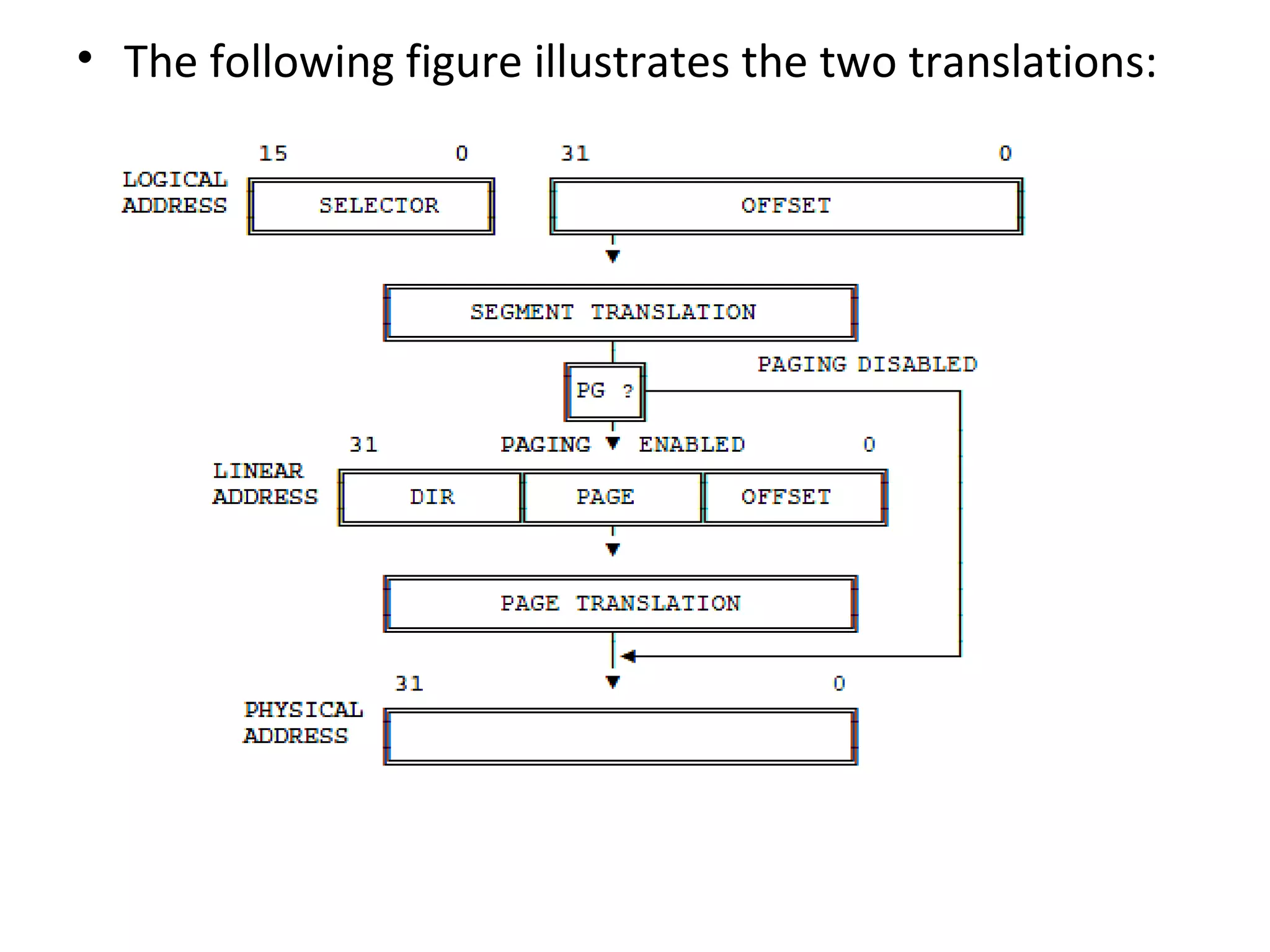

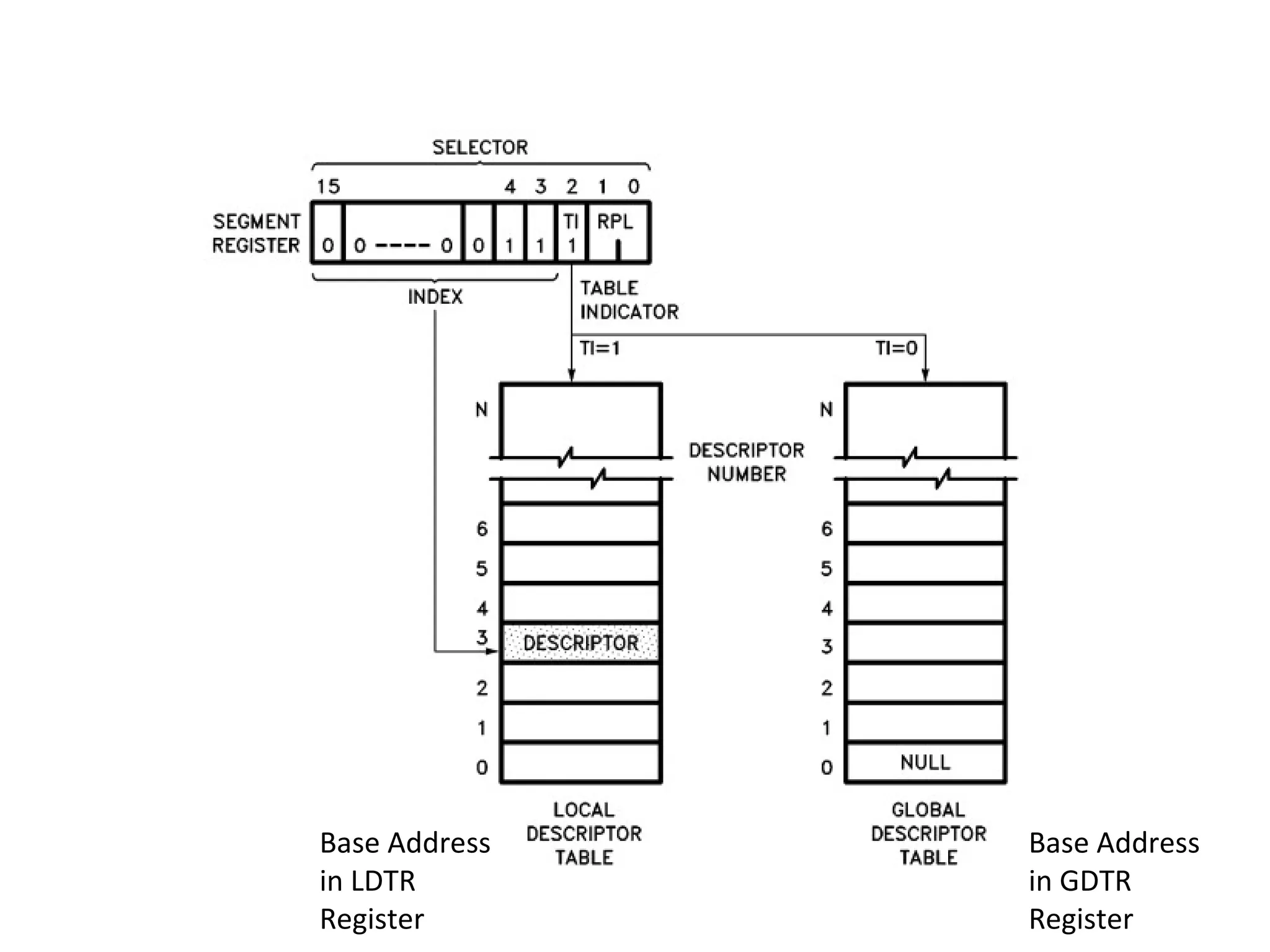

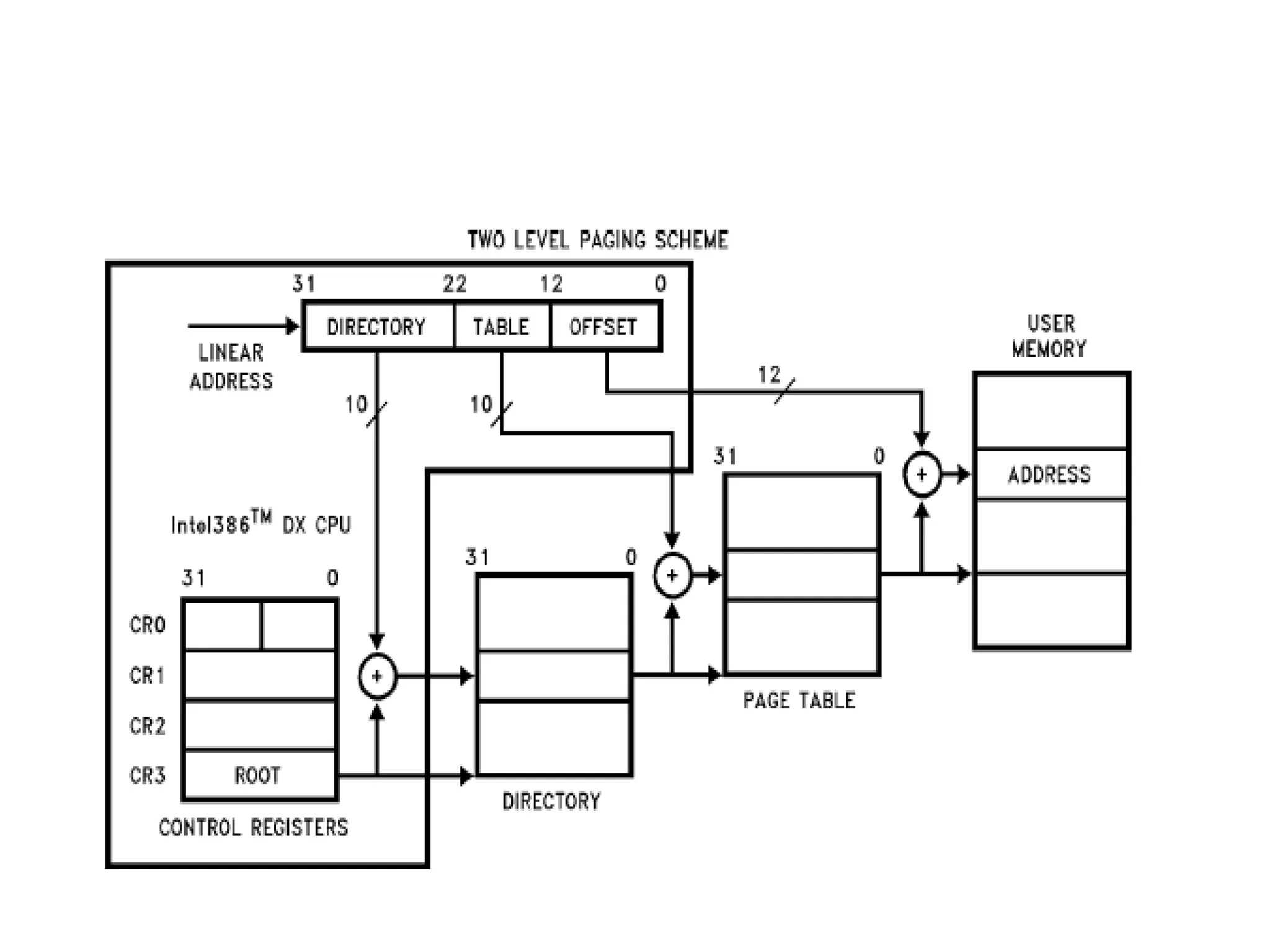

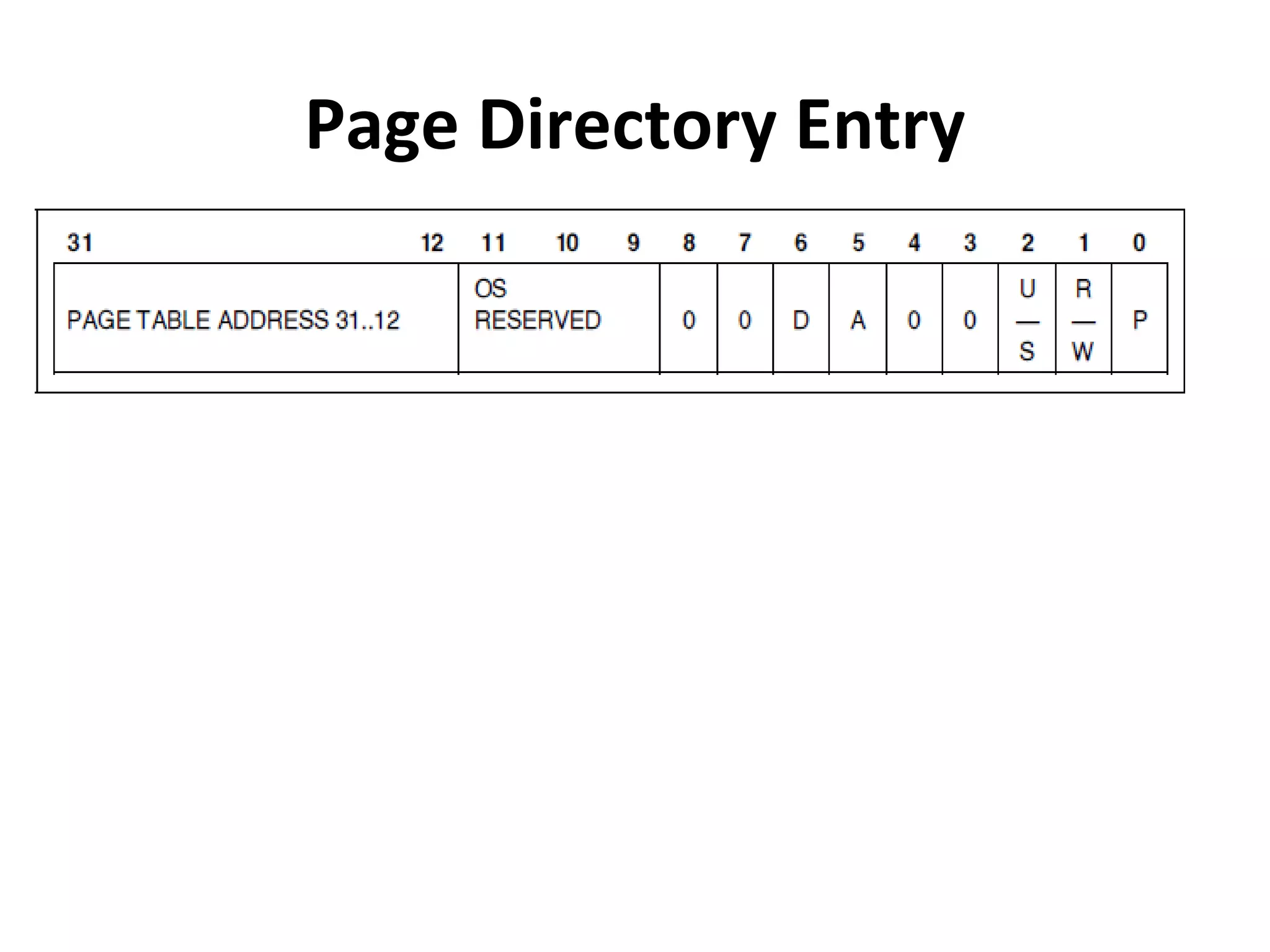

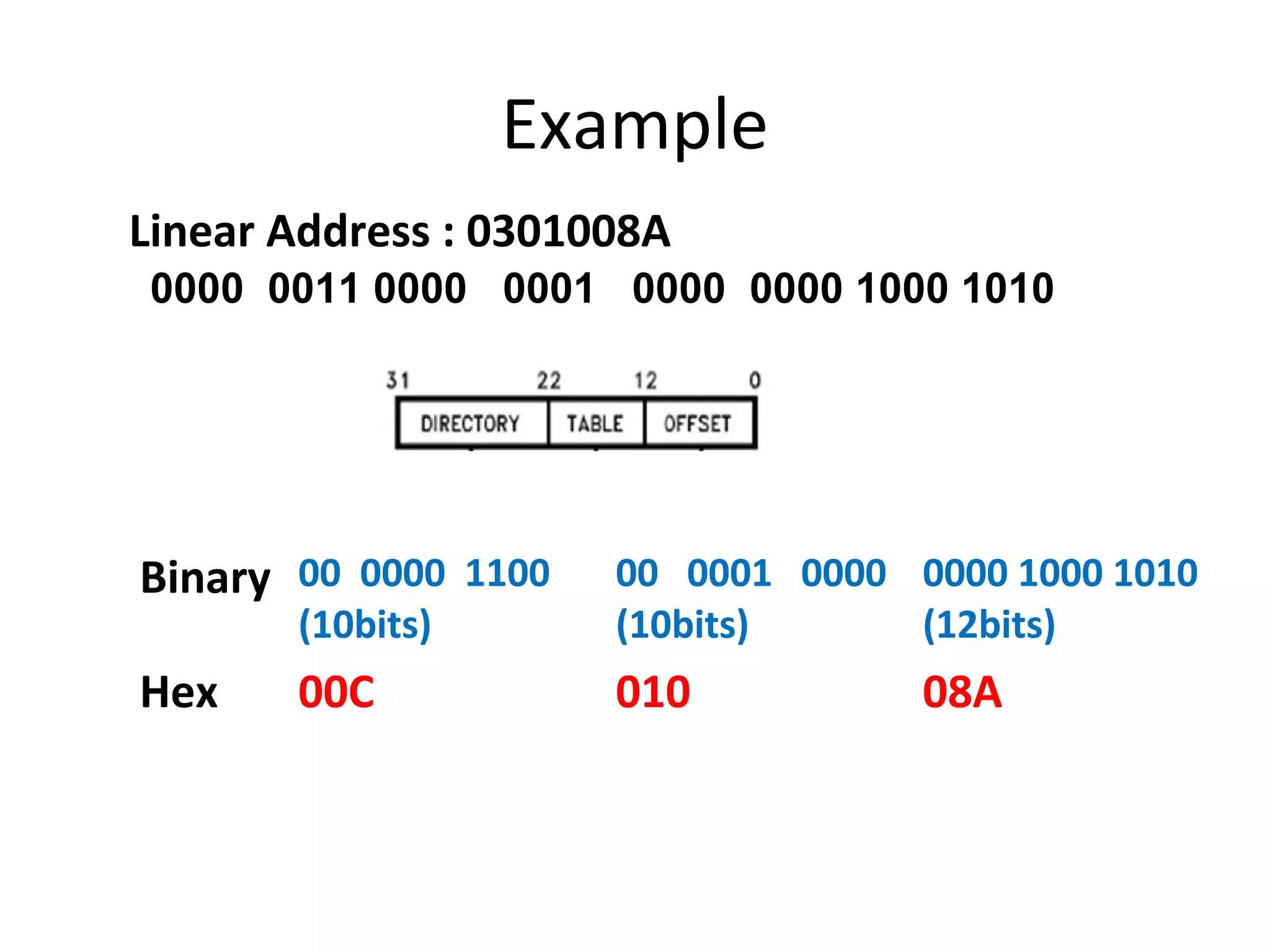

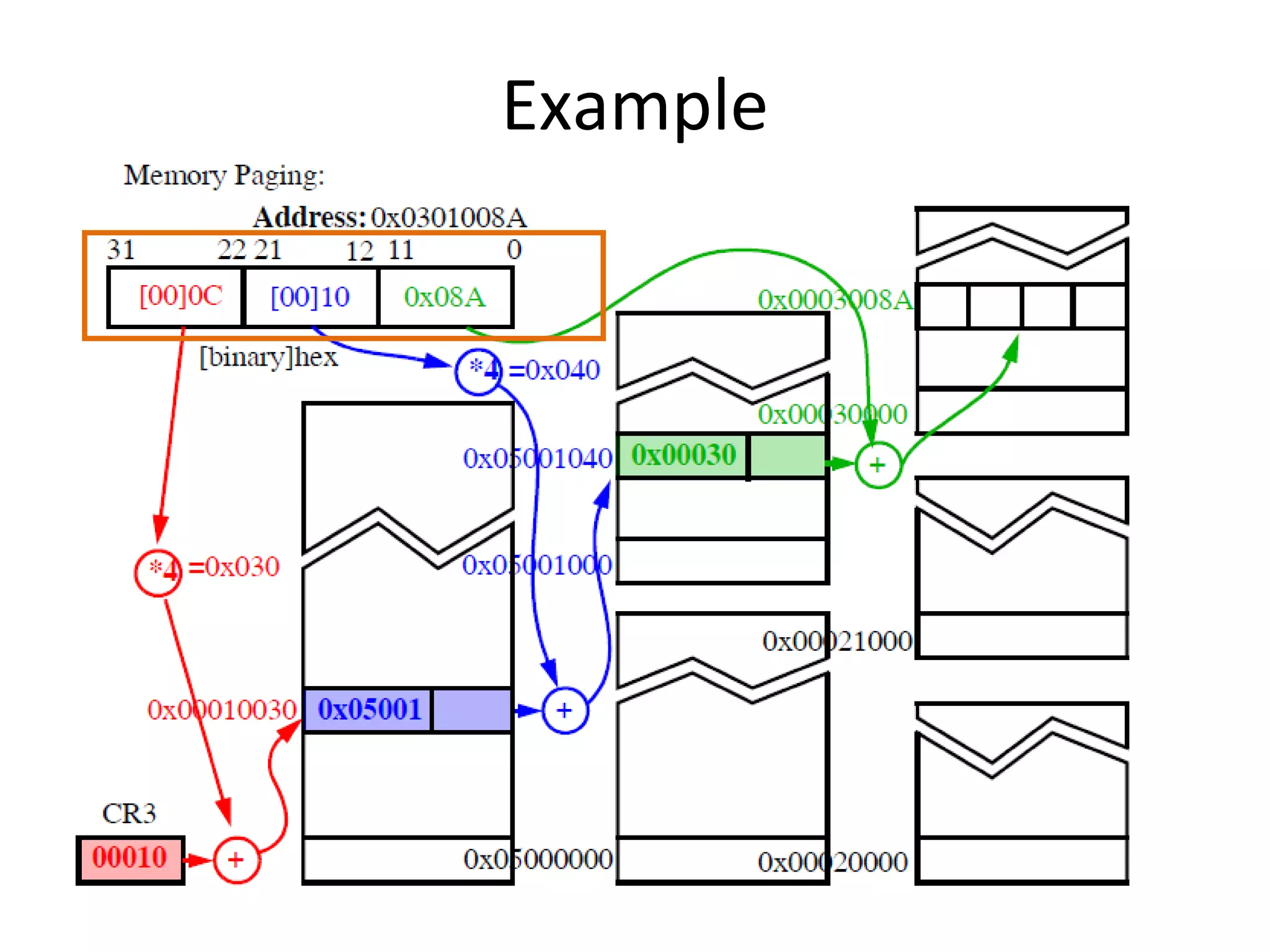

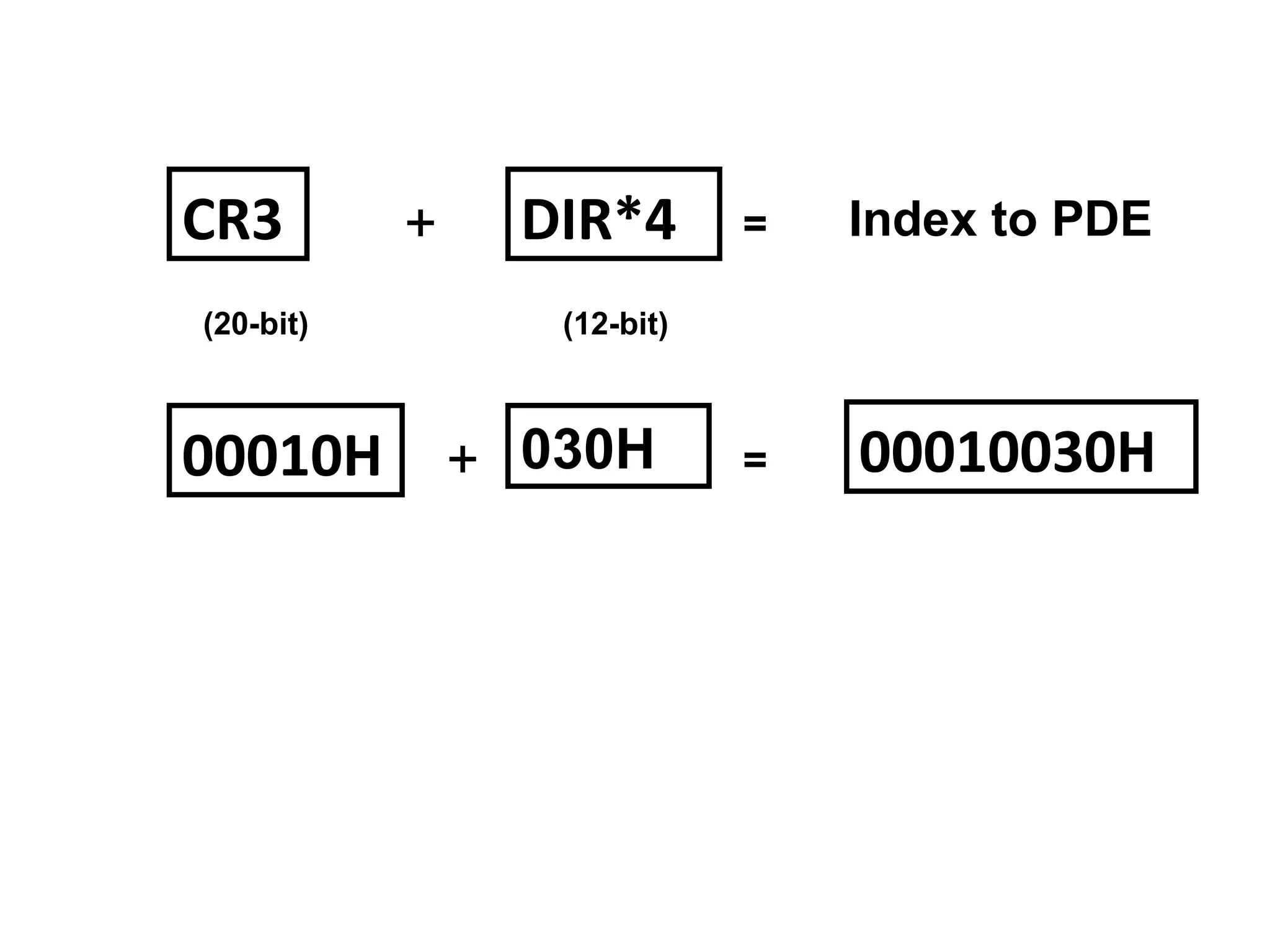

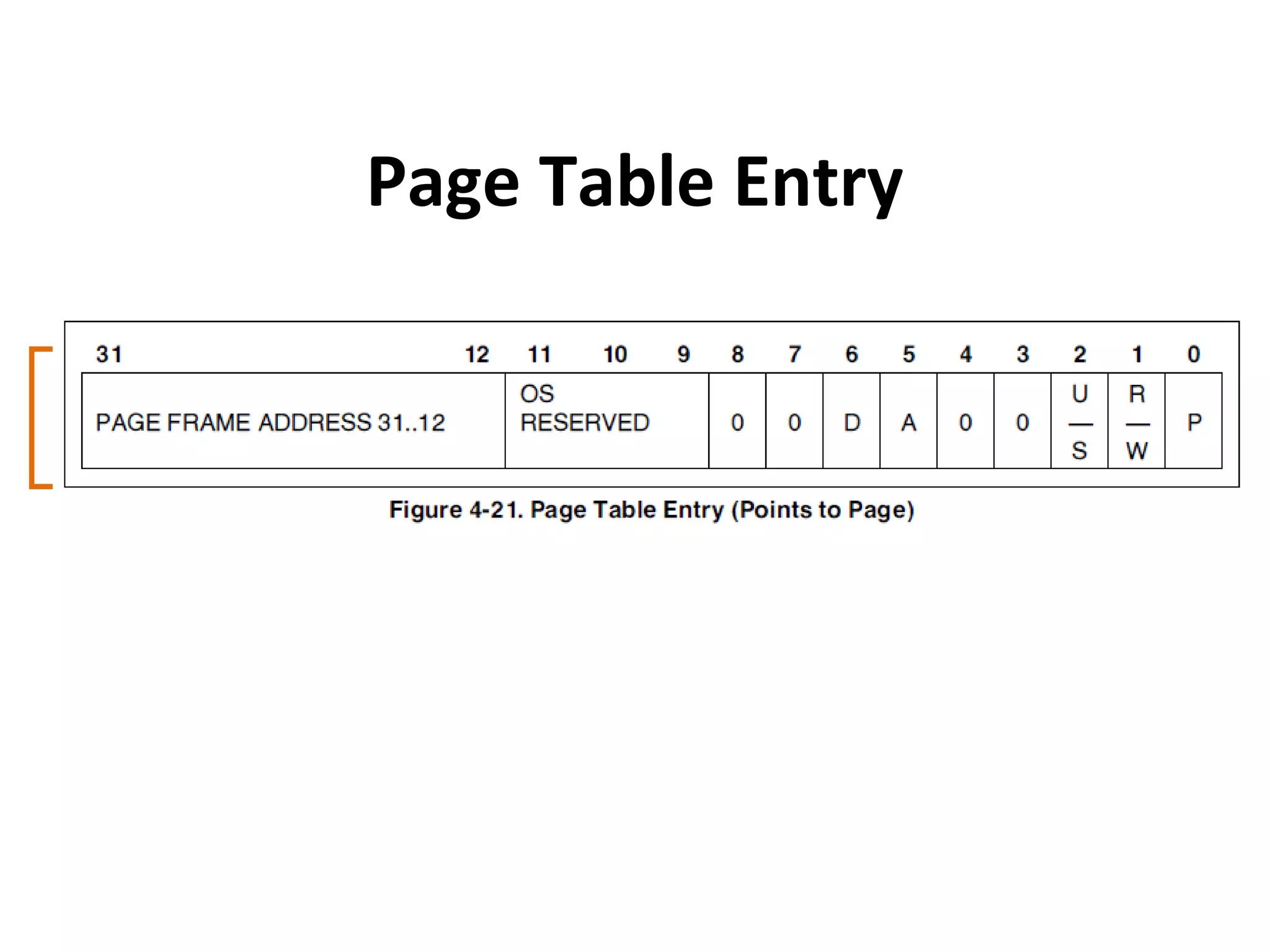

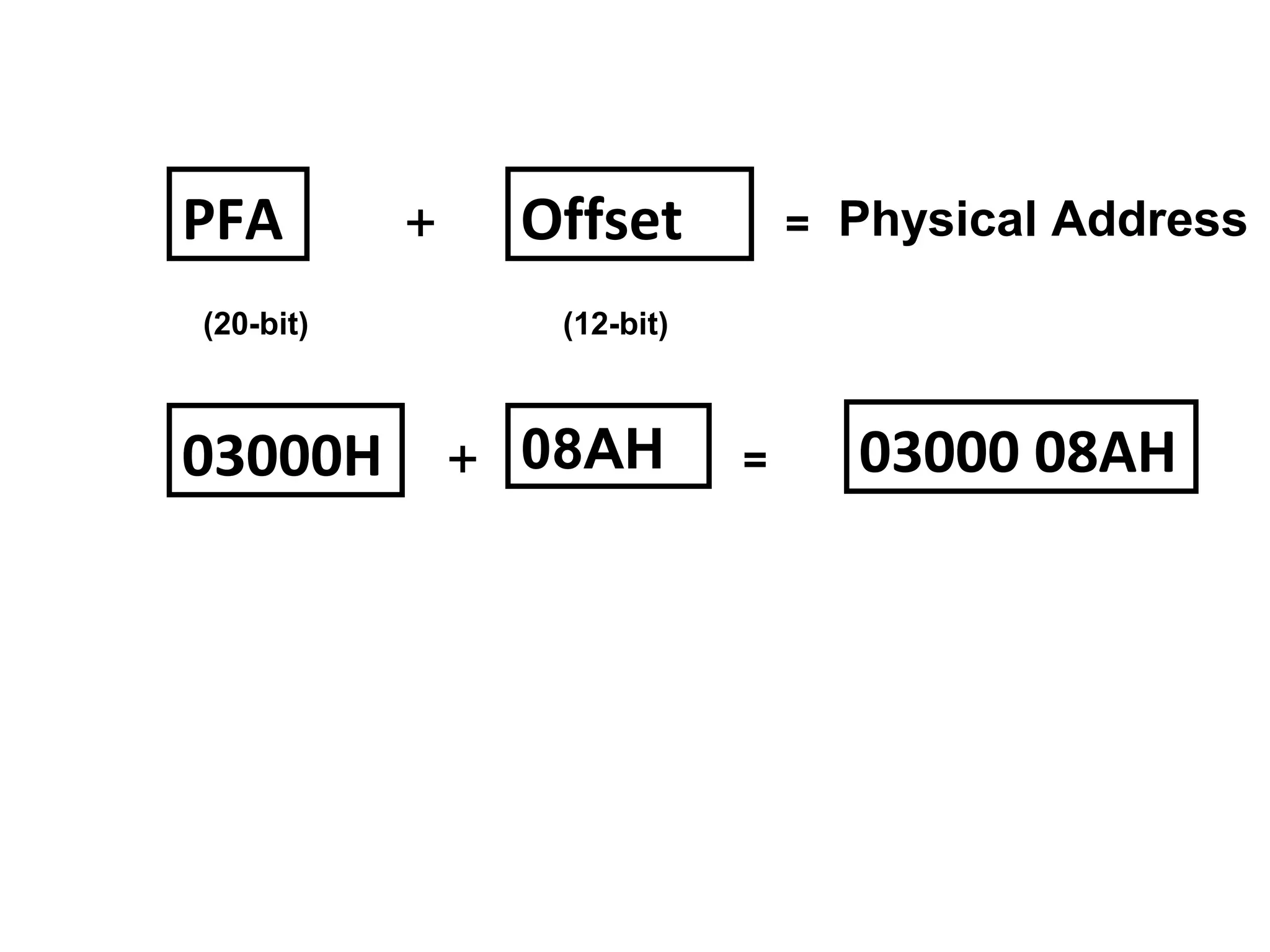

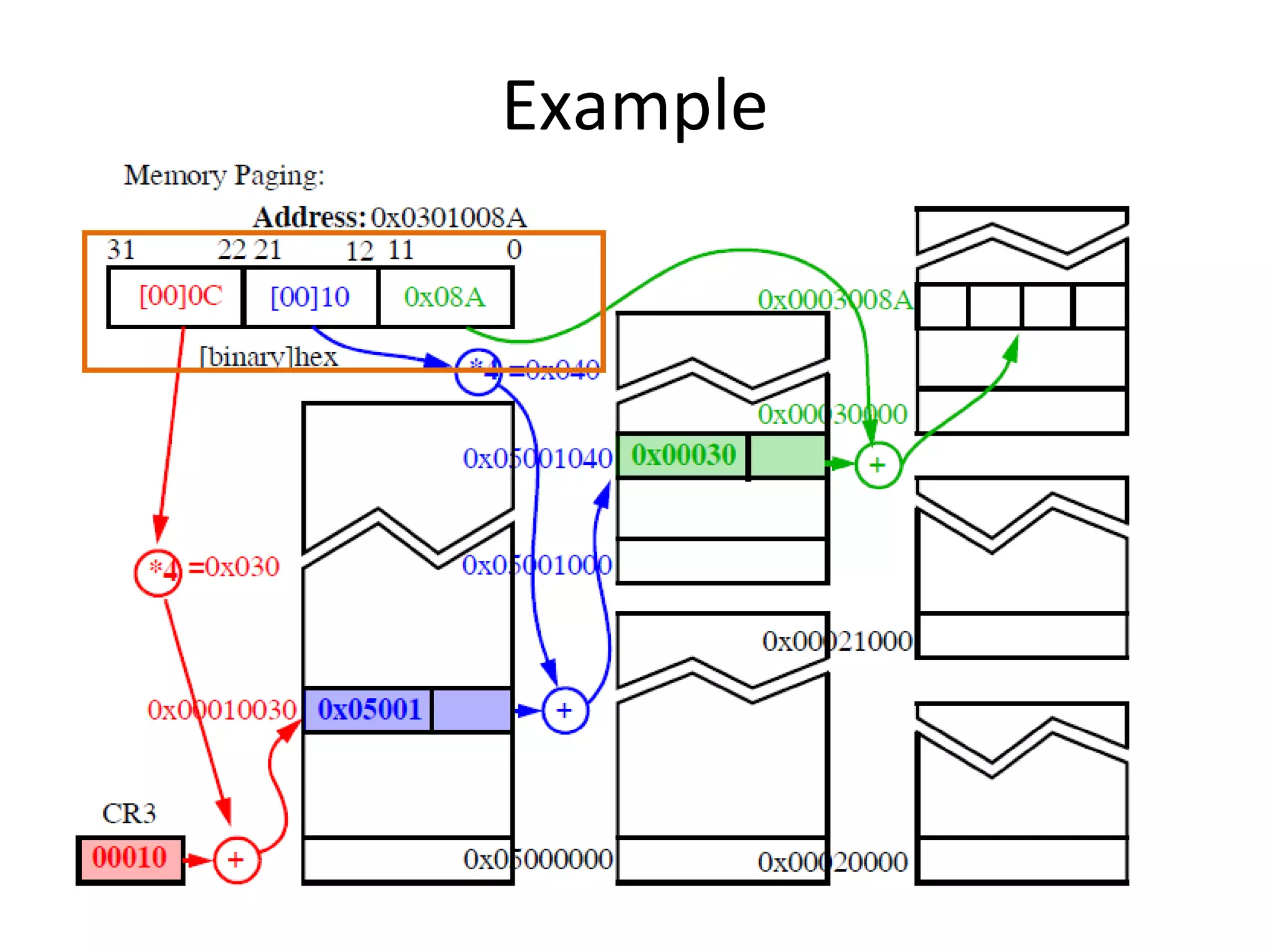

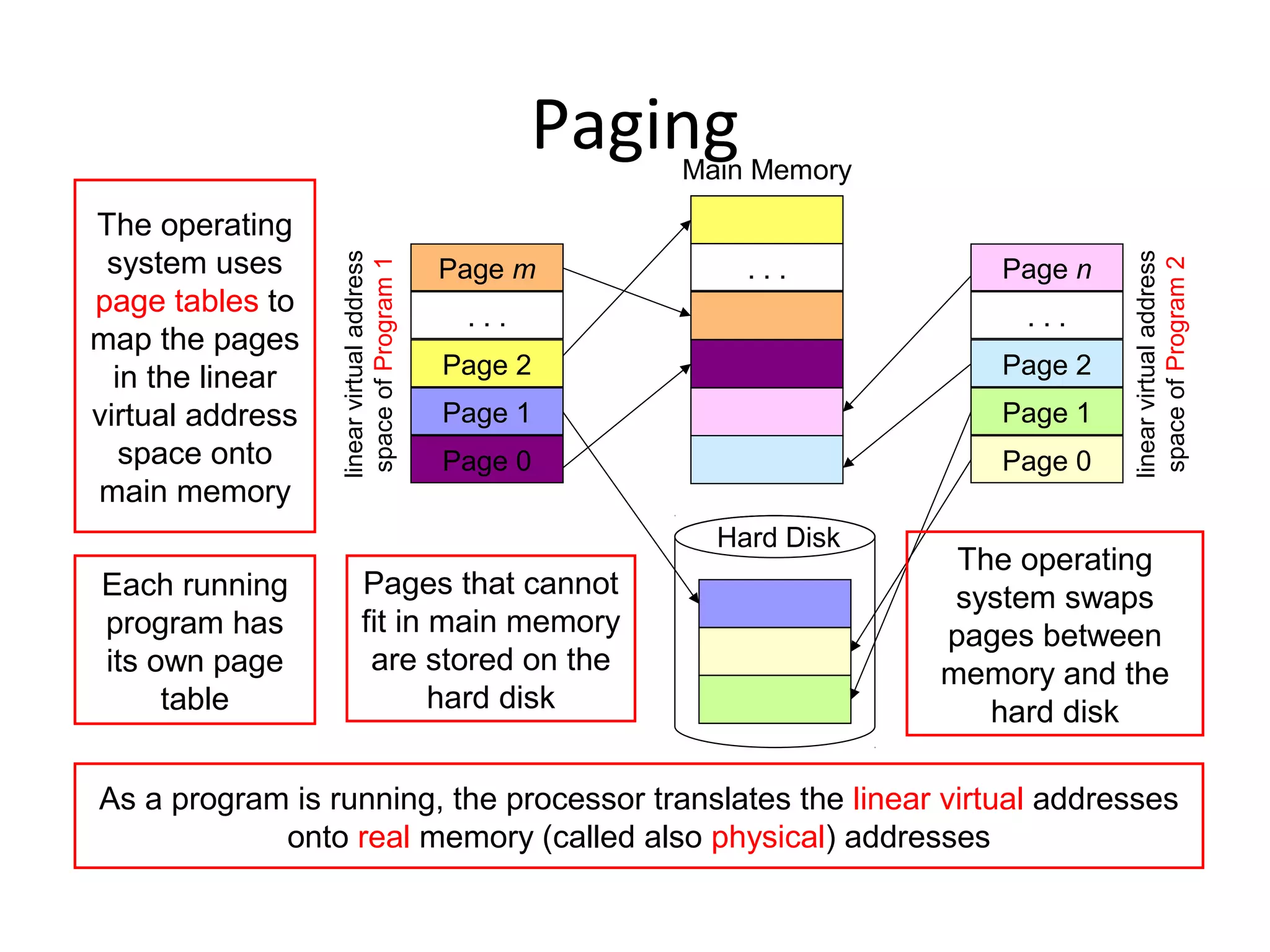

The 80386 CPU uses a two-level address translation mechanism to map logical addresses to physical addresses. It first uses segmentation to translate logical addresses to linear addresses, then uses paging to translate linear addresses to physical addresses. Paging involves using the page directory and page tables, which are stored in memory and map 4KB pages to physical addresses. The TLB cache is used to improve performance by storing recently used page table entries to avoid having to access memory for translation.