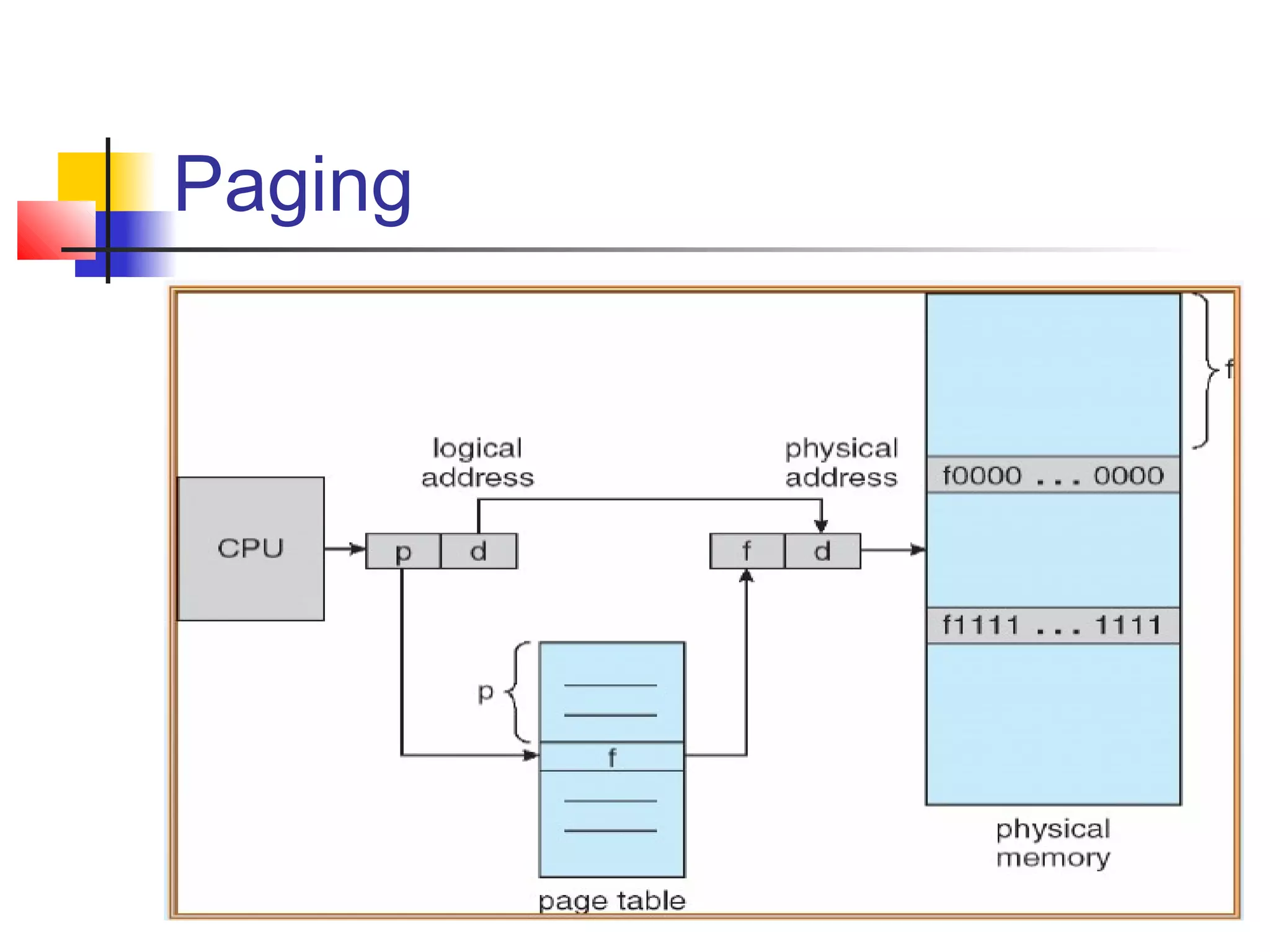

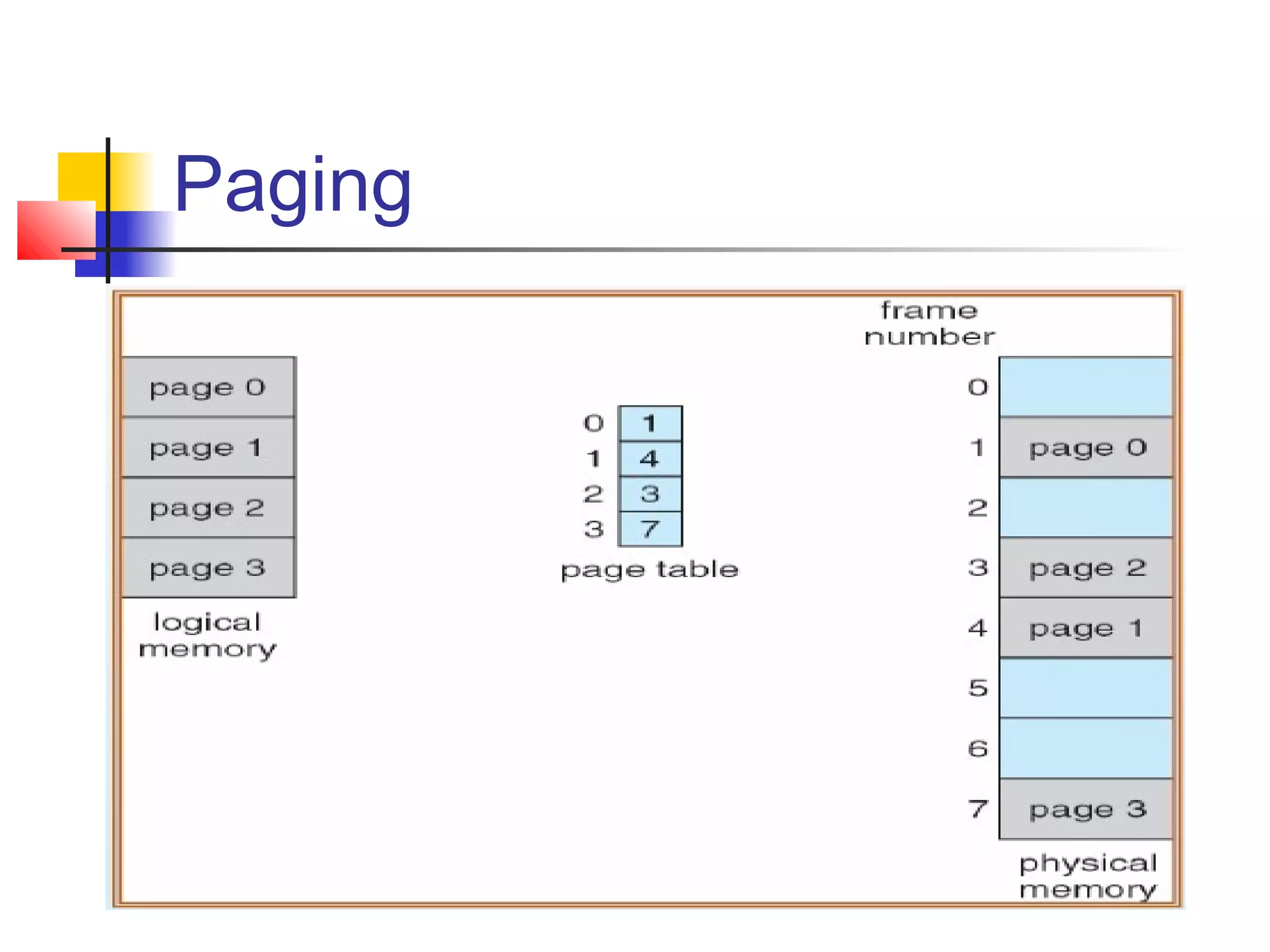

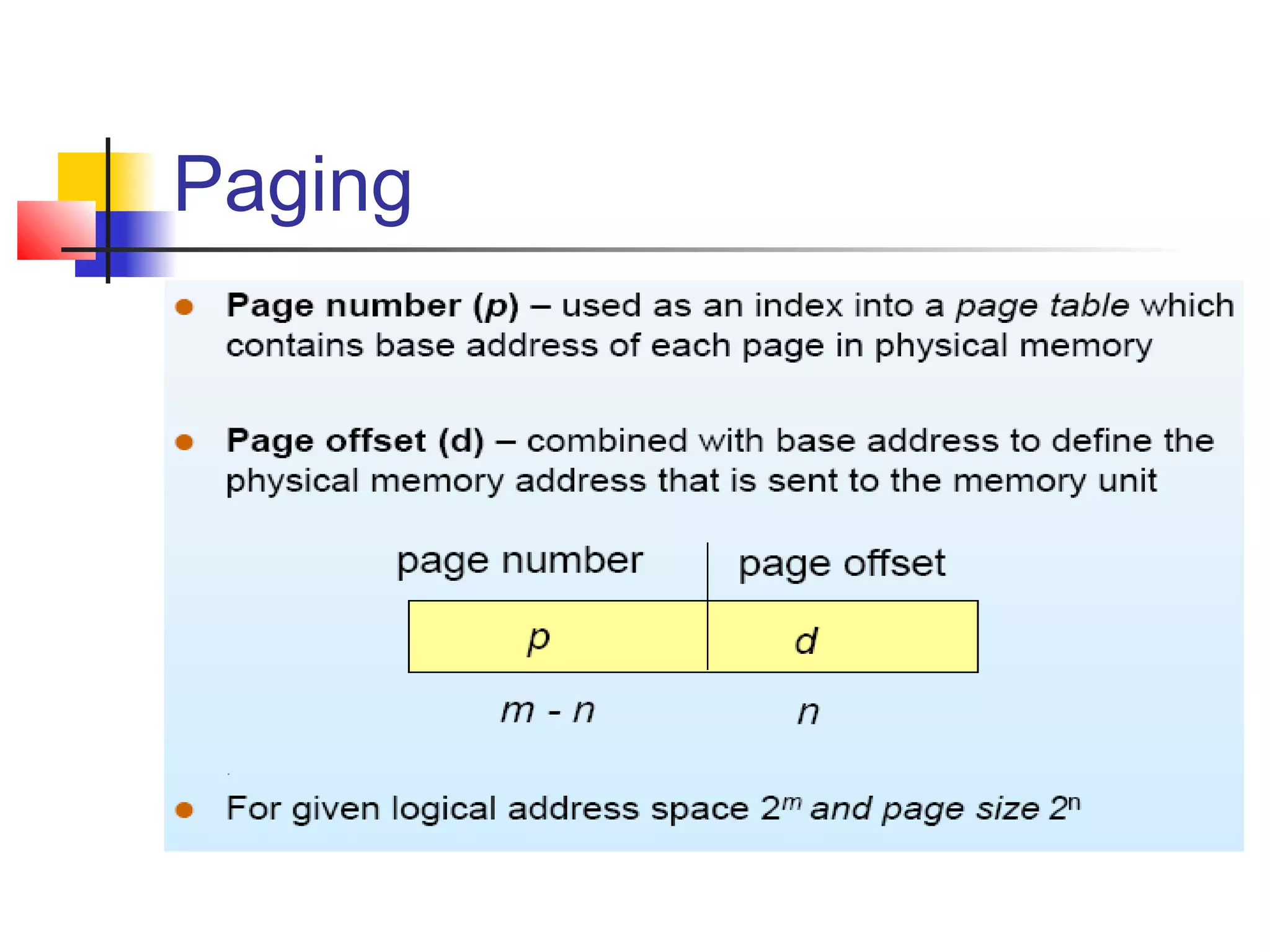

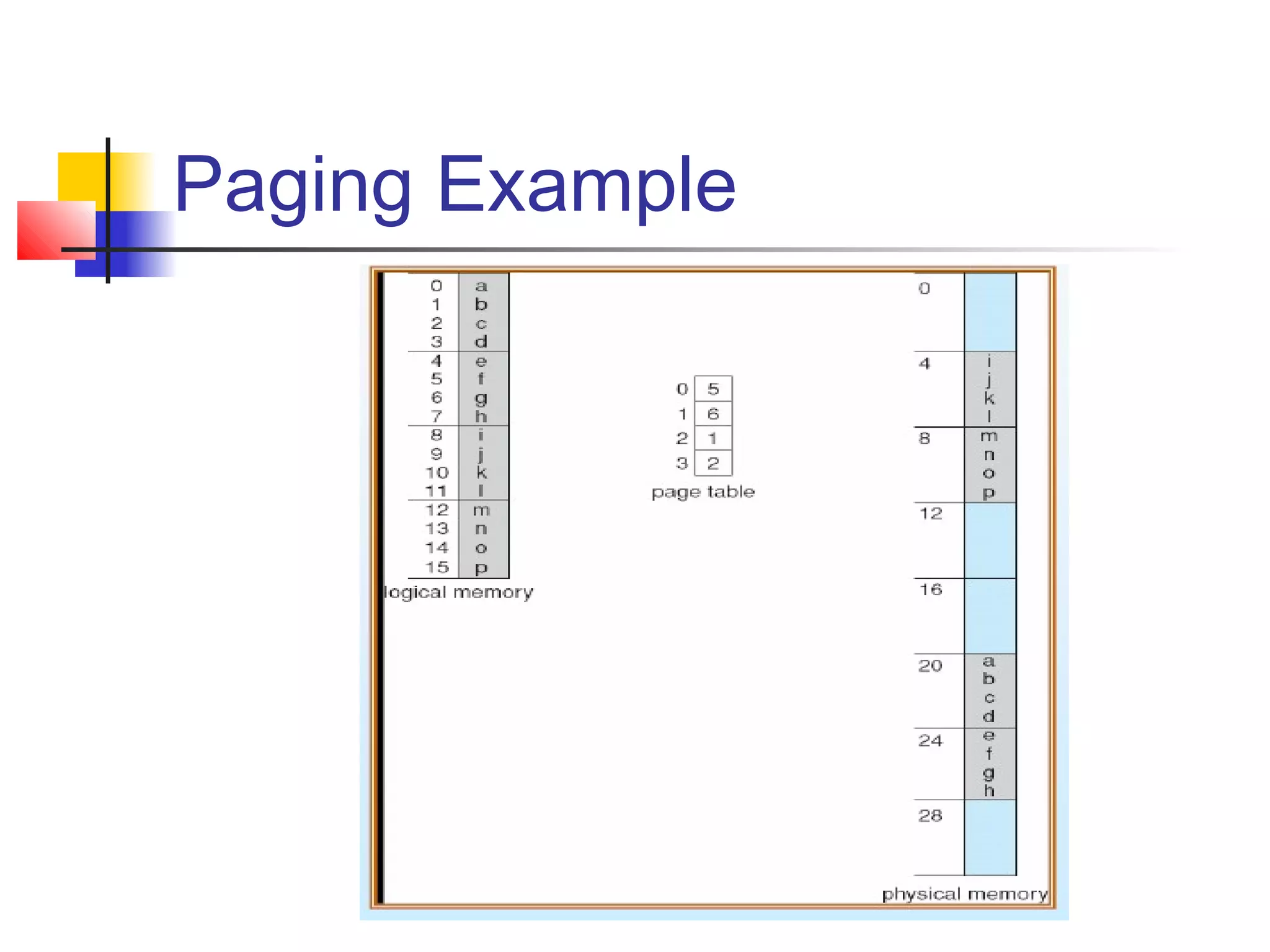

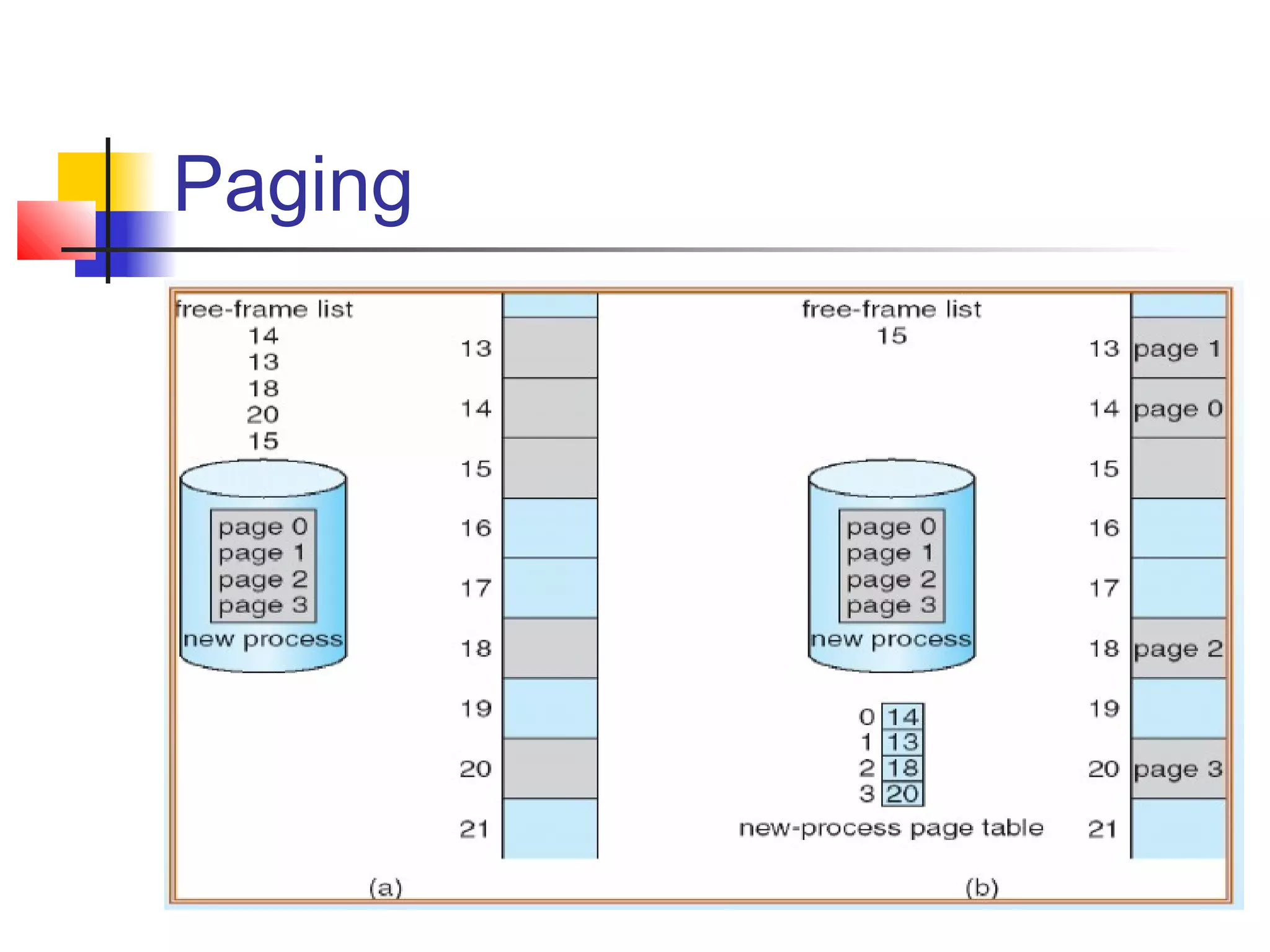

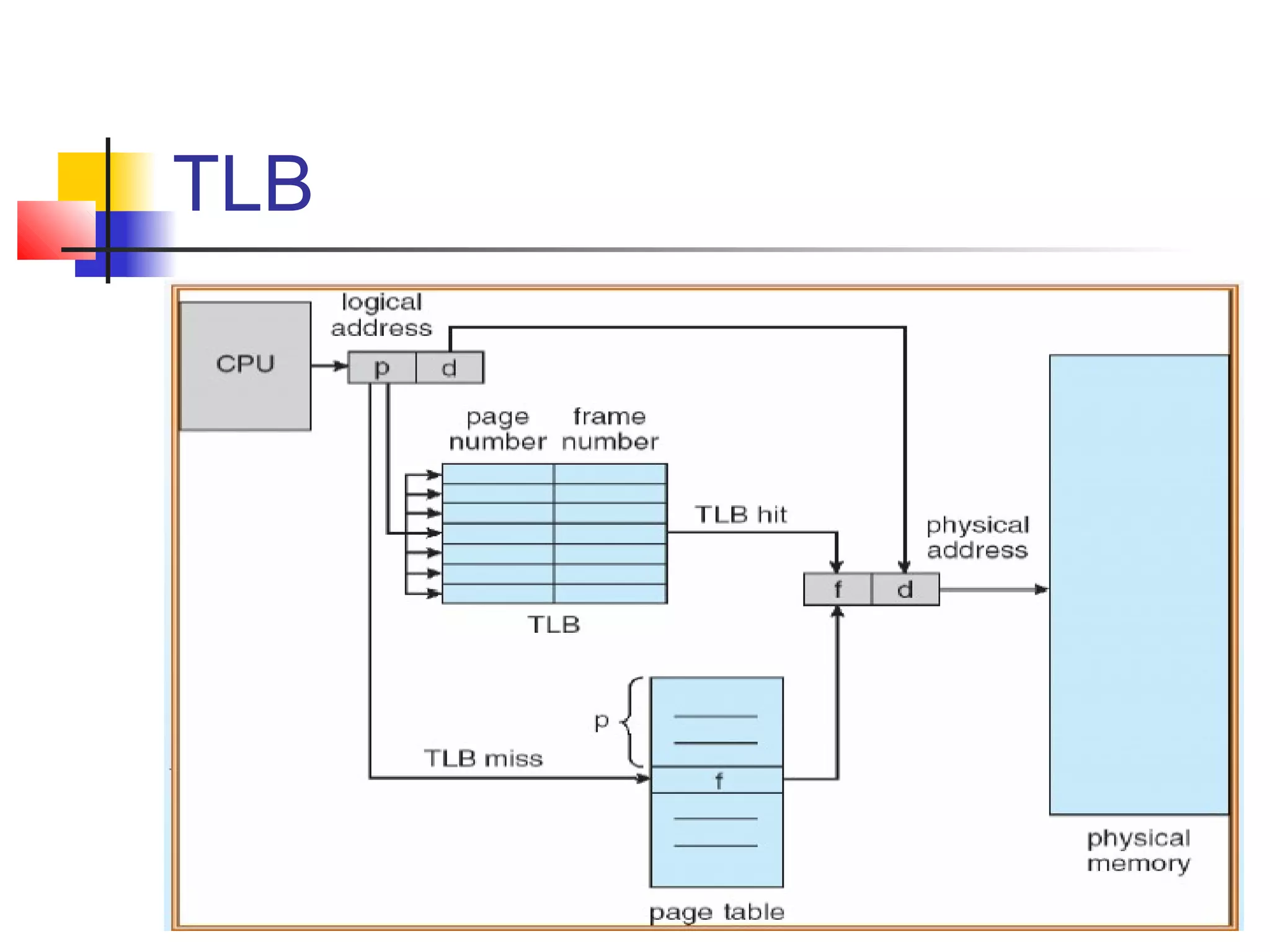

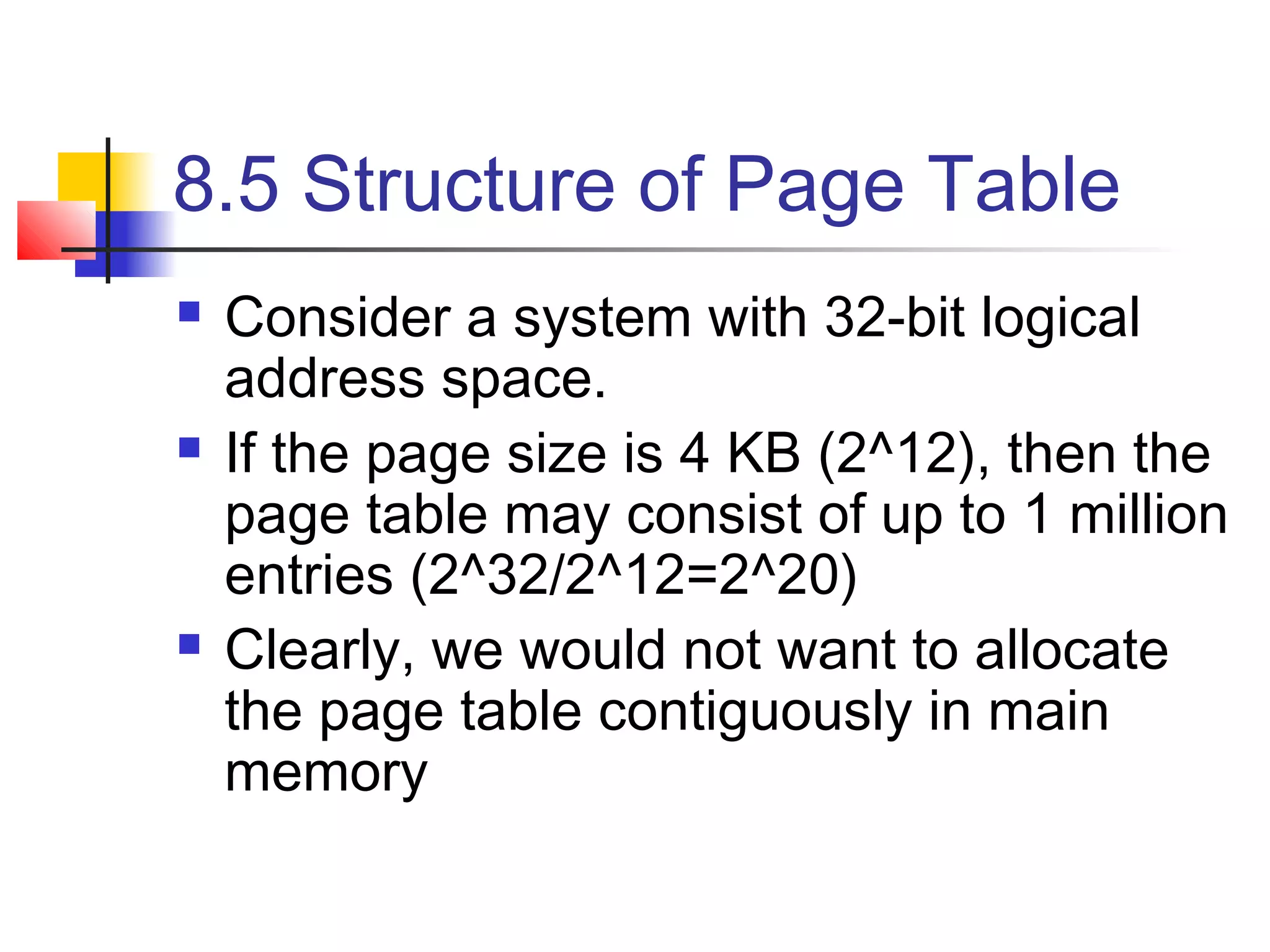

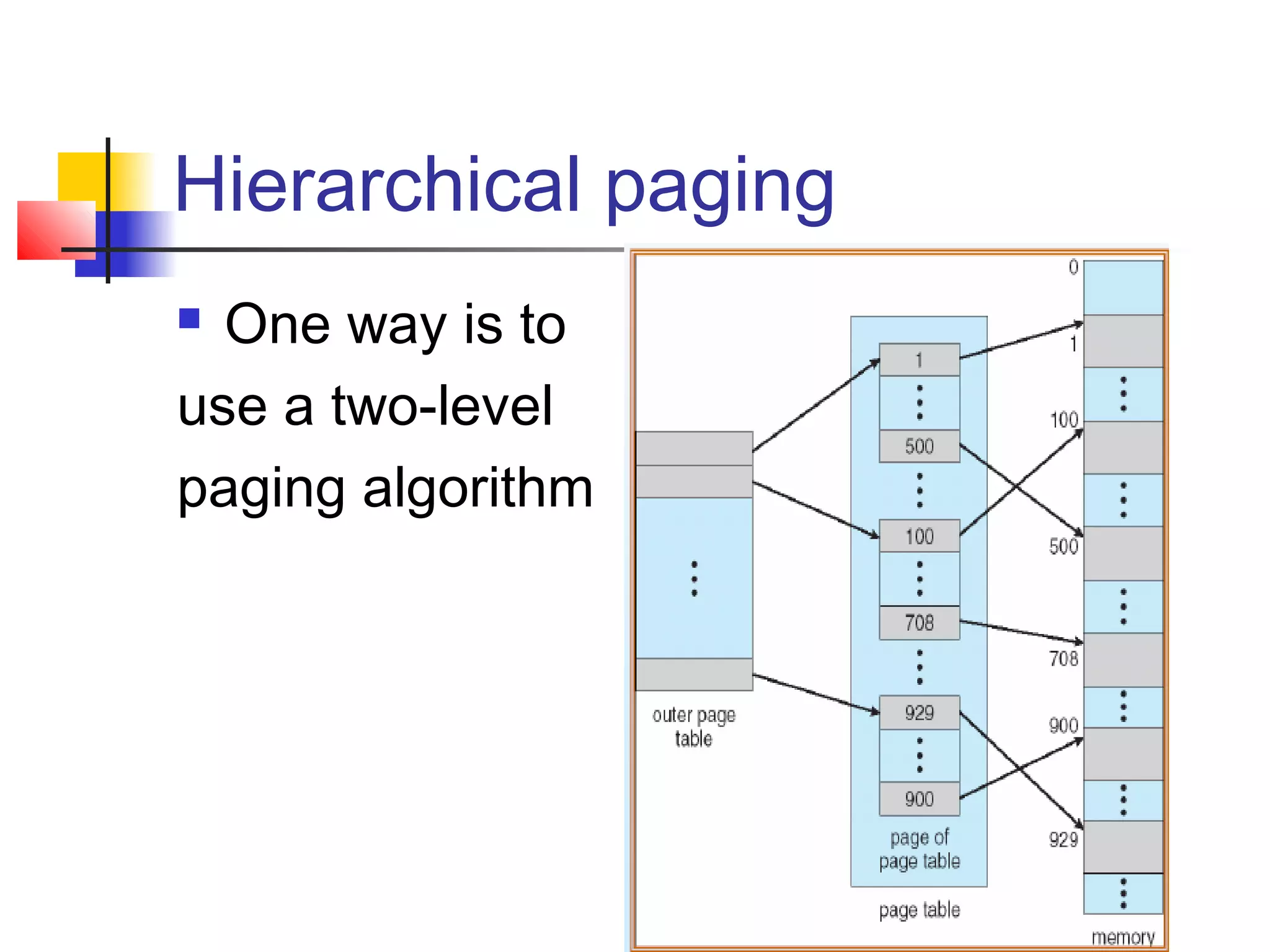

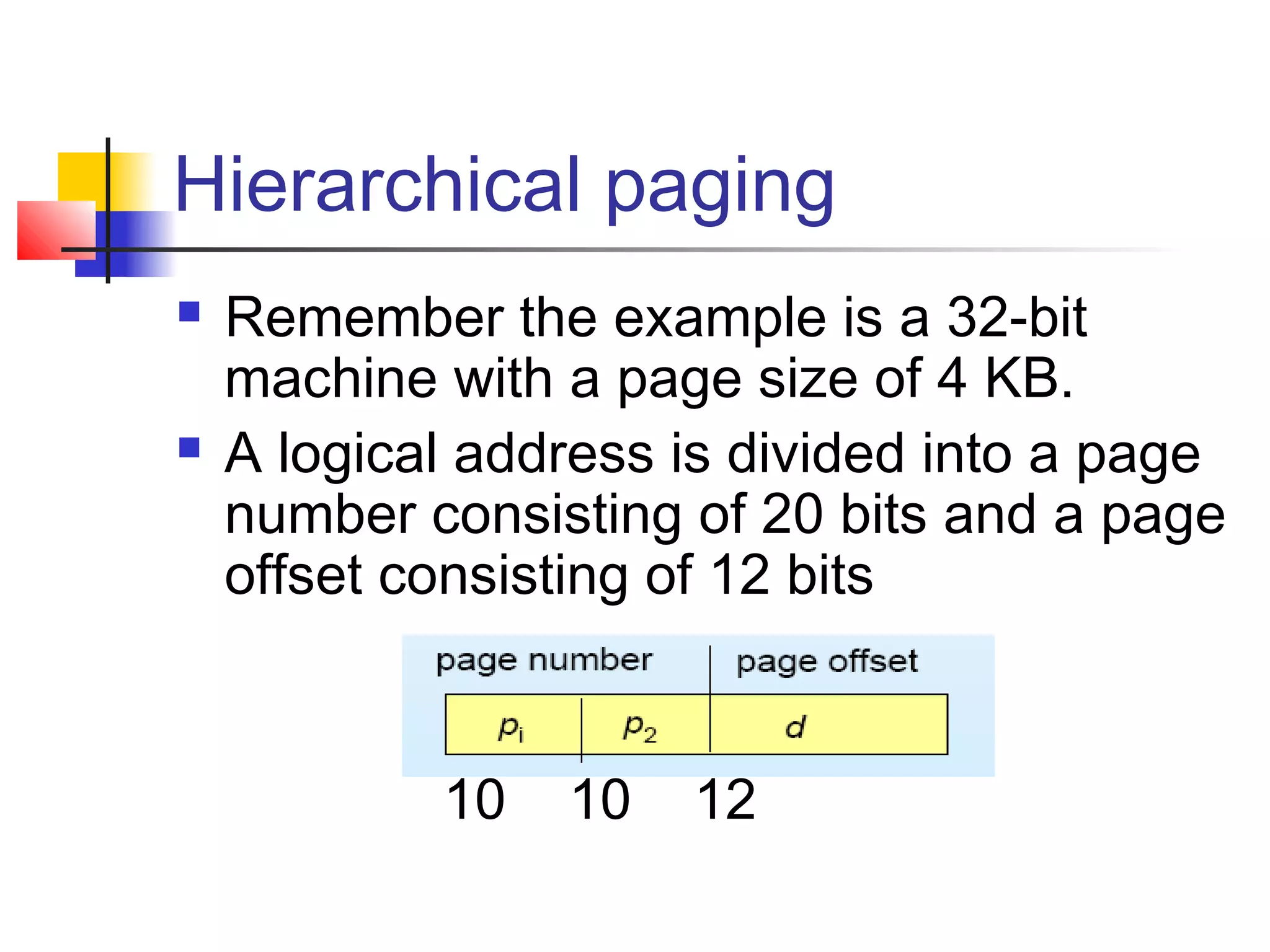

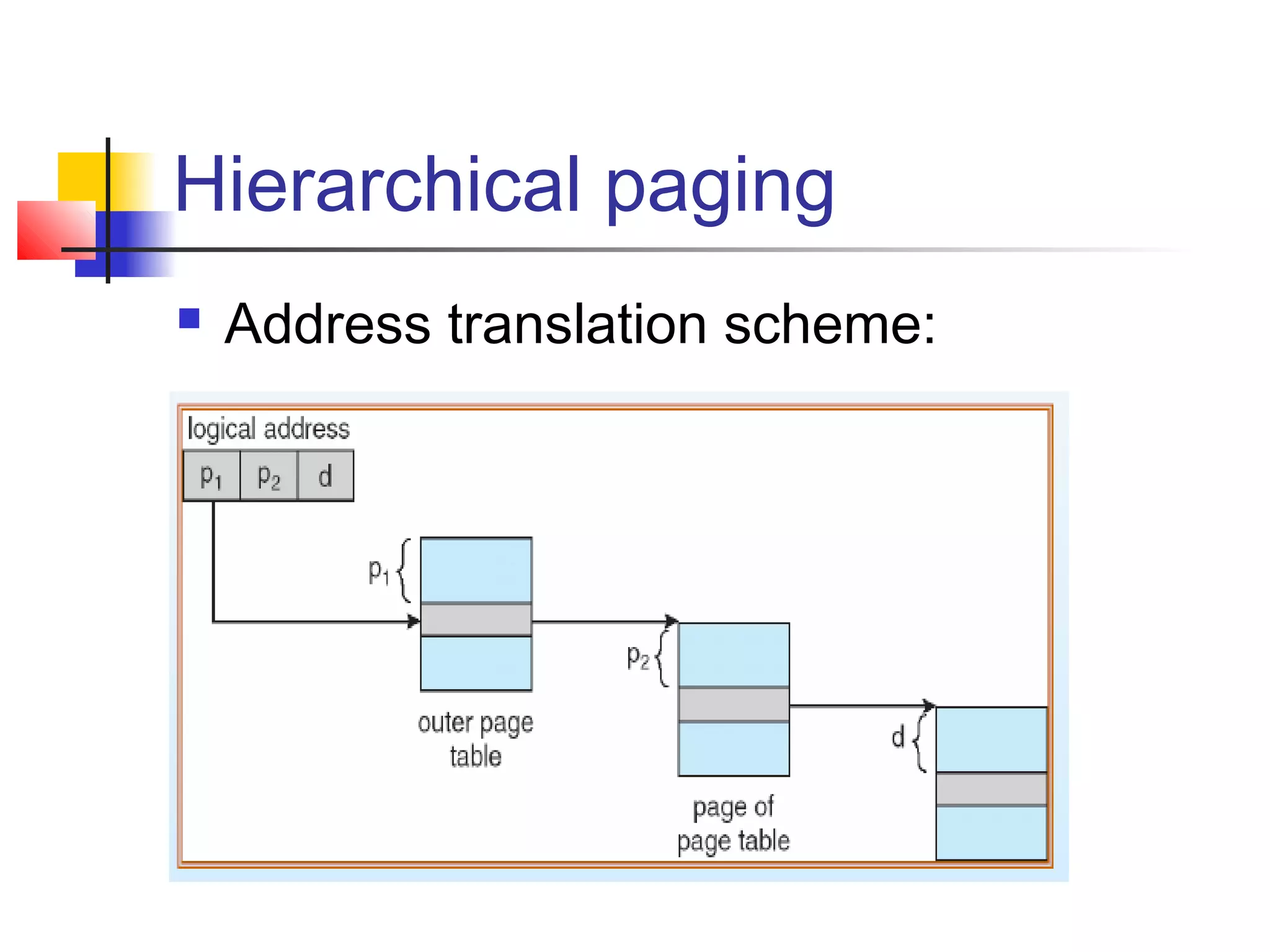

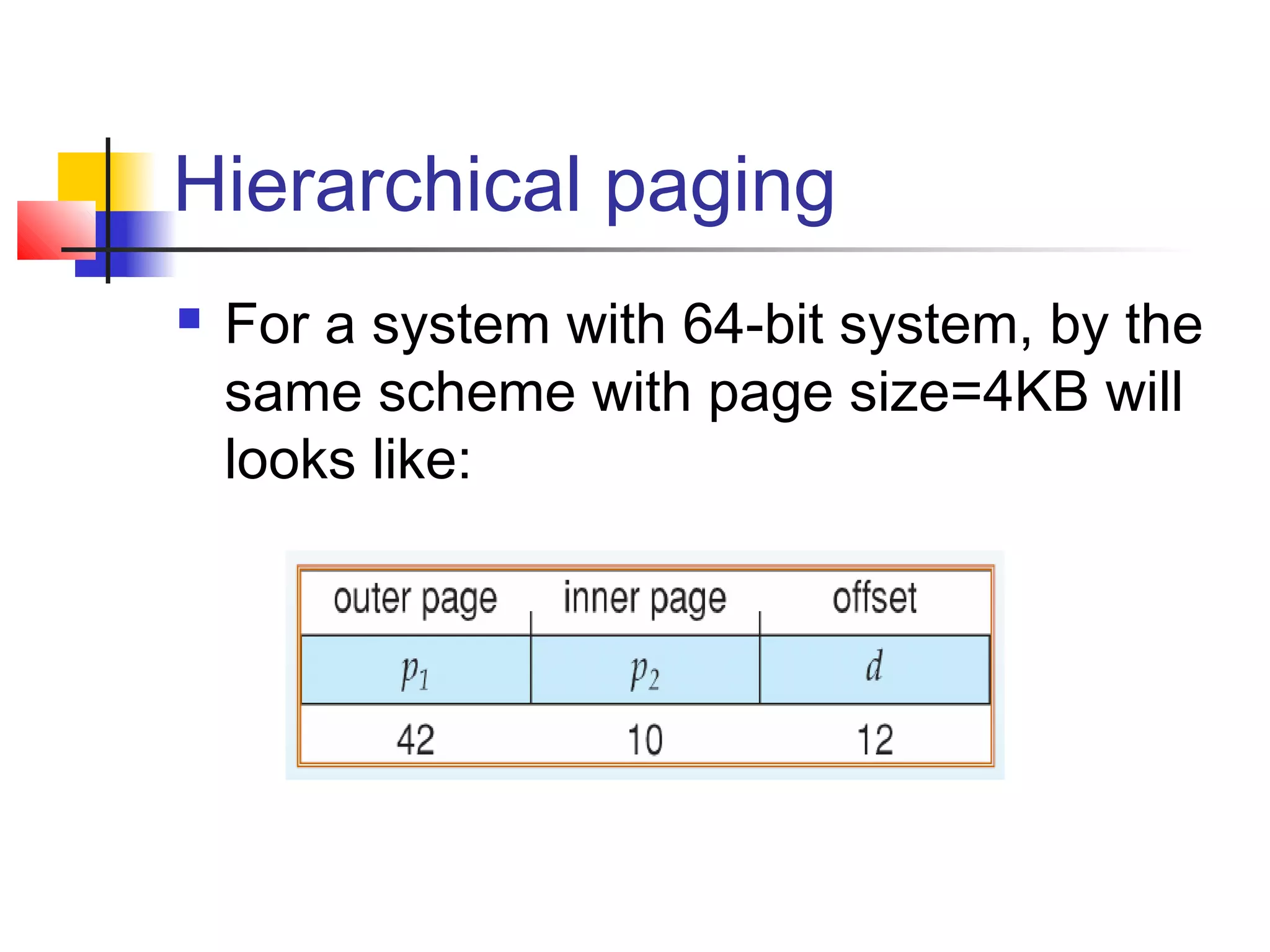

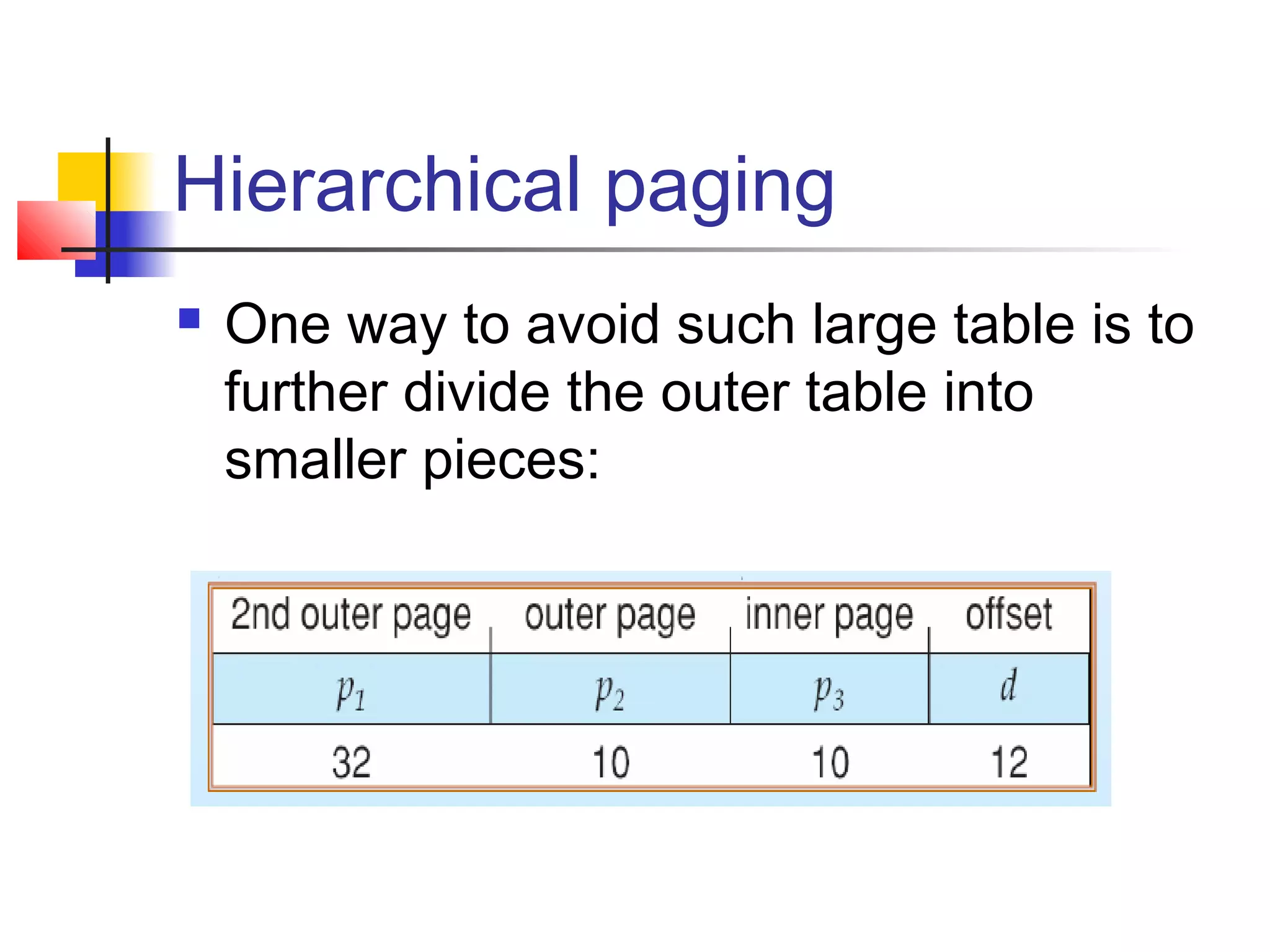

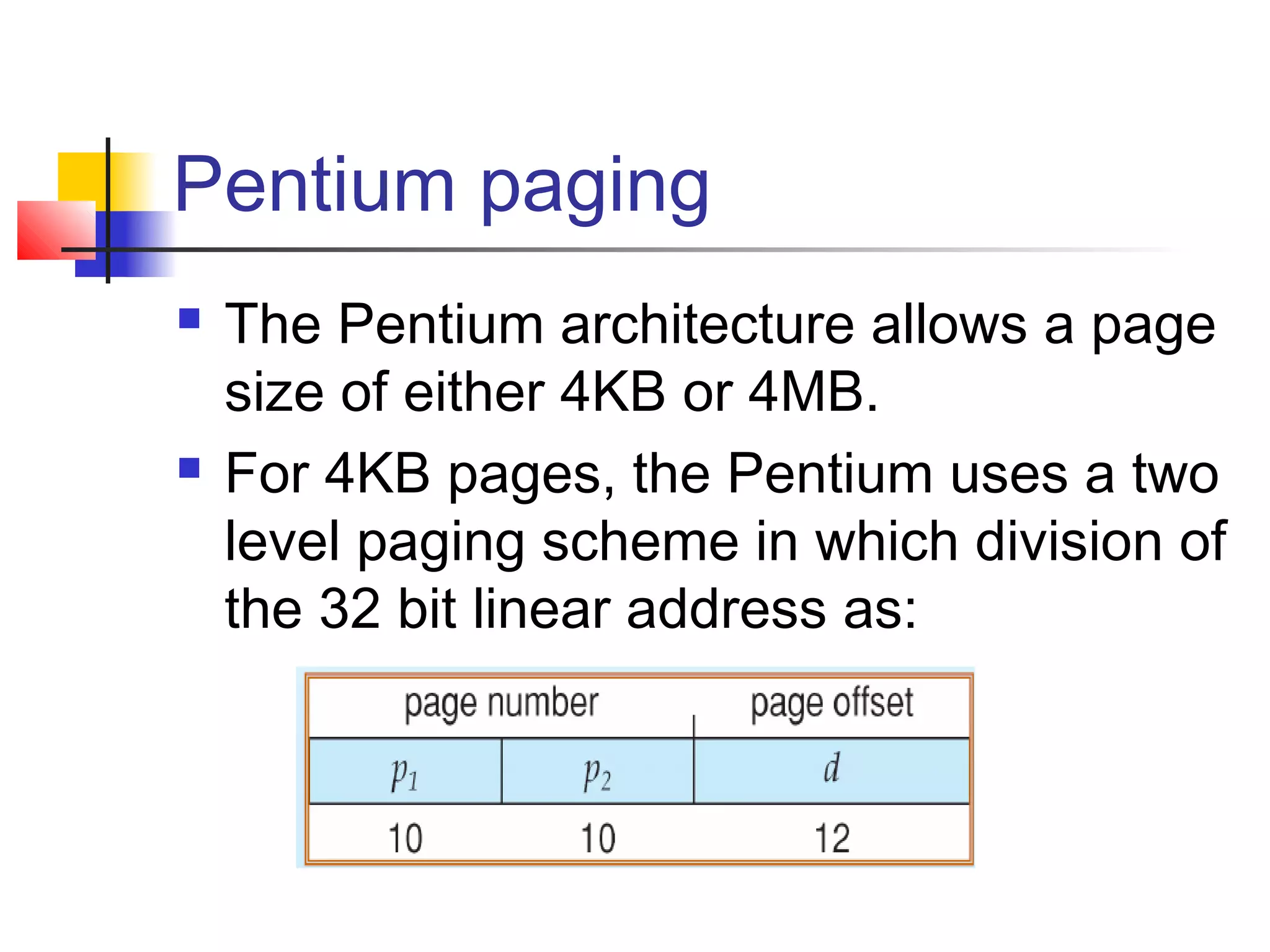

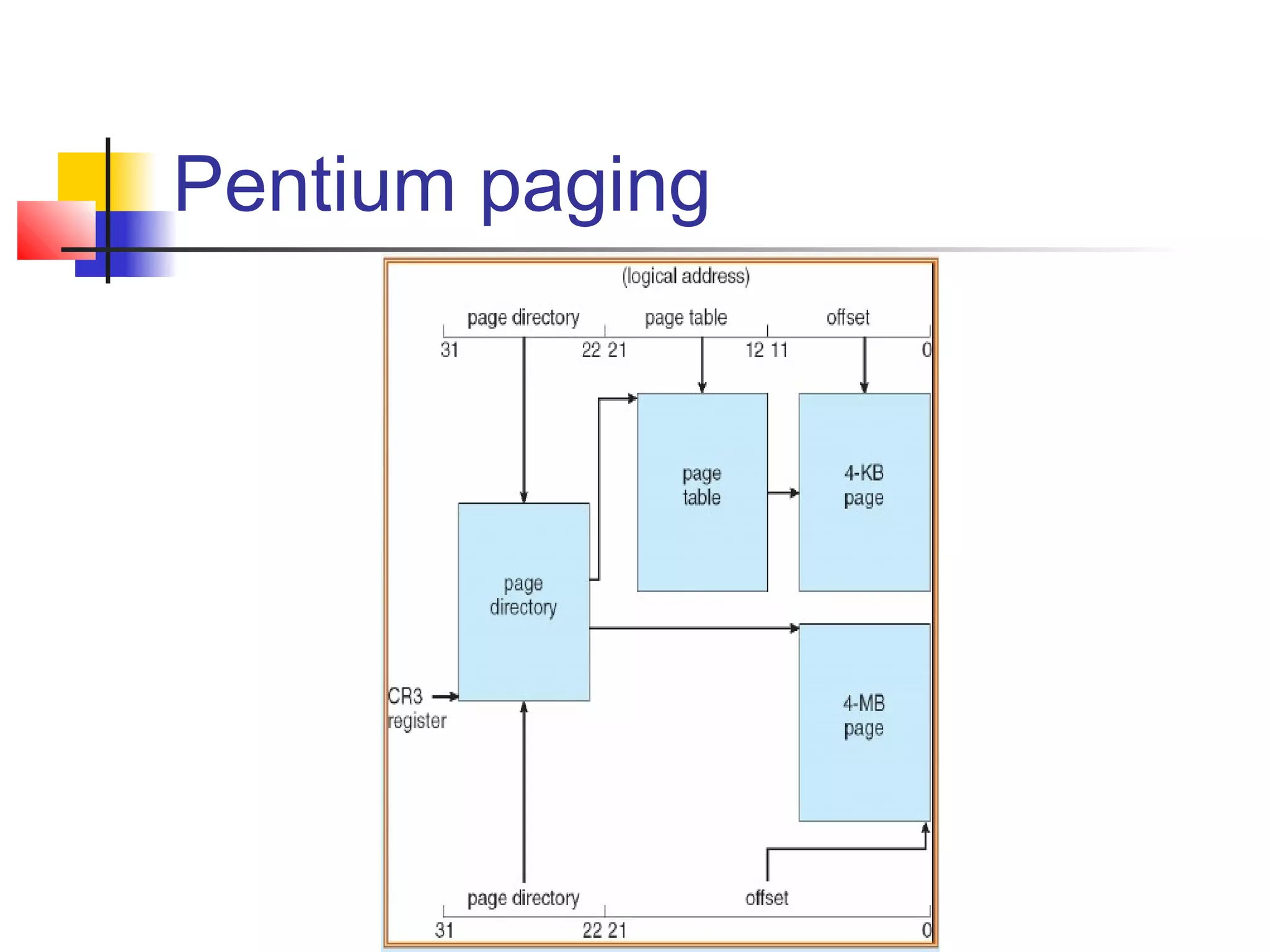

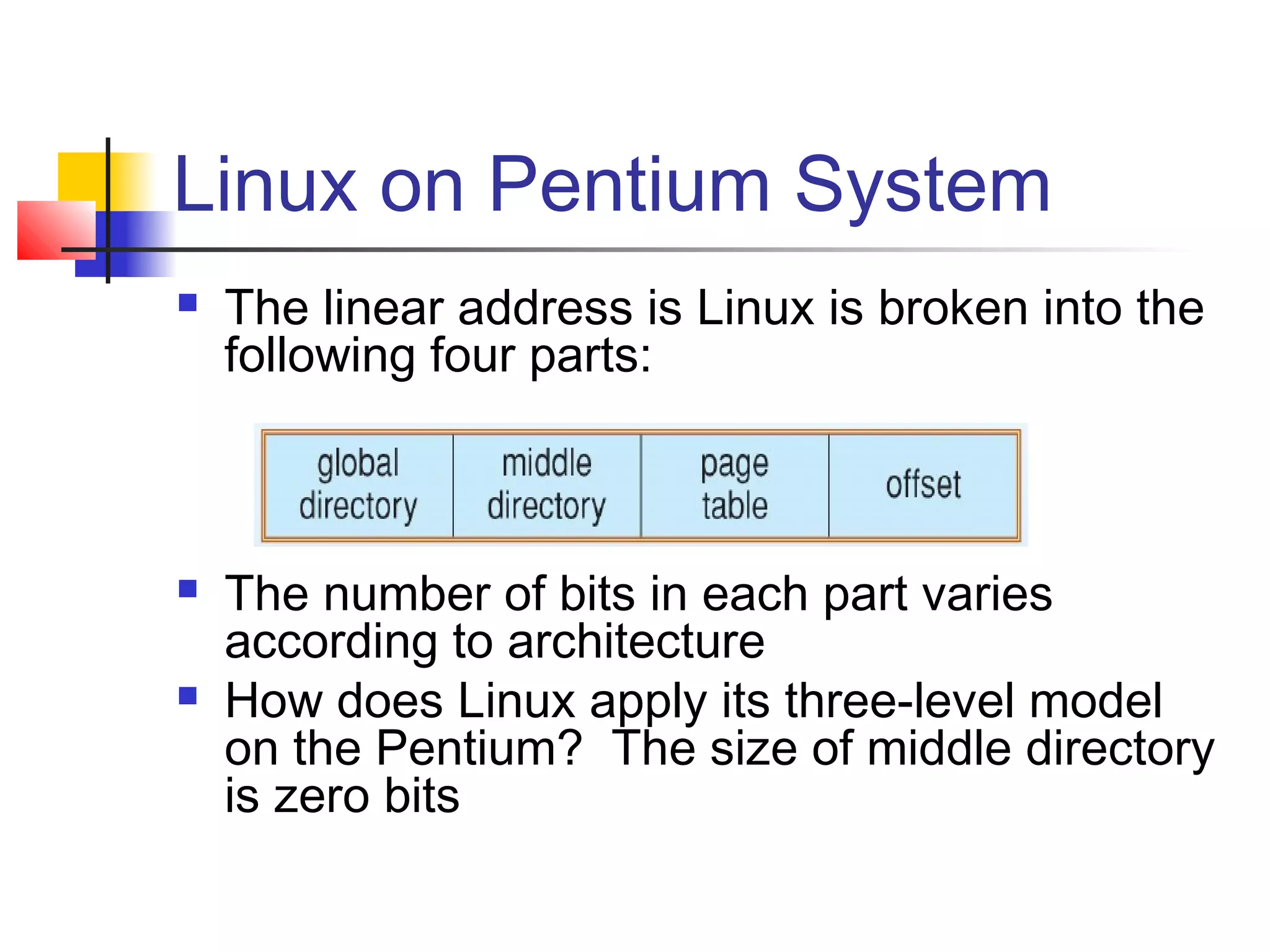

Paging is a memory management scheme that allows the physical address space of a process to be non-contiguous. The logical memory is divided into pages of a fixed size, while physical memory is divided into frames of the same size. When accessing a memory location, the CPU generates a page number and page offset. The page number is used to index into a page table stored in main memory to map the logical page to a physical frame. A Translation Lookaside Buffer (TLB) cache is used to improve performance by caching recent page table lookups.