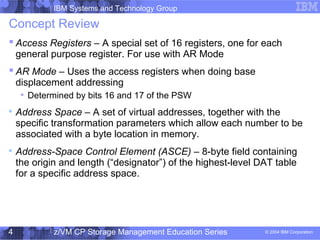

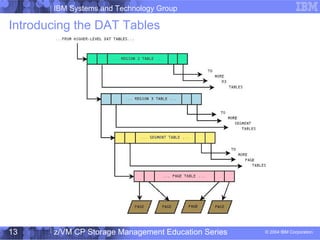

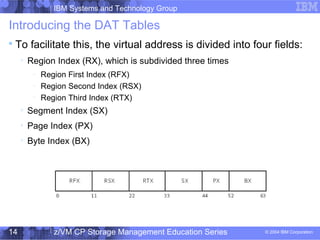

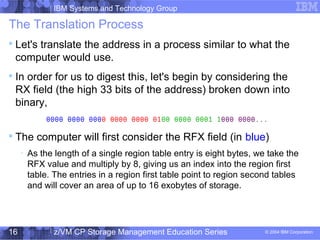

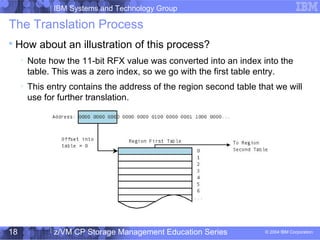

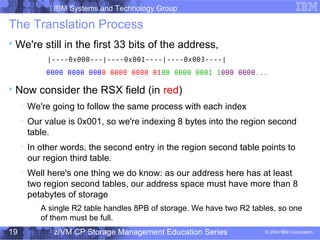

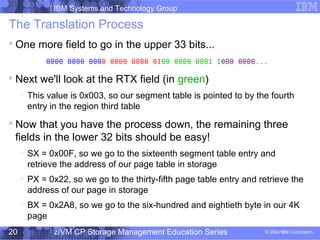

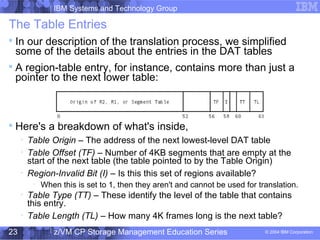

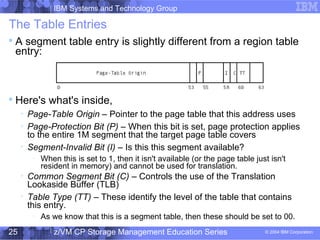

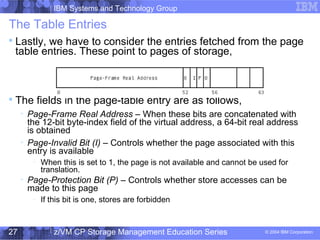

The document provides an introduction to dynamic address translation (DAT) on IBM z/Architecture systems. It begins with concept definitions related to DAT. It then explains that DAT uses a hierarchical set of tables, called DAT tables, to translate virtual addresses to real addresses. The translation process walks through the virtual address fields to index into the DAT tables at each level, starting with the region tables pointed to by the address space control element, and ending with the page table to retrieve the real address.