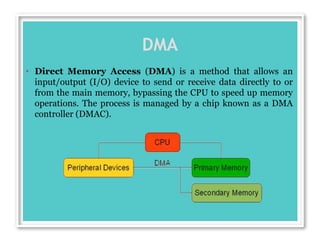

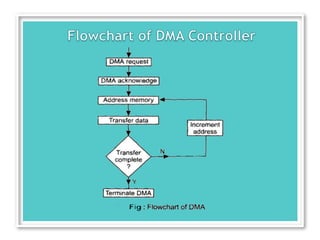

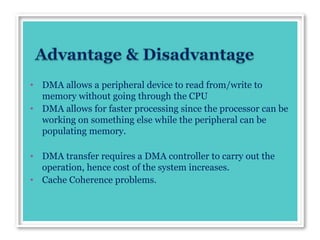

1. Direct Memory Access (DMA) allows input/output devices to directly access main memory, bypassing the CPU to speed up memory transfers. This is managed by a DMA controller.

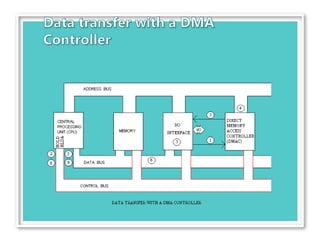

2. During a DMA transfer, the DMA controller gains control of the address bus, data bus, and control bus from the microprocessor to transfer data directly between an I/O port and memory.

3. The DMA controller has several options for transferring data, including cycle stealing for single byte transfers, burst mode for block transfers using address sequencing, and hidden DMA which occurs transparently when the CPU is not using the bus.