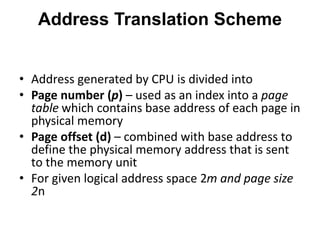

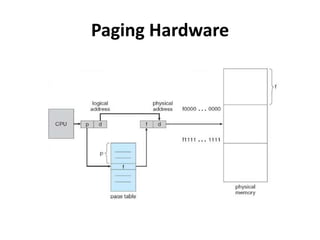

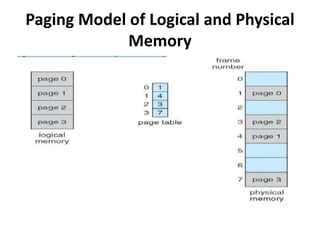

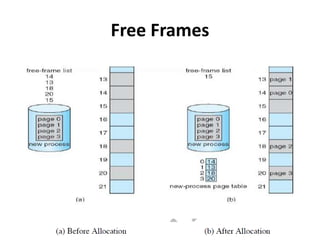

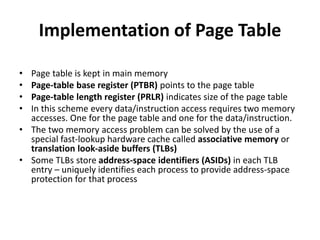

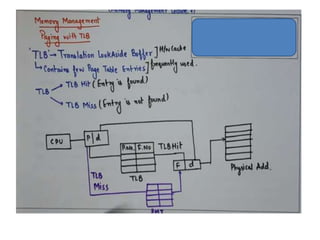

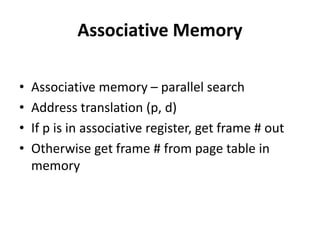

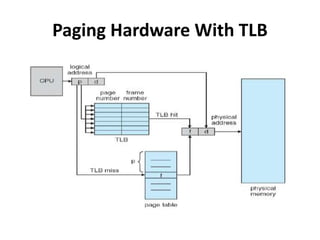

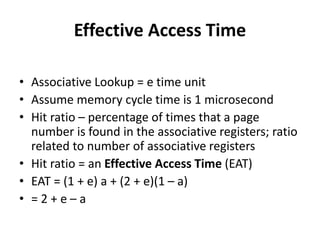

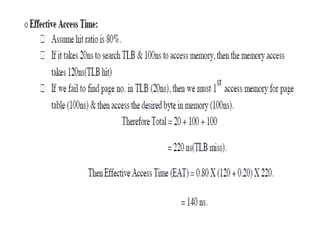

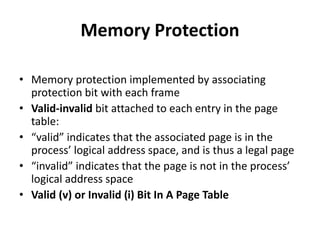

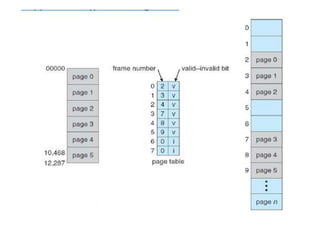

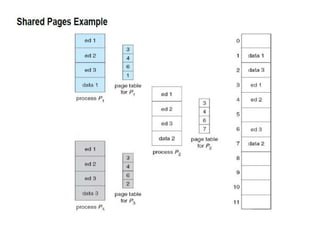

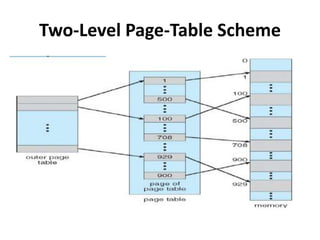

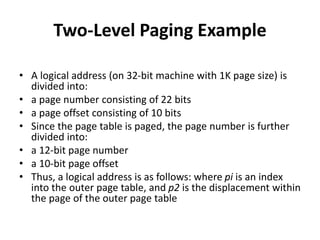

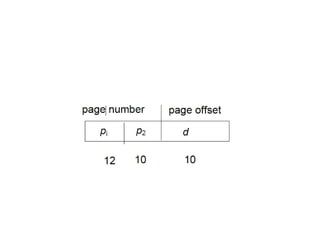

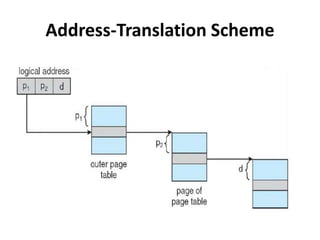

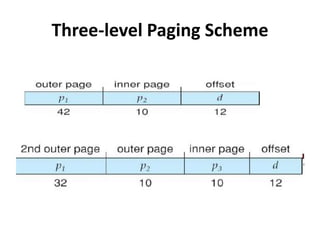

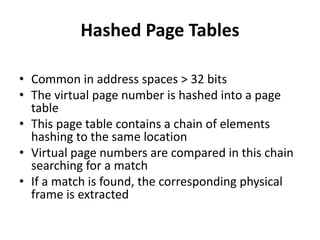

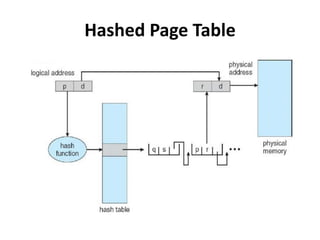

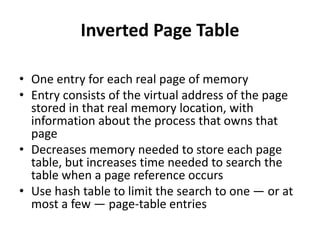

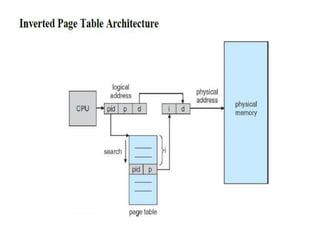

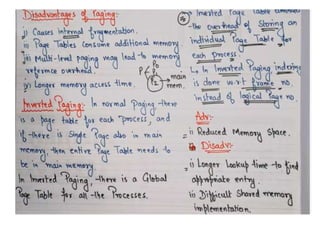

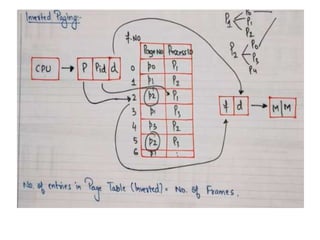

The document discusses paging concepts in memory management, explaining how logical addresses are translated into physical addresses using page tables. It covers various paging mechanisms such as hierarchical paging, hashed page tables, and inverted page tables, along with their implementations and performance considerations like effective access time and memory protection. Additionally, it addresses the challenges of multiple memory accesses and solutions using translation look-aside buffers (TLBs).