48 51

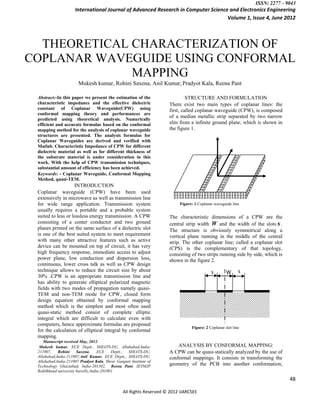

- 1. ISSN: 2277 – 9043 International Journal of Advanced Research in Computer Science and Electronics Engineering Volume 1, Issue 4, June 2012 THEORETICAL CHARACTERIZATION OF COPLANAR WAVEGUIDE USING CONFORMAL MAPPING Mukesh kumar, Rohini Saxena, Anil Kumar, Pradyot Kala, Reena Pant Abstract:-In this paper we present the estimation of the STRUCTURE AND FORMULATION characteristic impedance and the effective dielectric There exist two main types of coplanar lines: the constant of Coplanar Waveguide(CPW) using first, called coplanar waveguide (CPW), is composed conformal mapping theory and performances are of a median metallic strip separated by two narrow predicted using theoretical analysis. Numerically efficient and accurate formulae based on the conformal slits from a infinite ground plane, which is shown in mapping method for the analysis of coplanar waveguide the figure 1. structures are presented. The analysis formulas for Coplanar Waveguides are derived and verified with Matlab. Characteristic Impedance of CPW for different dielectric material as well as for different thickness of the substrate material is under consideration in this work. With the help of CPW transmission techniques, substantial amount of efficiency has been achieved. Keywords: - Coplanar Waveguide, Conformal Mapping Method, quasi-TEM. INTRODUCTION Coplanar waveguide (CPW) have been used extensively in microwave as well as transmission line for wide range application. Transmission system Figure: 1 Coplanar waveguide line usually requires a portable and a probable system suited to less or lossless energy transmission. A CPW The characteristic dimensions of a CPW are the consisting of a center conductor and two ground central strip width W and the width of the slots s . planes printed on the same surface of a dielectric slot The structure is obviously symmetrical along a is one of the best suited system to meet requirement vertical plane running in the middle of the central with many other attractive features such as active strip. The other coplanar line; called a coplanar slot device can be mounted on top of circuit, it has very (CPS) is the complementary of that topology, high frequency response, immediate access to adjust consisting of two strips running side by side, which is power plane, low conduction and dispersion loss, shown in the figure 2. continuous, lower cross talk as well as CPW design technique allows to reduce the circuit size by about s W s 30% .CPW is an appropriate transmission line and has ability to generate elliptical polarized magnetic fields with two modes of propagation namely quasi- TEM and non-TEM mode for CPW, closed form design equation obtained by conformal mapping method which is the simplest and most often used quasi-static method consist of complete elliptic integral which are difficult to calculate even with computers, hence approximate formulas are proposed Figure: 2 Coplanar slot line for the calculation of elliptical integral by conformal mapping. Manuscript received May, 2012. Mukesh kumar, ECE Deptt., SHIATS-DU, Allahabad,India- ANALYSIS BY CONFORMAL MAPPING: 211007, Rohini Saxena, ECE Deptt., SHIATS-DU, A CPW can be quasi-statically analyzed by the use of Allahabad,India-211007,Anil Kumar, ECE Deptt., SHIATS-DU, conformal mappings. It consists in transforming the Allahabad,India-211007 Pradyot Kala, Shree Ganpati Institute of Technology Ghaziabad, India-201302, Reena Pant, IETMJP geometry of the PCB into another conformation, Rohilkhand university bareilly,India-201001 48 All Rights Reserved © 2012 IJARCSEE

- 2. ISSN: 2277 – 9043 International Journal of Advanced Research in Computer Science and Electronics Engineering Volume 1, Issue 4, June 2012 whose properties make the computations r 1 straightforward. re (3) 2 z dz and the impedance: w 30 K ' k1 z0 z W 2 z W 2 2 Z (4) re K k1 W/2 s A B C D Figure: 4 Parallel plate capacitor filled Figure: 3 Infinitely deep substrate of CPW with dielectric substrate The CPW of negligible thickness located on top of an In practical cases, the substrate has a finite thickness infinitely deep substrate, as shown in the Figure 3, h Figure 4. To carry out the analysis of this can be mapped into a parallel plate capacitor filled conformation, a preliminary conformal mapping with dielectric ABCD using the conformal function transforms the finite thickness dielectric into an as shown in the Figure 4.To further simplify the infinite thickness one Figure 3. Only the effective analysis, the original dielectric boundary is assumed permittivity is altered, it becomes: to constitute a magnetic wall, so that BC and AD r 1 K k 2 K ' k 1 become magnetic walls too and there is no resulting fringing field in the resulting capacitor. With that re 1 ' K k 2 K k 1 assumption, the capacitance per unit length is merely (5) 2 the sum of the top (air filled) and bottom (dielectric filled) partial capacitances. Capacitance of dielectric Finally, let us consider a CPW over a finite thickness filled bottom of the substrate and the dielectric backed by an infinite ground plane. In this case, the quasi-TEM wave is a hybrid between capacitance of top of the substrate is given by microstrip and true CPW mode. The equations then the formula: become: K k1 re 1 q r 1 Cd 2 0 R (6) K ' k1 (1) Where q , called filling factor.The impedance of this K k 1 line amounts to: Ca 2 0 K ' k 1 (2) 60 1 In both formulae K k and K k represent the ' Z re K k 1 K k 3 (7) K ; k 1 K ' k 3 complete elliptic integral of the first kind and its W complement, and k1 ' .with k being the W 2s RESULTS & DISCUSSION complementary modulus: k 1 k . Where ' 2 the accuracy of the above formulae is close a) CHARACTERISTIC IMPEDANCE Vs 5 6 NORMALIZED STRIP WIDTH FOR DIFFERENT to 10 to 3 10 . It can be considered as exact DIELECTRIC MATERIALS OF CPW: for any practical purposes. The total line capacitance 1.1 For Infinite Substrate Thickness is thus the sum of C d and C a . The effective It is observed that the characteristic impedance of permittivity is therefore: CPW decreases as normalized strip width increases. 49 All Rights Reserved © 2012 IJARCSEE

- 3. ISSN: 2277 – 9043 International Journal of Advanced Research in Computer Science and Electronics Engineering Volume 1, Issue 4, June 2012 air=1 quartz=3.78 alumina=9.5 be at negative potential or grounded to complete the 300 circuitry. As for finite and infinite substrate thickness shielding for different dielectric materials are not 250 Characteristic impedance in ohm possible because dielectric or air can never be 200 grounded. As the shielded plate is grounded the 150 central strip occupies higher potential and eventually 100 can hold more energy. Hence loss will be reduced 50 and from all the graphs discussed earlier, characteristic impedance of CPW changes which is a 0 0.1 1 10 proof for above mention postulates. Normalize d strip width (W/s) in mm When alumina is used as dielectric material Graph 1.1: characteristic impedance Vs normalized strip width. whose relative permittivity is equal to 9.5 for infinite thickness, finite thickness and ground shielded of 1.2 For Finite Substrate Thickness CPW, the electric field between central strip line and ground plane becomes more and more dominant as compared to dielectric material with lower air=1 quartz=3.78 alumina=9.5 permittivity, which means there will be an increase in 300 displacement current also called leakage current from central strip to ground plane. With large leakage Characteristic impedance in ohm 250 200 current, conductance increases which eventually 150 corresponds into a decrement of characteristic impedance. 100 The characteristic impedance of any type of 50 transmission line decreases with increase in relative 0 0.1 1 10 permittivity and can be expressed by using formula Normalize d strip width (W/s) in mm from transmission line is given by Graph 1.2: characteristic impedance Vs normalized strip width. R jL Z0 G jC 1.3 For Ground plane shielded Hence it is observed that the graph 1.3 for alumina is Where is R Resistance per unit length, L more linear as compared for air and quartz. Inductance per unit length, G Conductance per air=1 quartz=3.78 alumina=9.5 unit length, C Capacitance per unit length 600 Form the above mention formula, the condition arises R C L G for distortion less transmission Characteristic impedance in ohm 500 400 line. Since there is no wires or long conducting 300 element L and G cannot be changed so it is very 200 evident from the above condition that only R and 100 C can be inversely proportional to each other as C 0 is dependent on relative permittivity and R can be 0.1 1 10 treated as characteristic impedance it can be knuckled Normalize d strip width (W/s) in mm with the fact that whenever C increases R Graph 1.3: characteristic impedance Vs normalized strip width. decreases. It is also observed that in the entire above graph, if Shielding is a technique due to which losses the width of slot is fixed, then large normalized strip in CPW is reduced. CPW provides other means for width means less strip width. It is cleared that that the electric field to complete the path which produces characteristic impedance of CPW decreases as re- and additional capacitance between central strip and reduce the strip width which is due to strong electric metallic plate. As the capacitance is in parallel with field between central strip and ground. the original capacitance, the total capacitance of the CPW surface will increase. The main objective of a CONCLUSION waveguide is to transmit total energy at feed to Work has been done to demonstrate the utility of antenna without any loss. We can perform this action CPW and its advantages especially when energy is to in CPW with the help of shielding. To feed the be transferred from feed to antenna in a very compact energy in CPW the outer jacket of coaxial cable must 50 All Rights Reserved © 2012 IJARCSEE

- 4. ISSN: 2277 – 9043 International Journal of Advanced Research in Computer Science and Electronics Engineering Volume 1, Issue 4, June 2012 and efficient form. A simple and inexpensive method also known as quasi-static conformal mapping theory has been applied for calculating the characteristic impedance of CPW. Variation of characteristic impedance with normalized strip width due to change in different substrate thickness, different dielectric materials and metallization effect is also represented. It has been observed that characteristic impedance decreases with advancement of normalized strip width and increases for increasing dielectric substrate thickness. The reason for this observation is that, the characteristic impedance decreases when ever permittivity of dielectric substrate increases. This property can be applied in microwave transmission theory to design different antenna models for different purposes along with the advantage of mounting active and passive component on the same plane. REFERENCES [1] Gevorgian S, Linner LJP and Kollberg EL(1995), CAD models for Shielded multilayered CPW. IEEE Trans. Microwave Theory Tech.43, 326-334. [2] Wen CP(1969) Coplanar waveguide: a surface strip transmission line suitable for non-recirocal gyro magnetic device applications, IEEE Trans. Microwave Theory Tech. MTT-17, 1087- 1090 [3] K. C. Gupta, R. Garg, I. J. Bahl, and P. Bhartia, Microstrip Lines and Slotlines, 2nd ed.Artech House, Inc., 1996. pp. 375 [4] Microstrip Characteristic Impedance,'' IEEE Transactions on Microwave Theory and Techniques, vol. 27, no. 5, p. 293, Apr. 1979. [5] H. A. Wheeler, ``Transmission-Line Properties of Parallel Wide Strips by a Conformal-Mapping Approximation,'' IEEE Transactions on Microwave Theory and Techniques, vol. 12, no. 3, pp. 280-289, May 1964. [6] S. S. Bedair and I. Wolff, ``Fast, Accurate and Simple Approximate Analytic Formulas for Calculating the Parameters of Supported Coplanar Waveguides for (M)MIC's,'' IEEE Transactions on Microwave Theory and Techniques, vol. 40, no. 1, pp. 41-48, Jan. 1992. [7] M. V. Schneider, ``Microstrip Lines for Microwave Integrated Circuits,'' The Bell System Technical Journal, vol. 48, pp. 1421-1444, May 1969. [8] E. Hammerstad and Ø. Jensen, ``Accurate Models for Microstrip Computer-Aided Design,'' Symposium on Microwave Theory and Techniques, pp. 407-409, June 1980. [9] E. Hammerstad, ``Computer-Aided Design of Microstrip Couplers with Accurate Discontinuity Models,'' Symposium on Microwave Theory and Techniques, pp. 54-56, June 1981. 51 All Rights Reserved © 2012 IJARCSEE