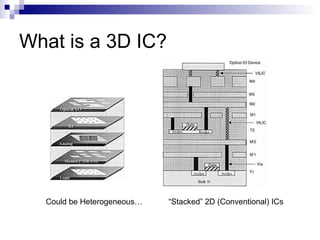

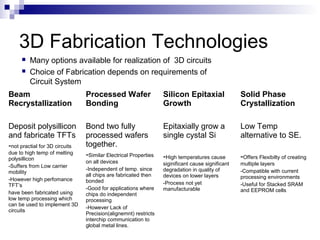

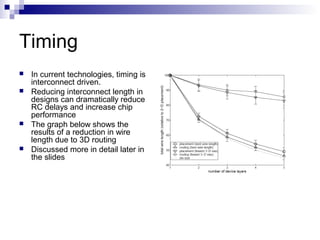

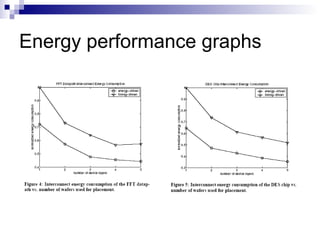

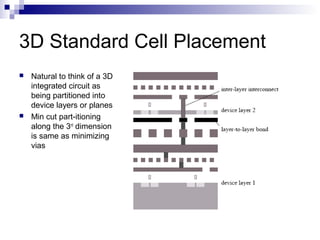

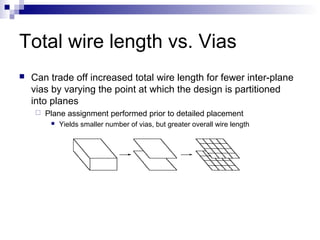

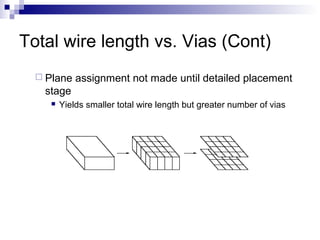

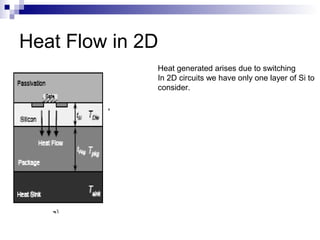

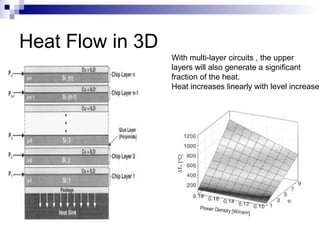

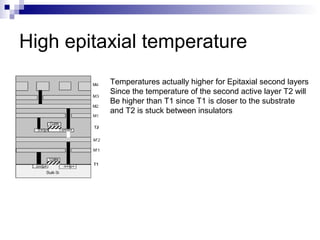

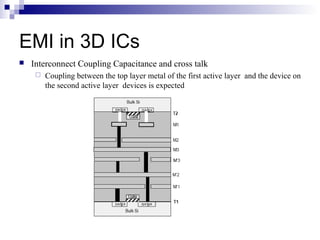

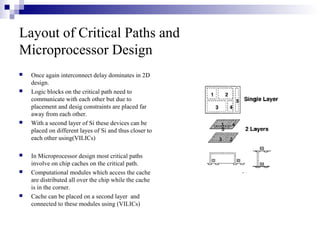

3D IC technology stacks multiple silicon layers vertically using through-silicon vias to connect the layers. This reduces wire lengths and interconnect delays which are becoming a dominant factor in chip performance. Challenges include thermal issues due to increased power density, electromagnetic interference, and reliability concerns between layers. Design tools are needed to take advantage of 3D architectures for applications like placing critical logic on separate layers to reduce delays.