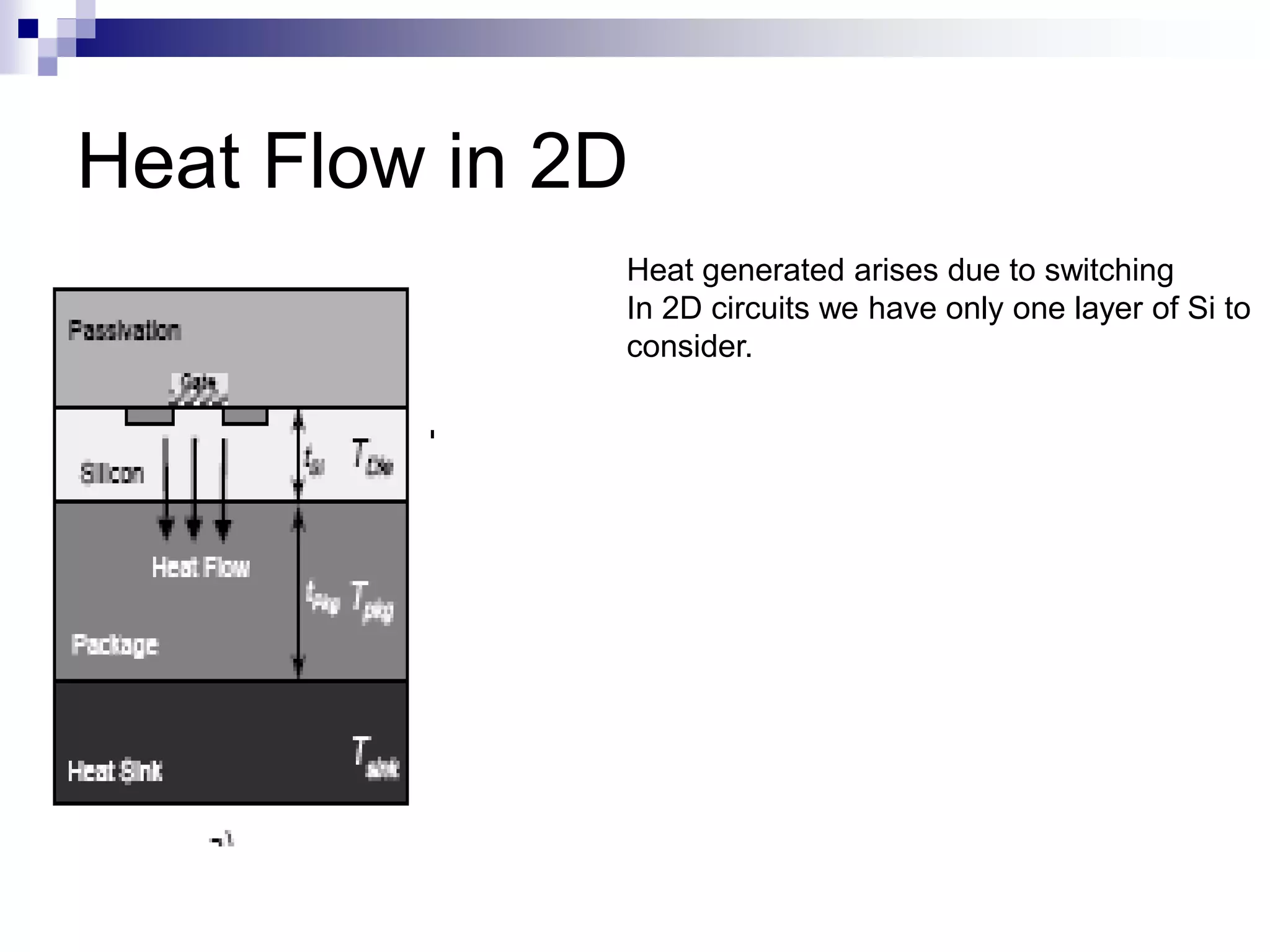

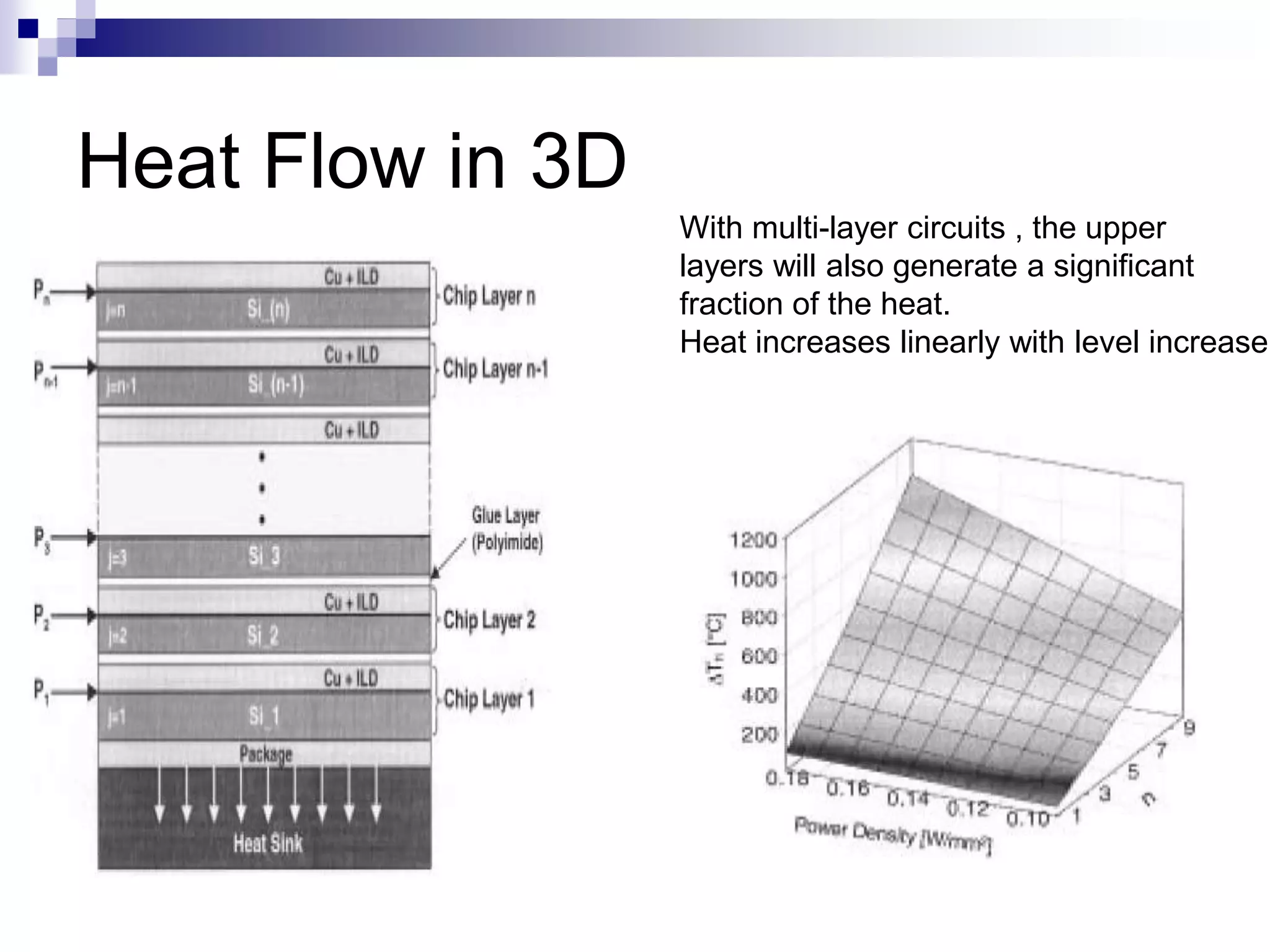

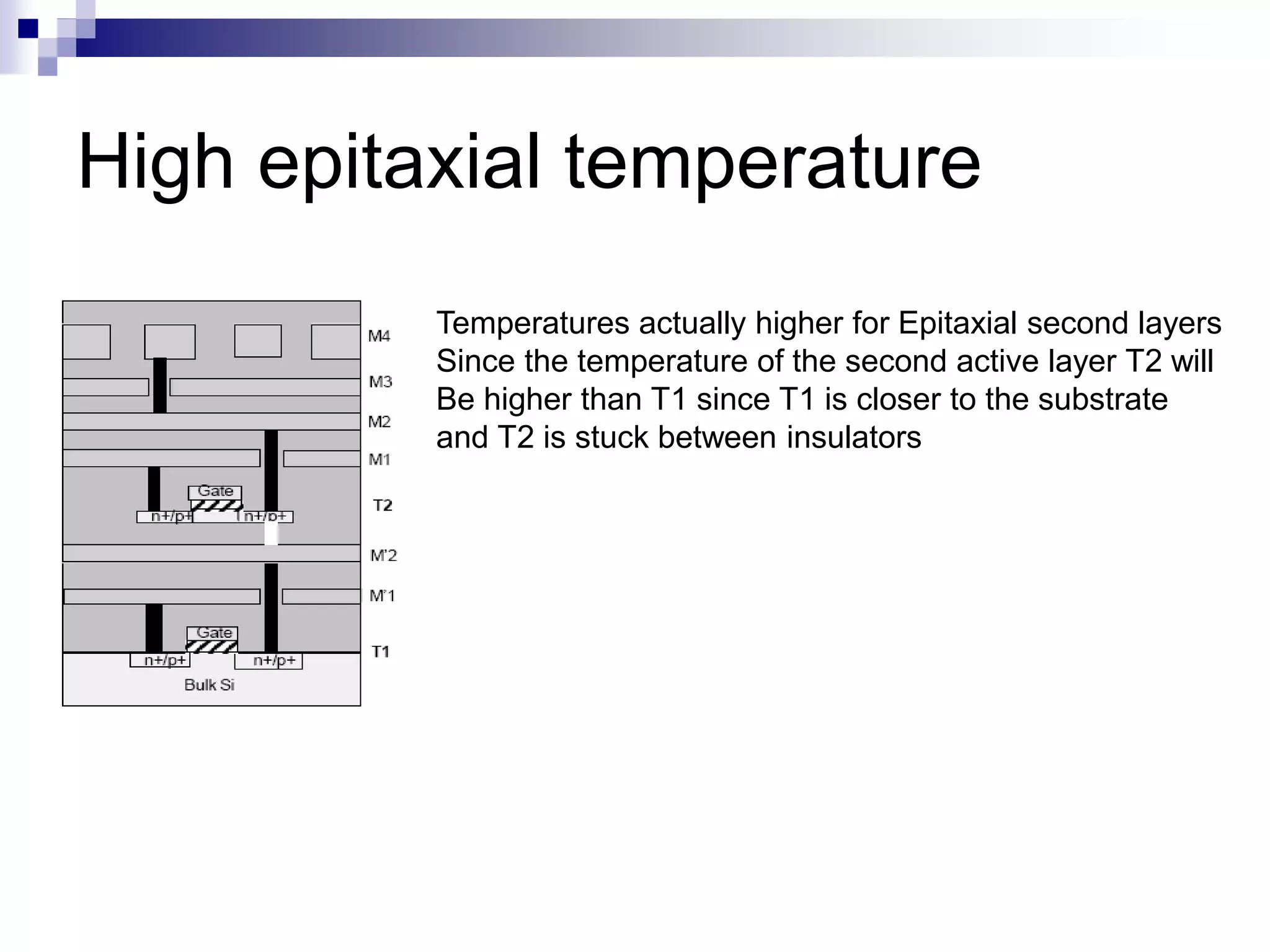

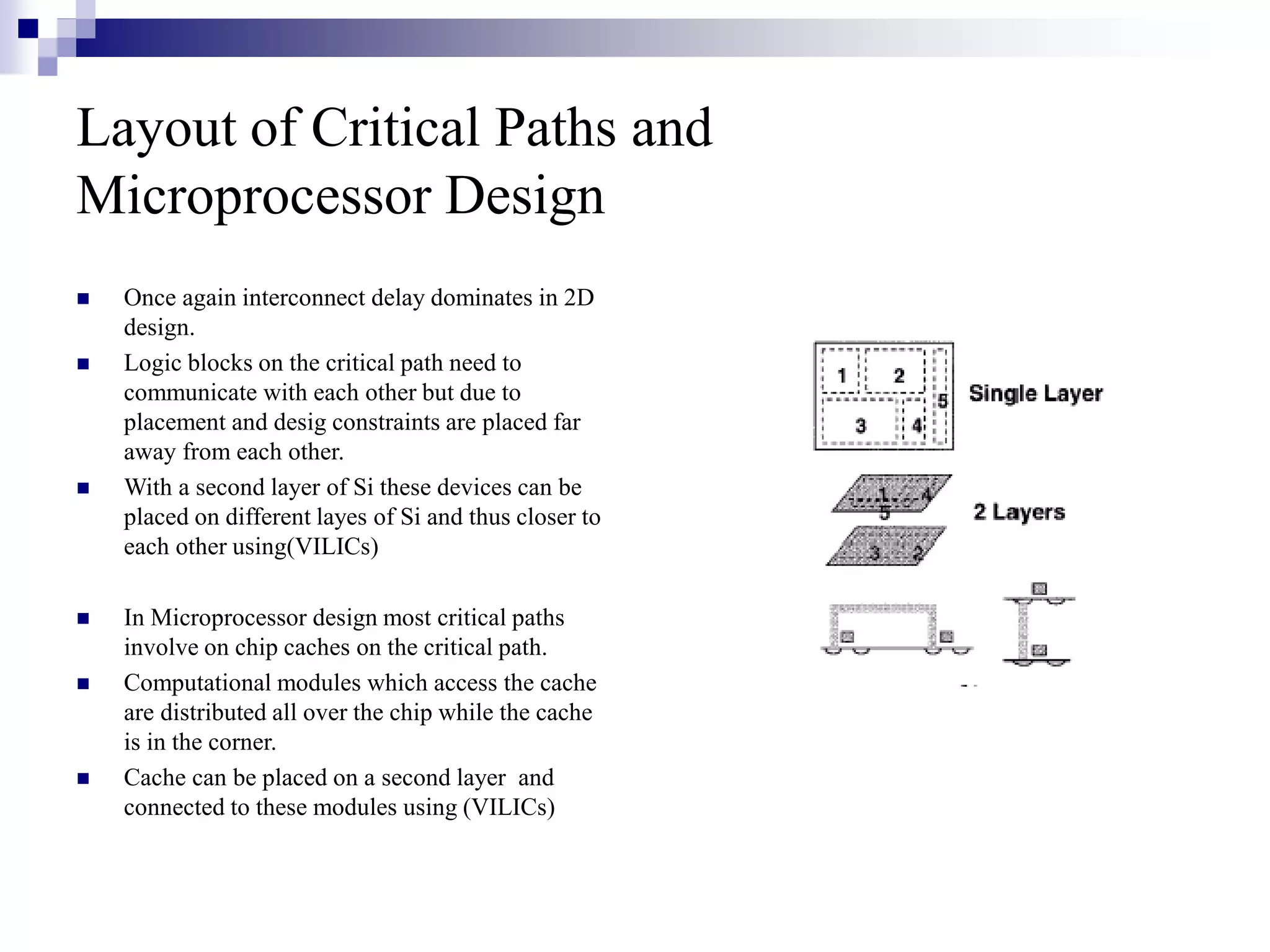

3D IC technology stacks multiple silicon layers vertically using through-silicon vias to connect the layers. This reduces interconnect length and delay. Motivations for 3D ICs include alleviating increasing interconnect delay issues. Fabrication approaches include wafer bonding and epitaxial growth. Performance benefits include reduced timing delay and energy due to shorter interconnects. Challenges include thermal issues due to increased power density, EMI, and reliability concerns between layers. 3D ICs impact circuit design and architecture such as critical path layout, buffer insertion, and mixed-signal separation.