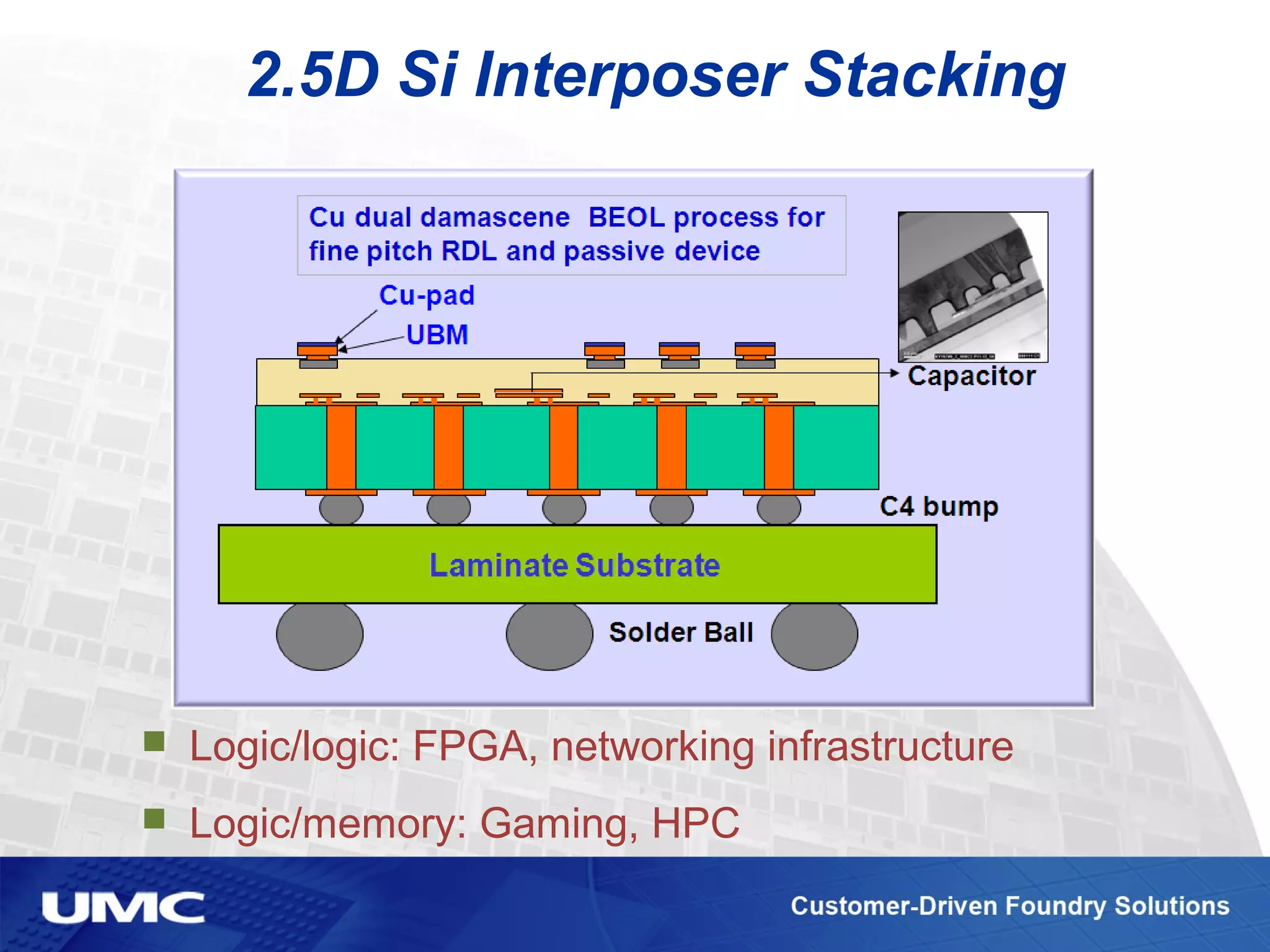

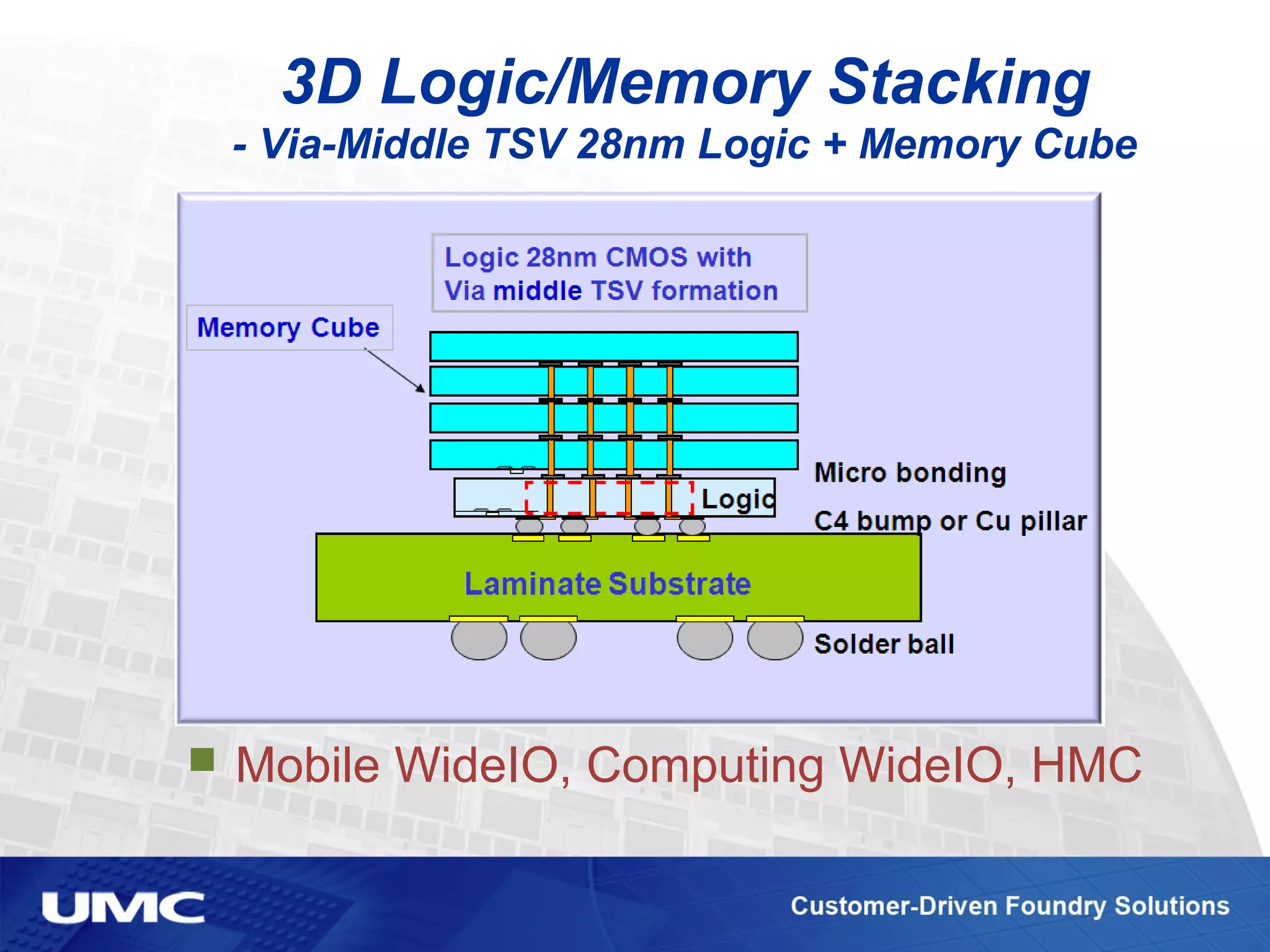

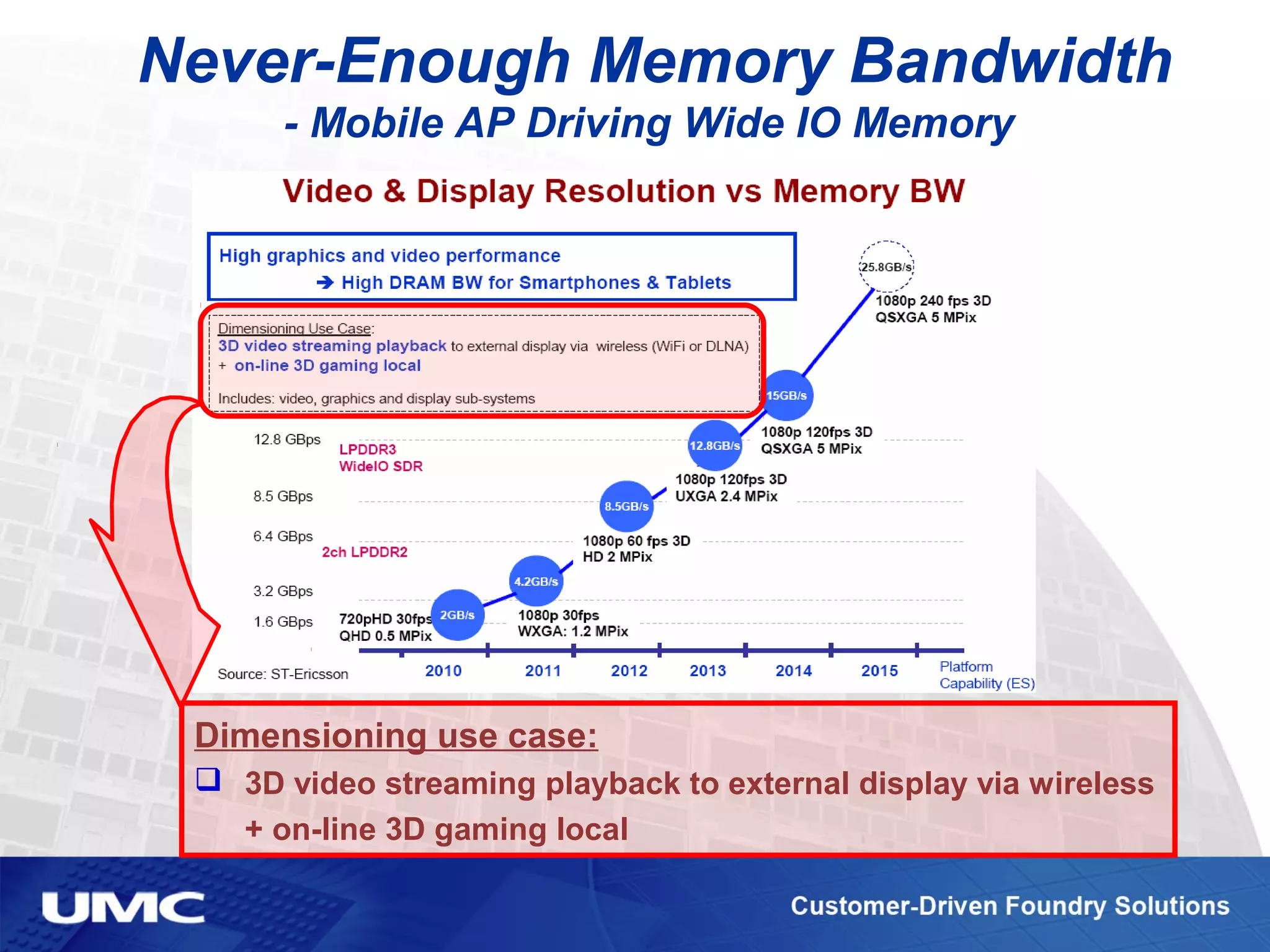

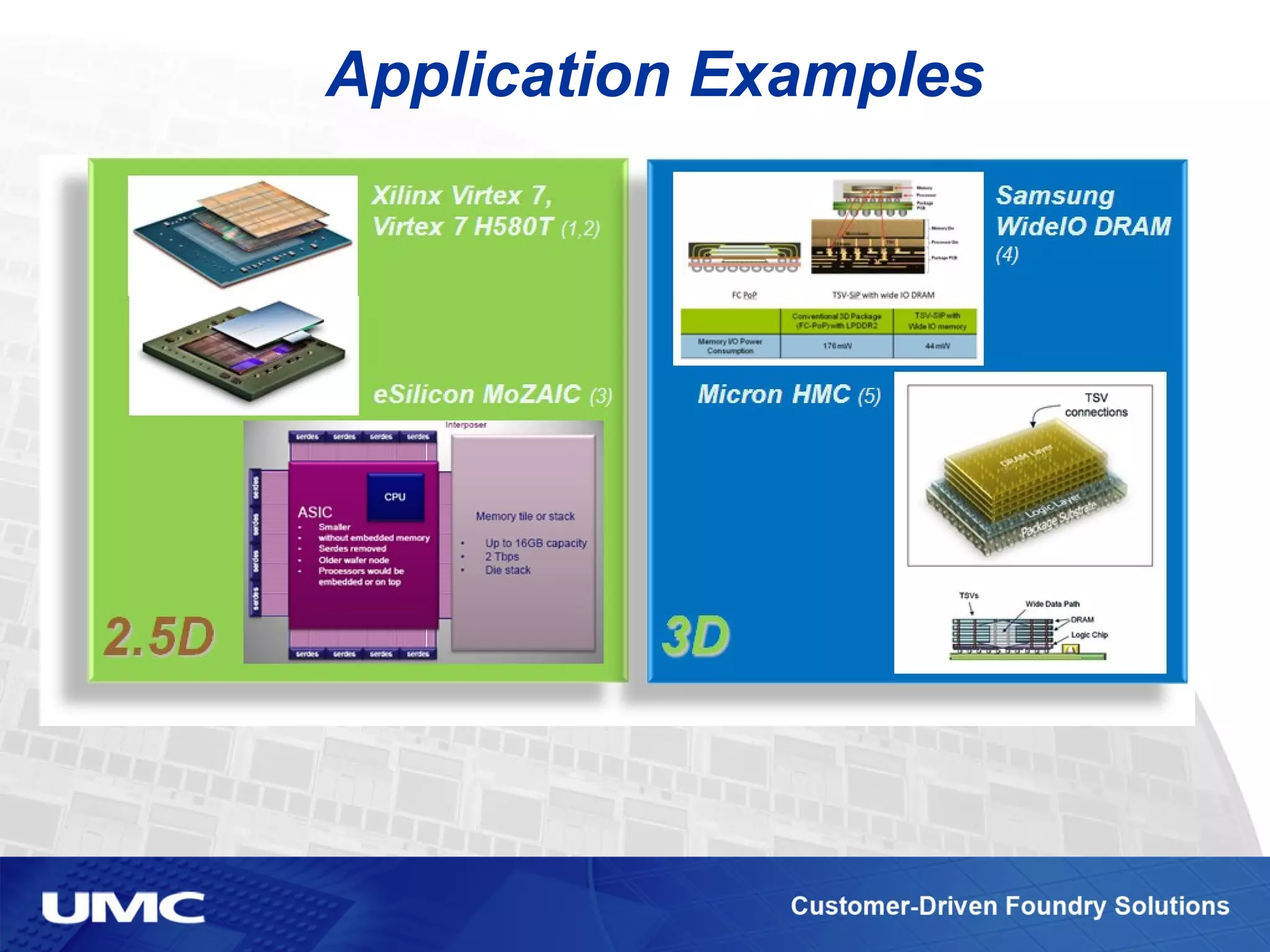

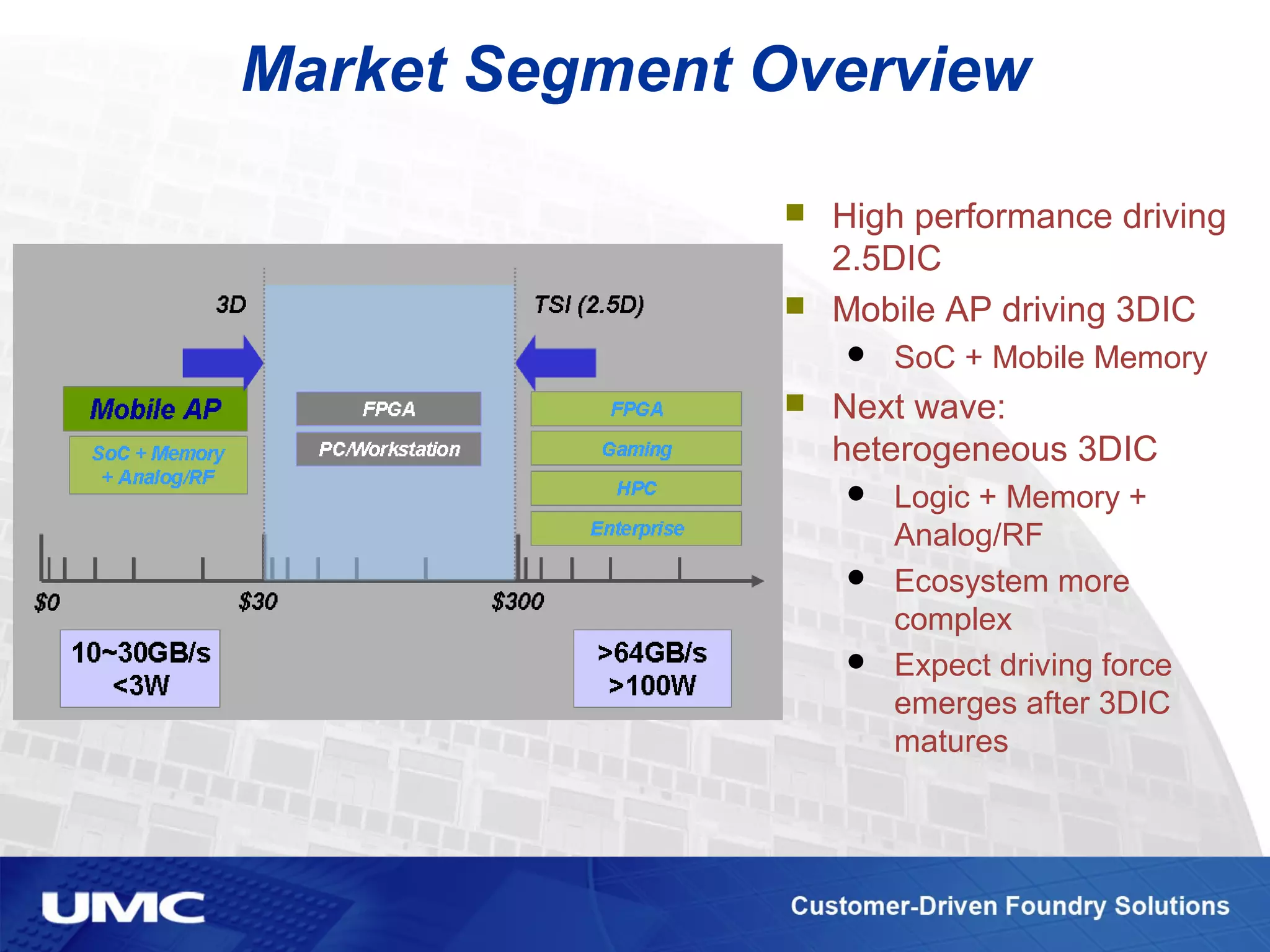

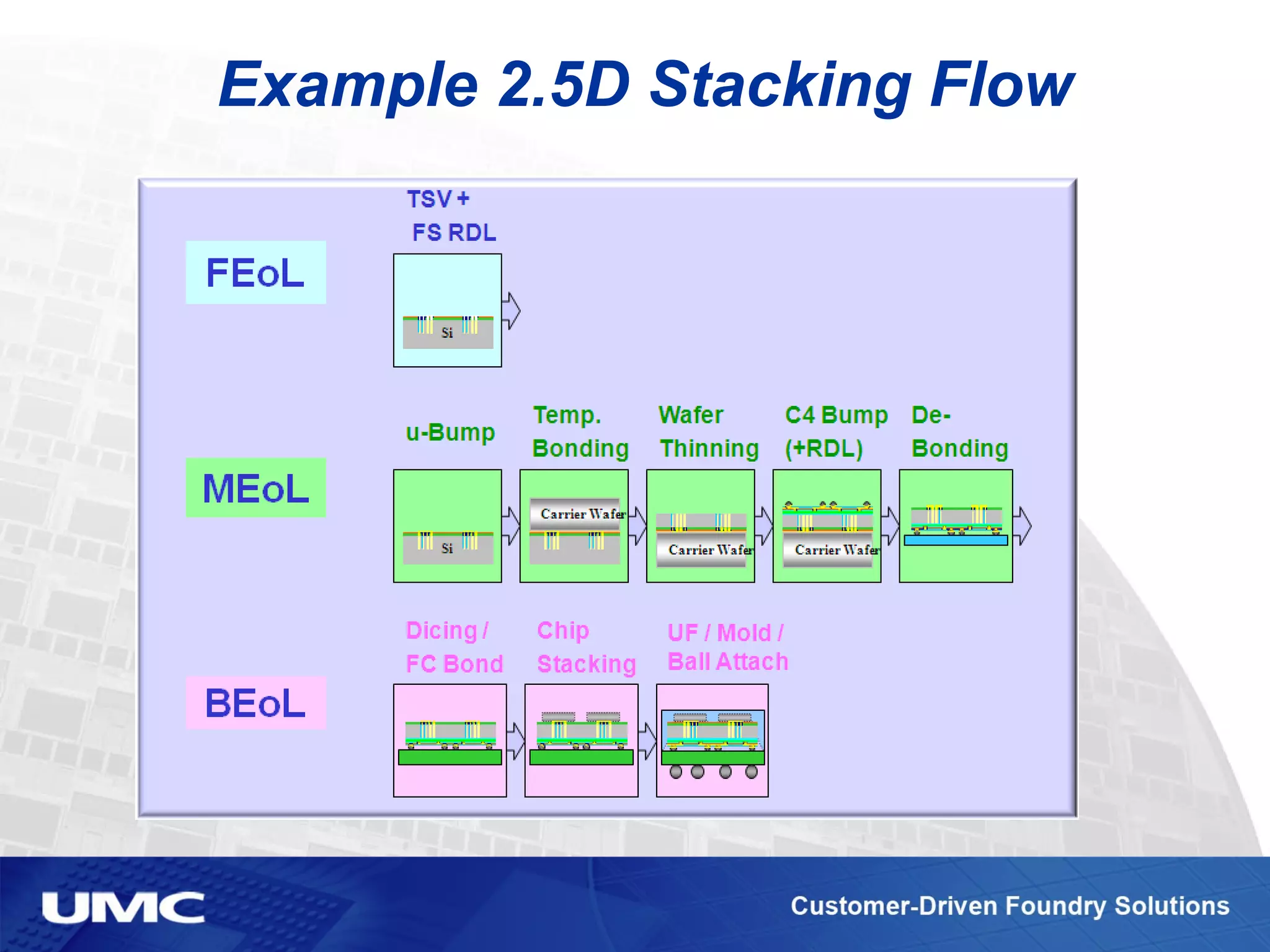

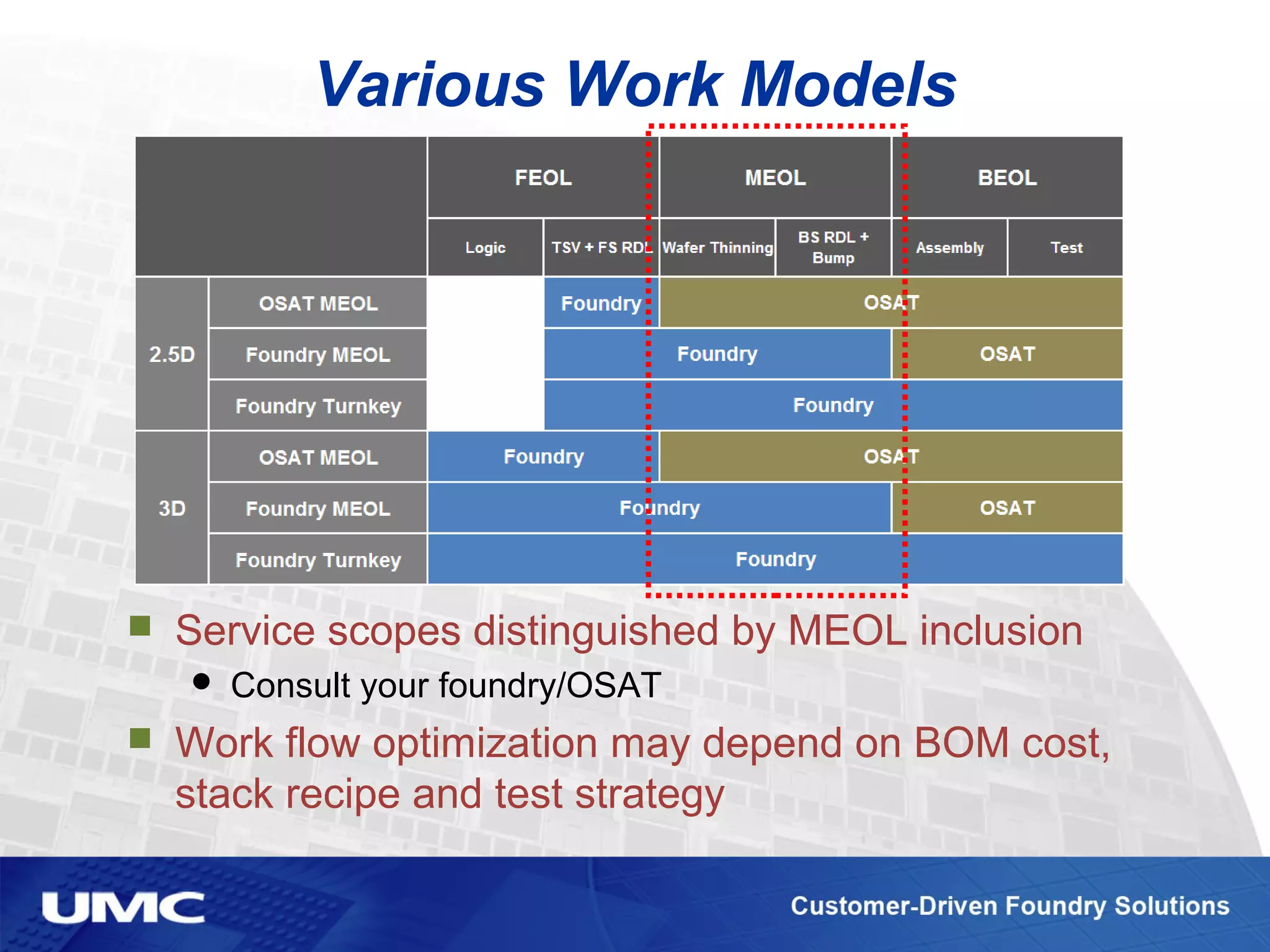

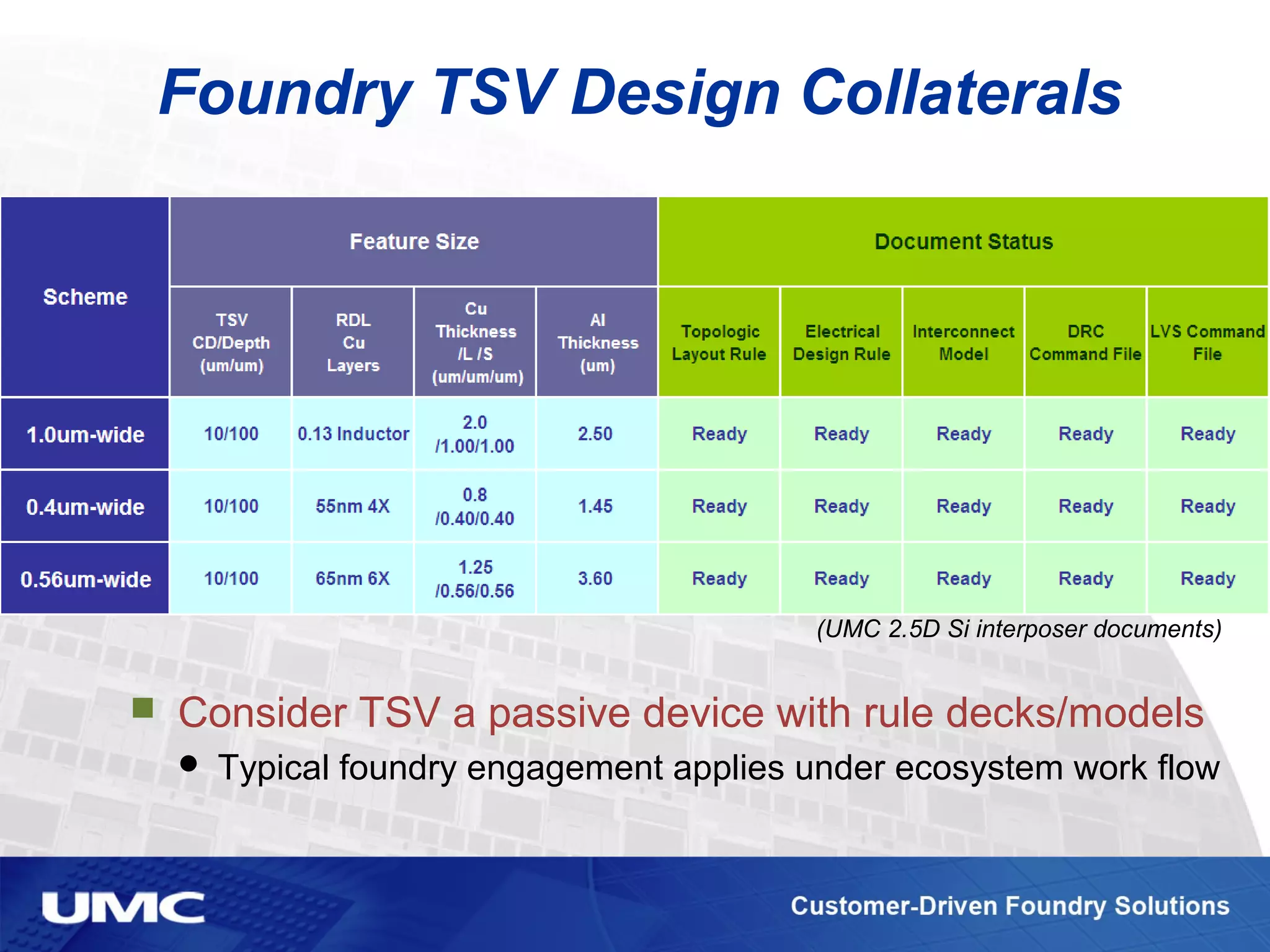

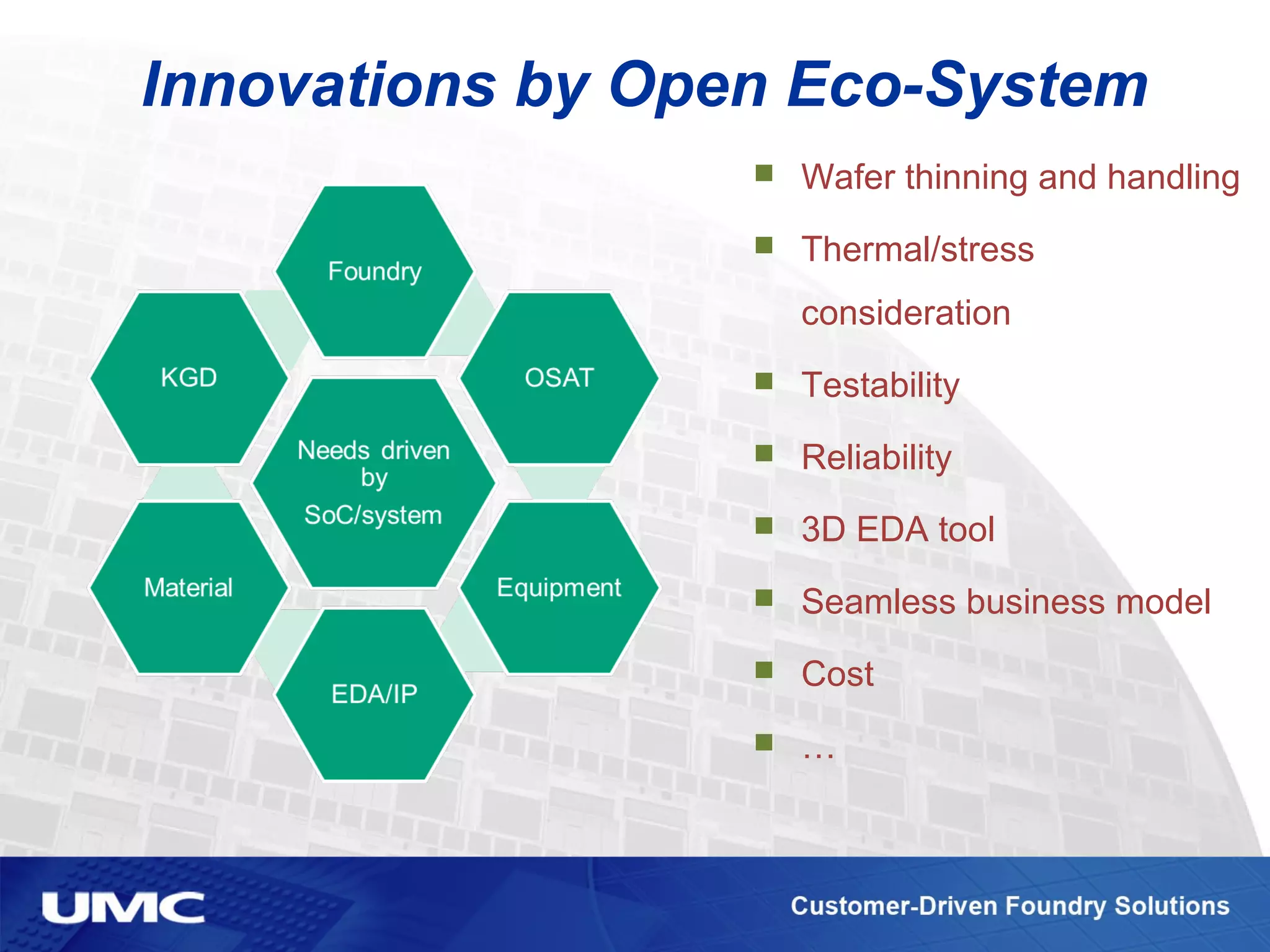

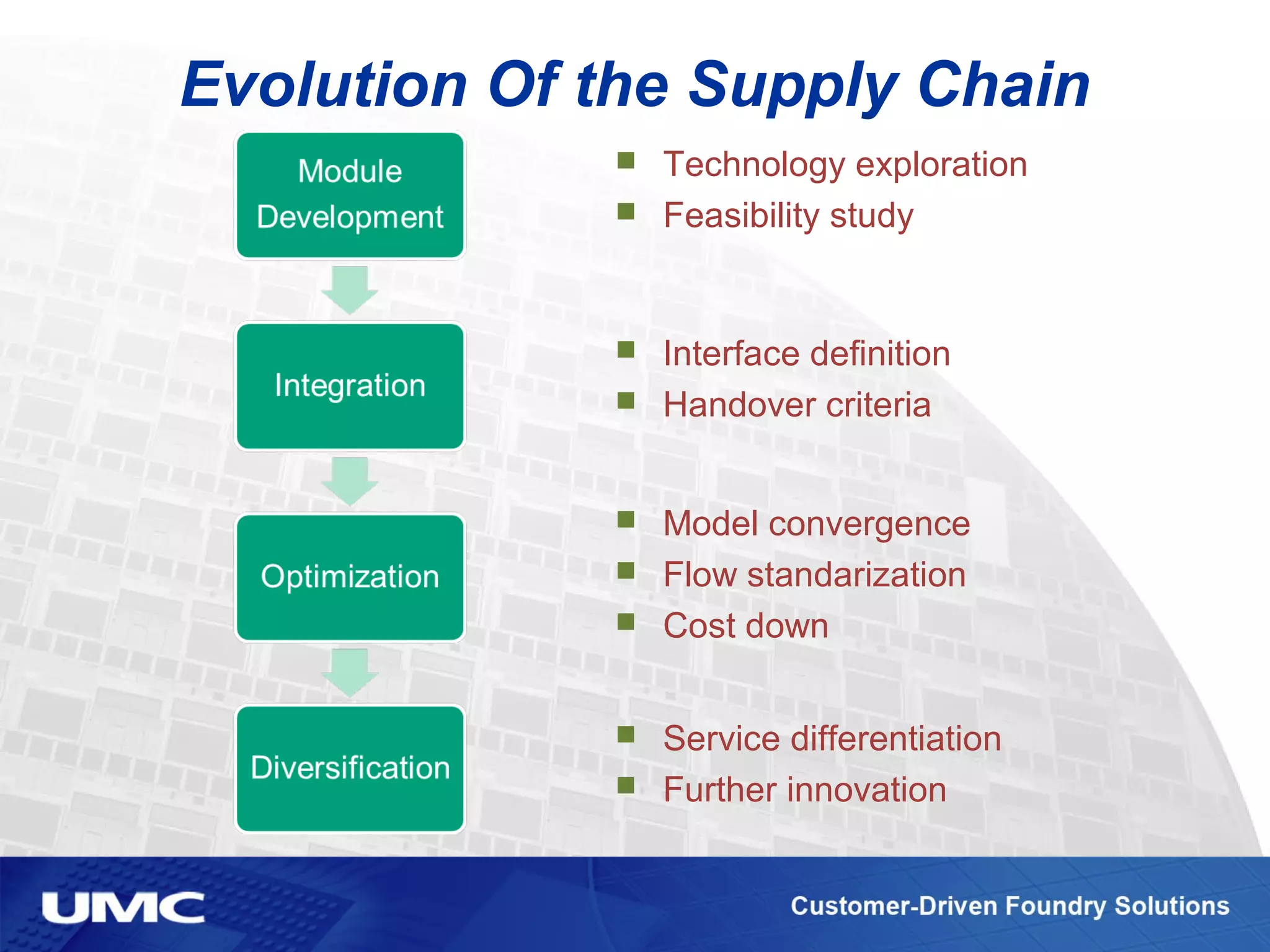

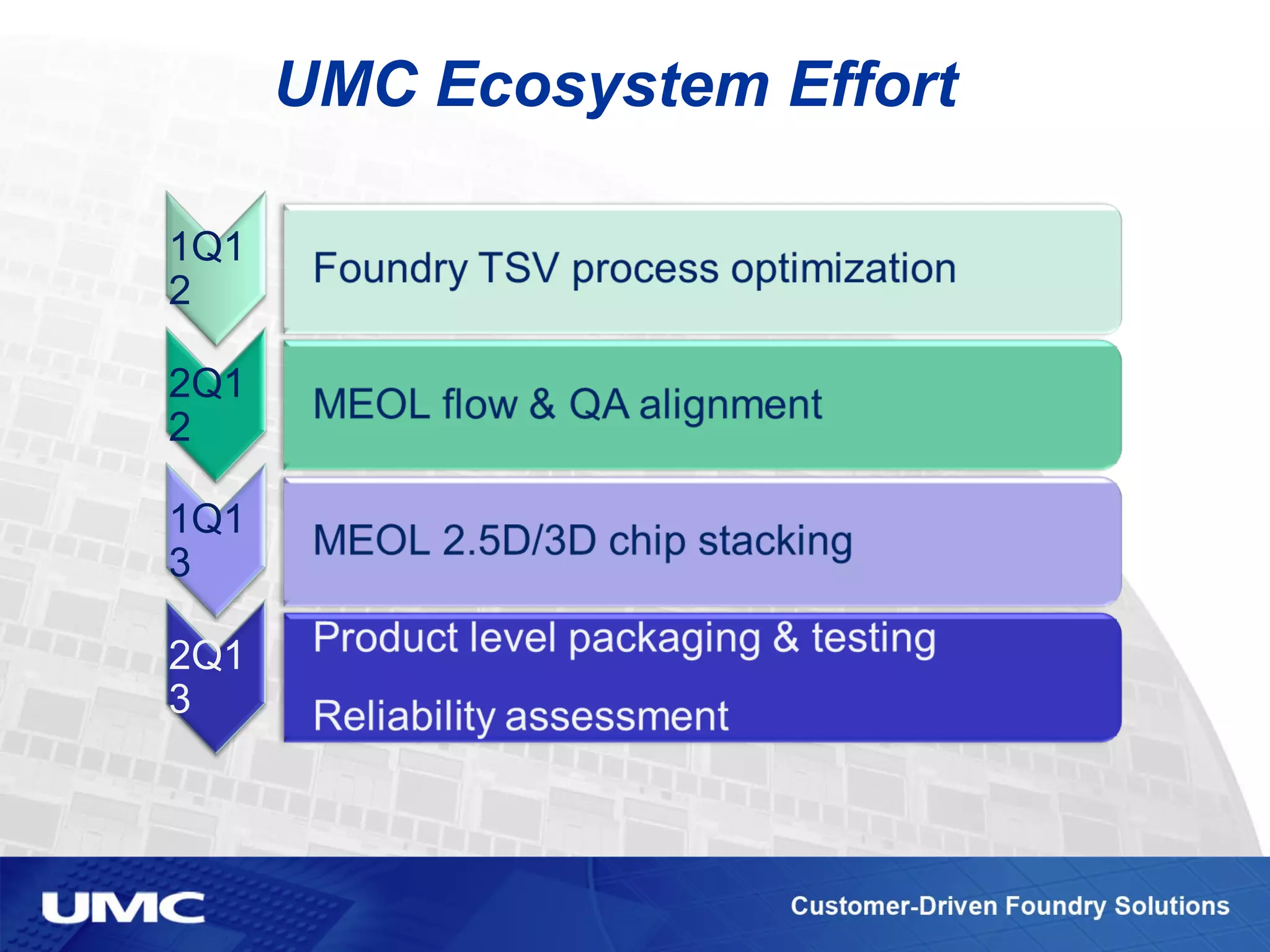

This document discusses 2.5D and 3D chip stacking technologies and the supply chain integration for their development. It outlines applications for 2.5D stacking of logic and memory chips as well as 3D stacking using through-silicon vias. The ecosystem workflow for 2.5D stacking is described, involving various partners from foundries to outsourced assembly and test houses. Finally, the document emphasizes that foundry development of through-silicon via processes has demonstrated key process issues can be identified and resolved, while ecosystem focus going forward includes product reliability assessment and collaboration on tools for 3D design.