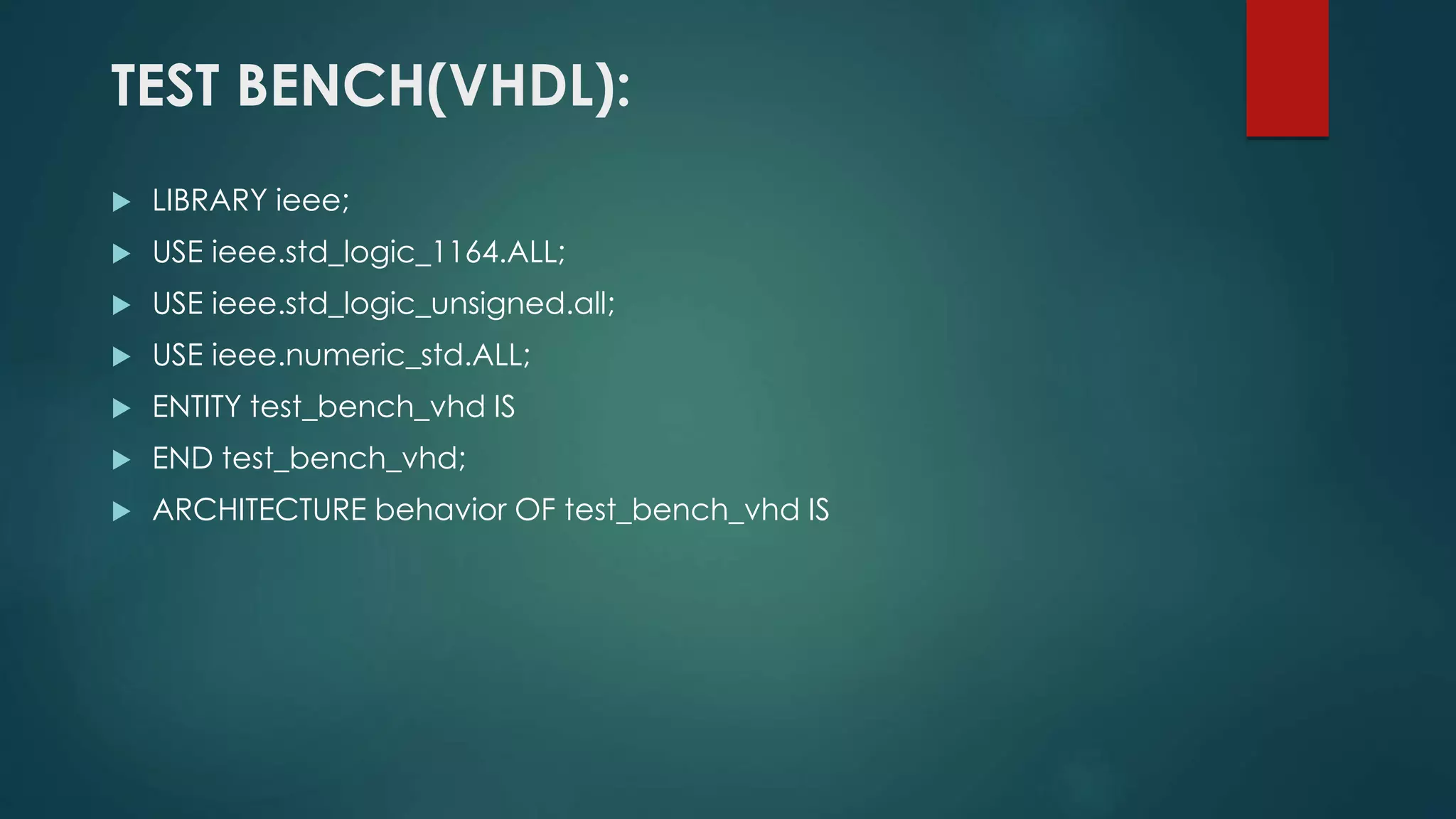

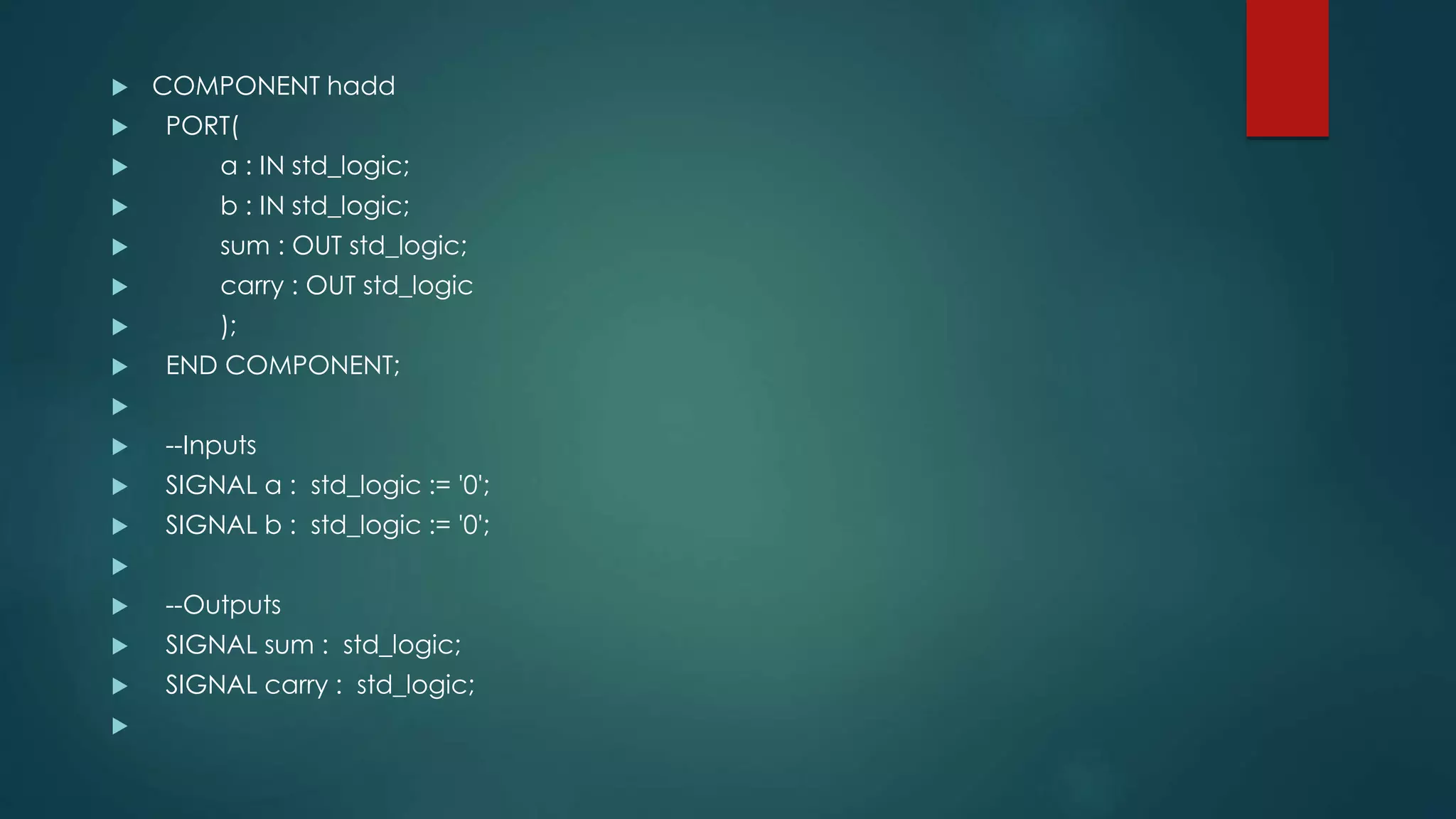

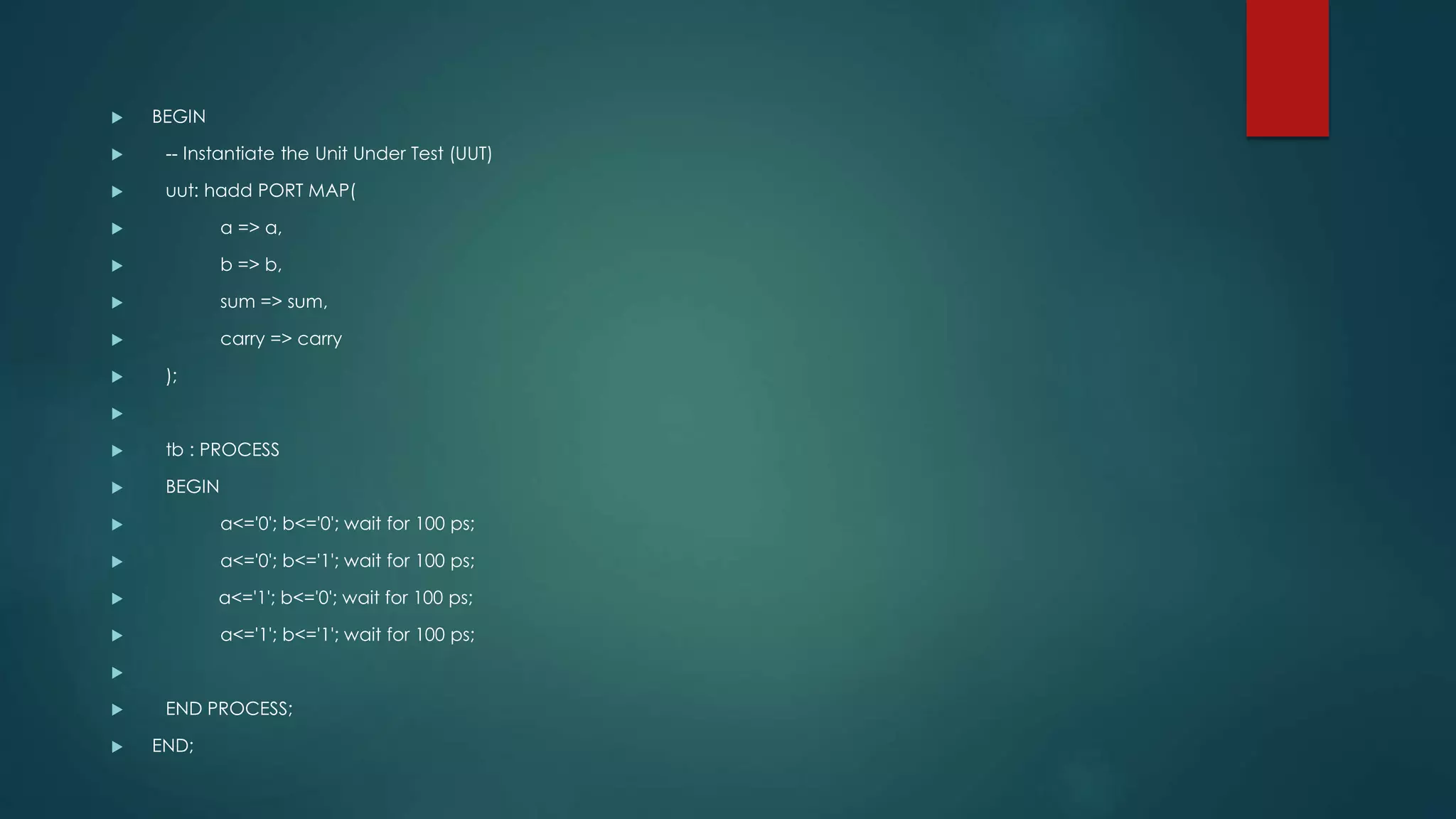

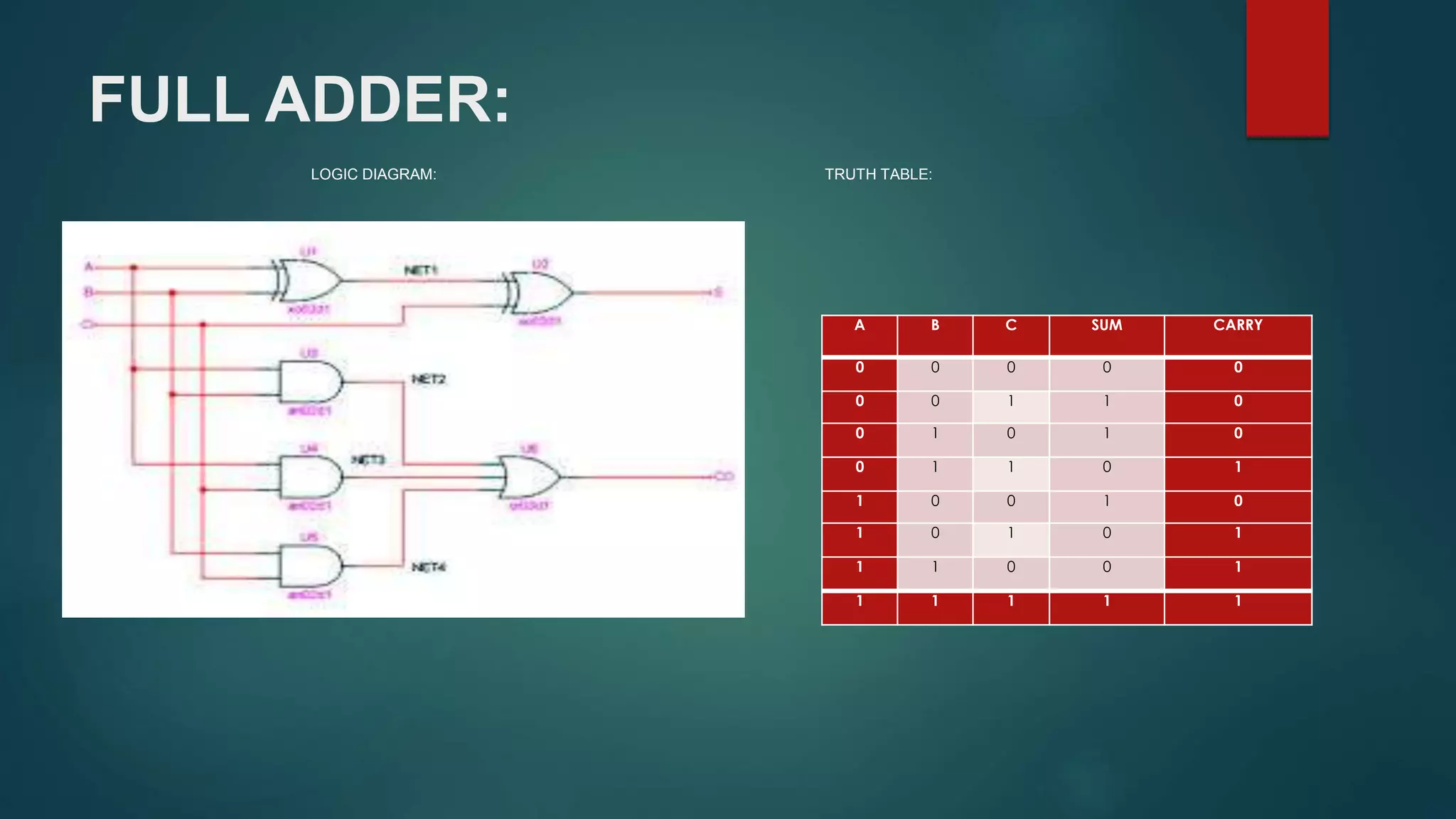

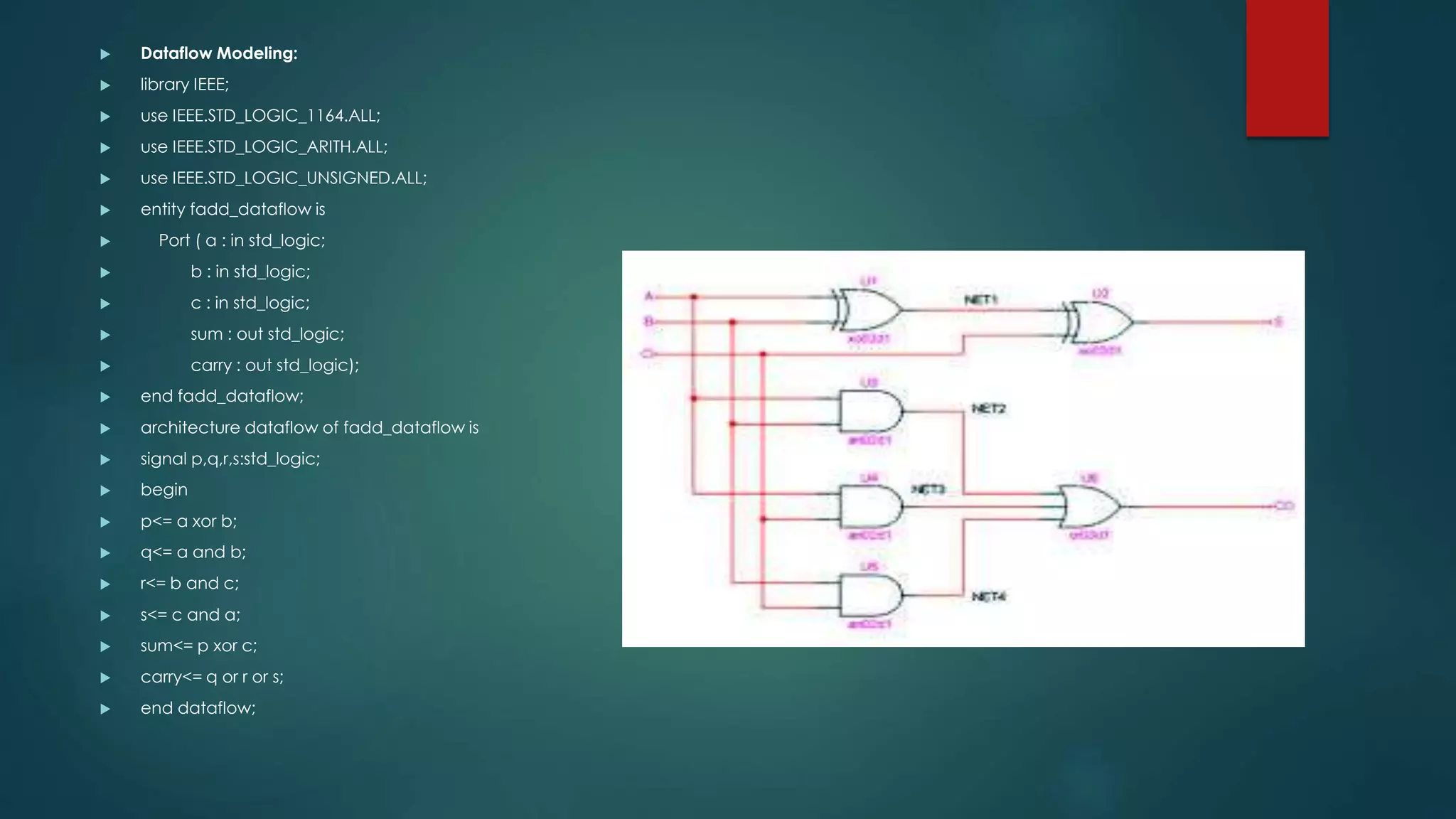

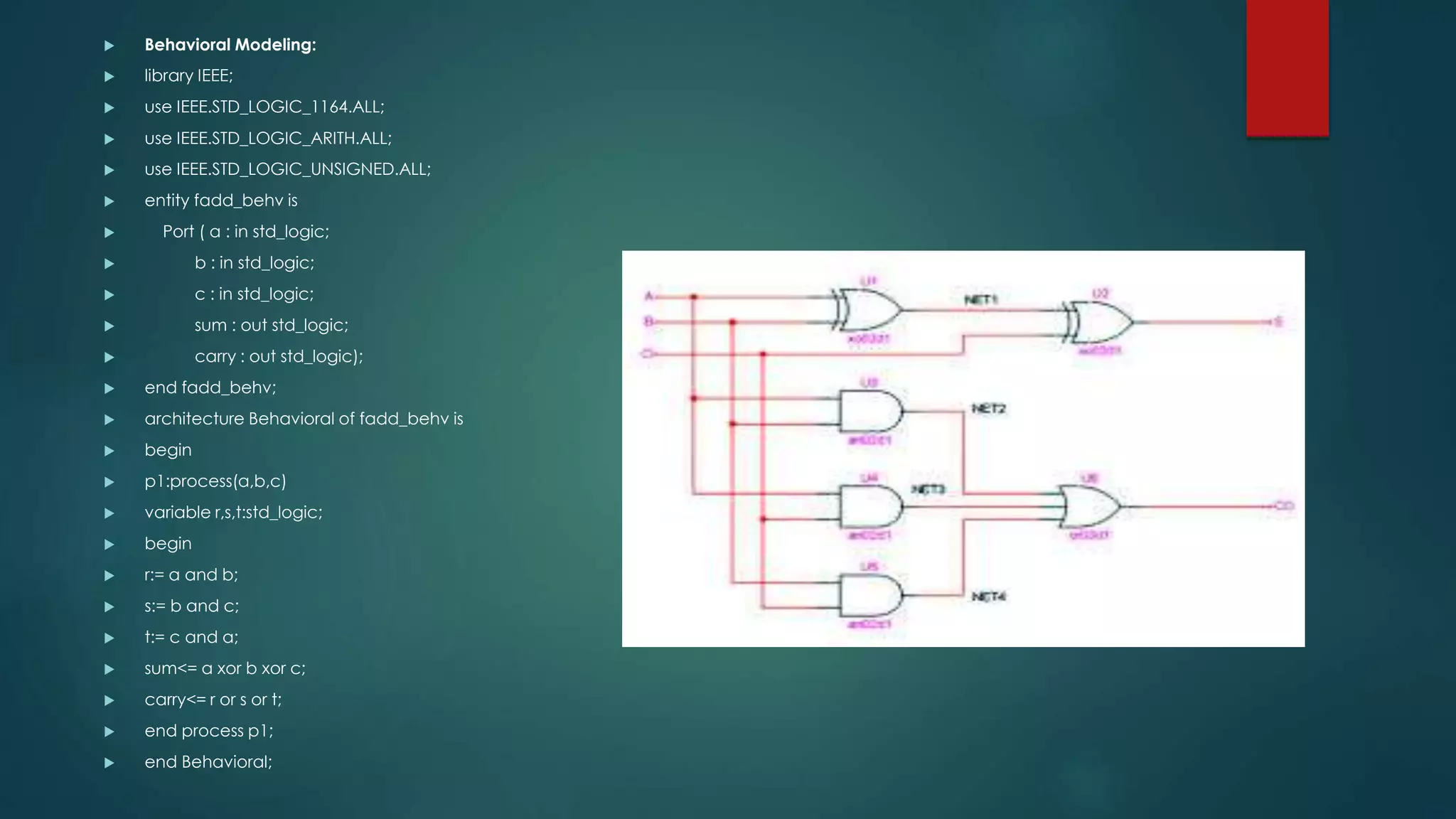

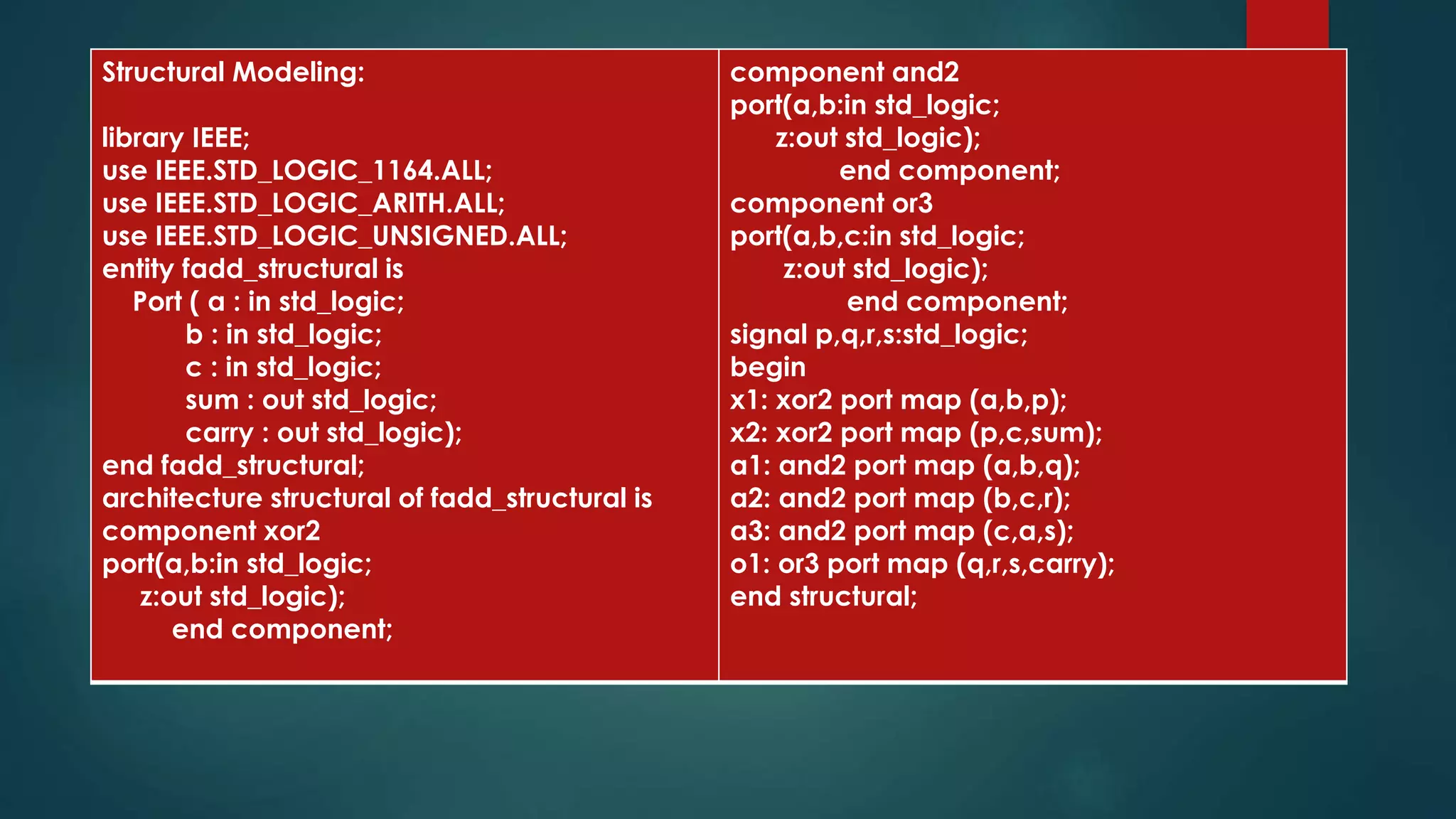

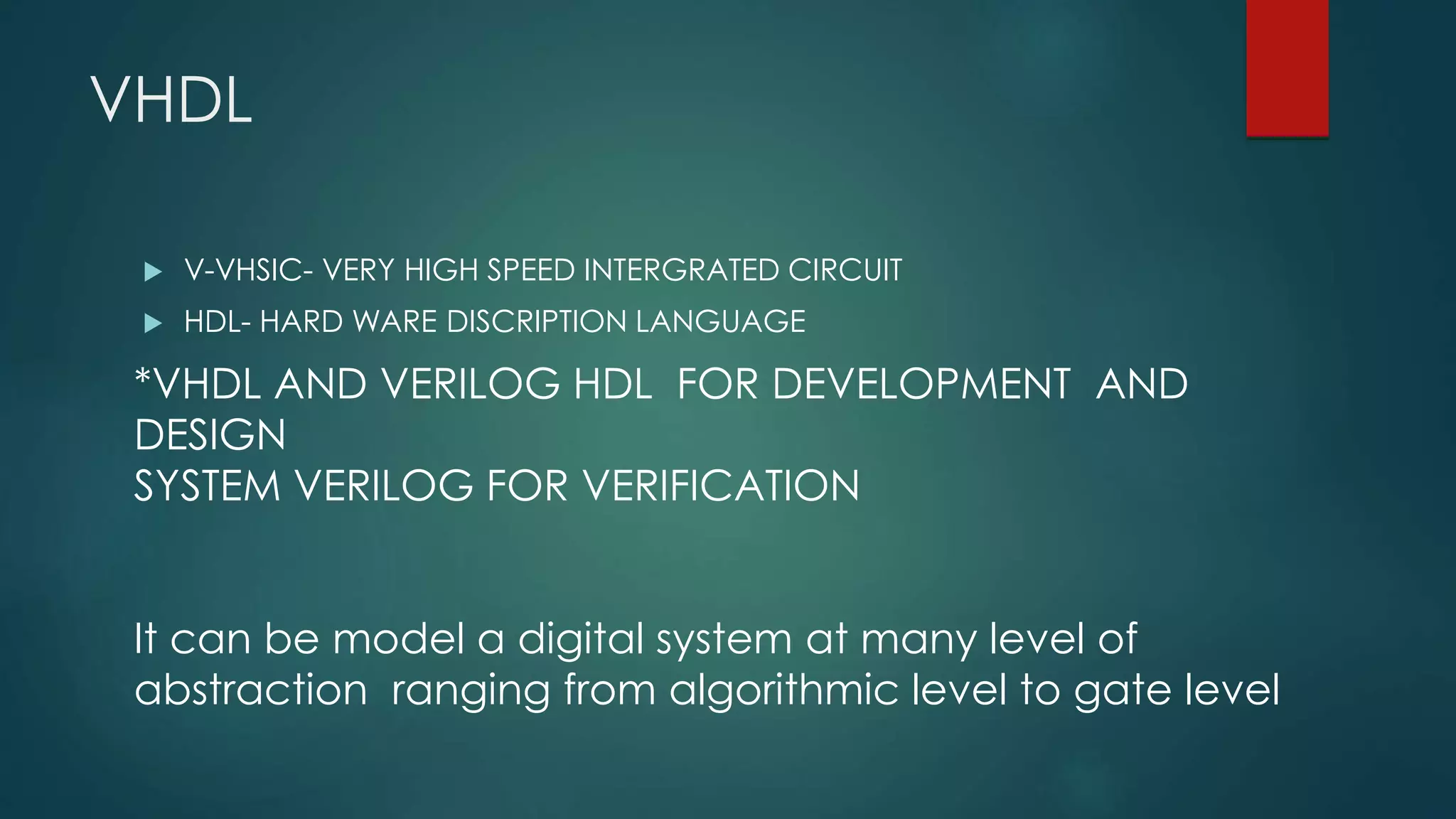

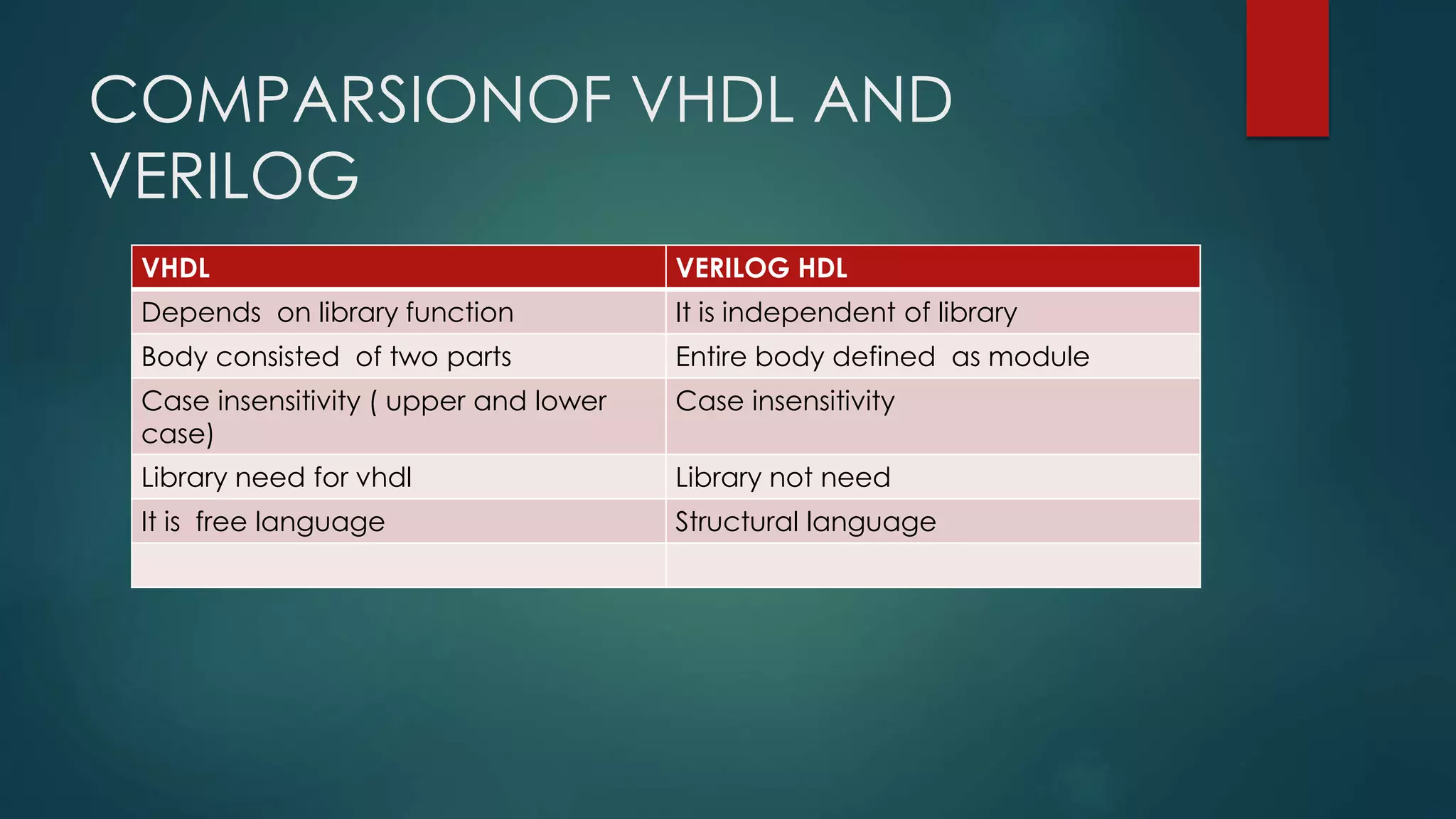

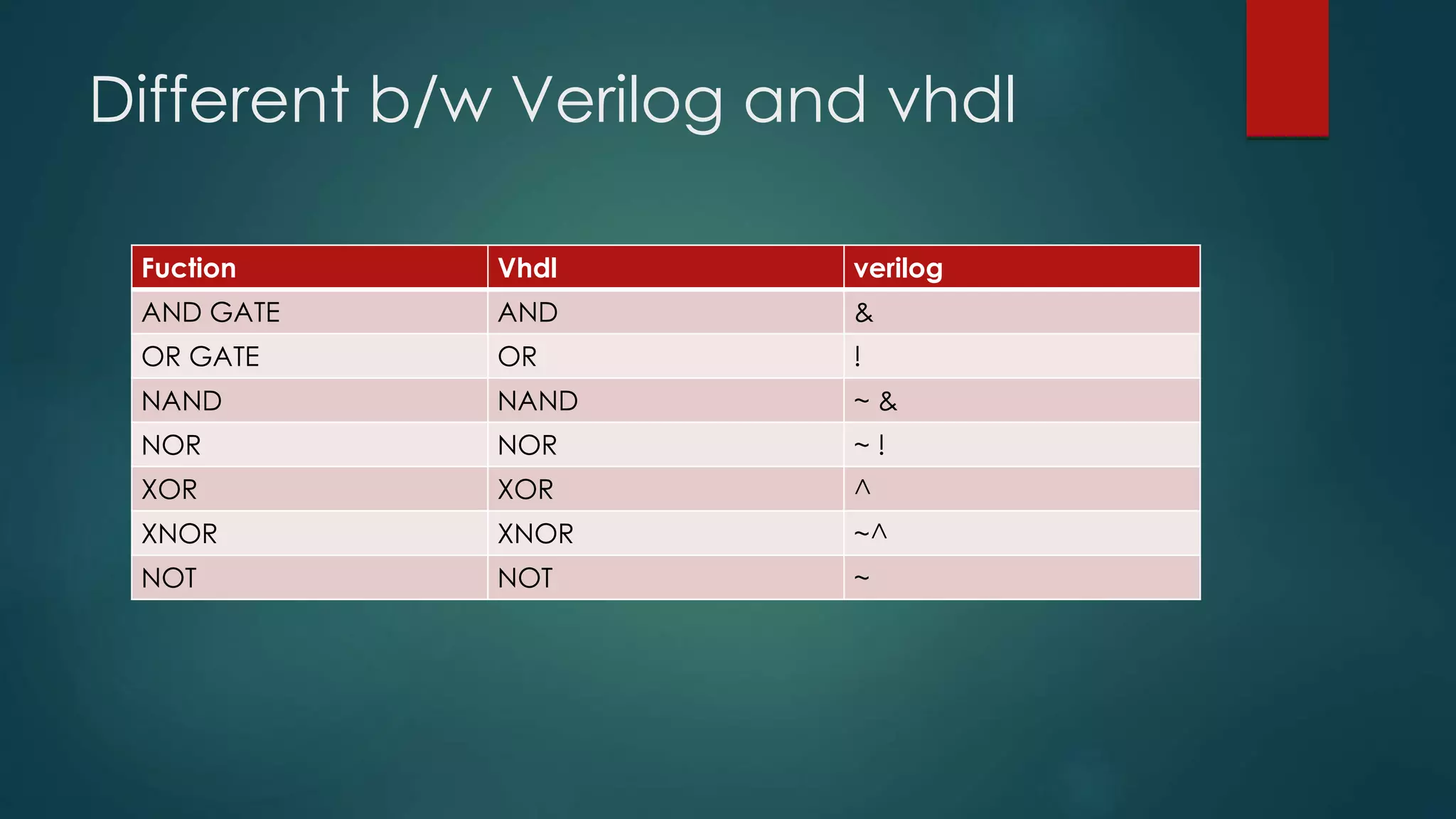

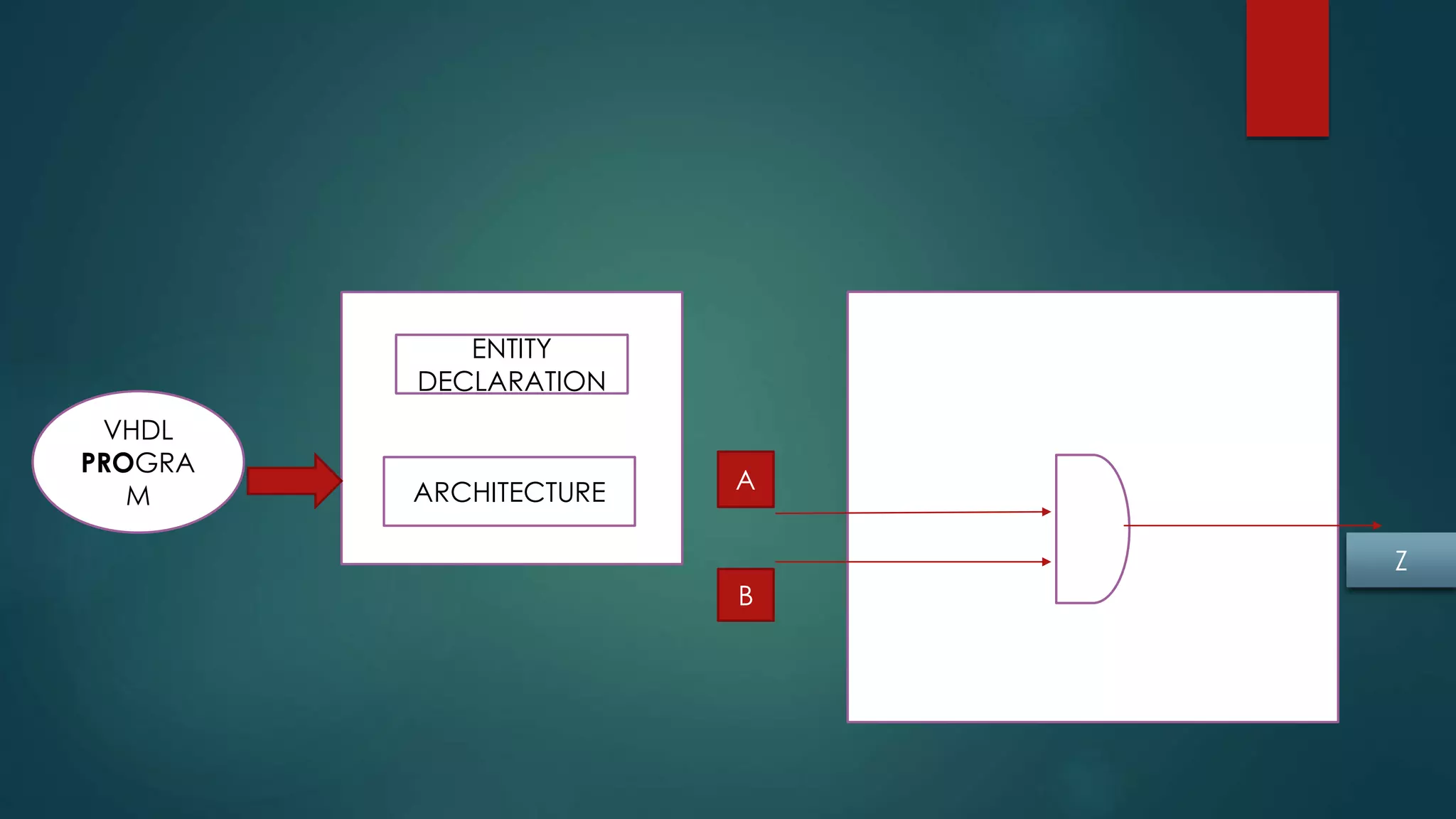

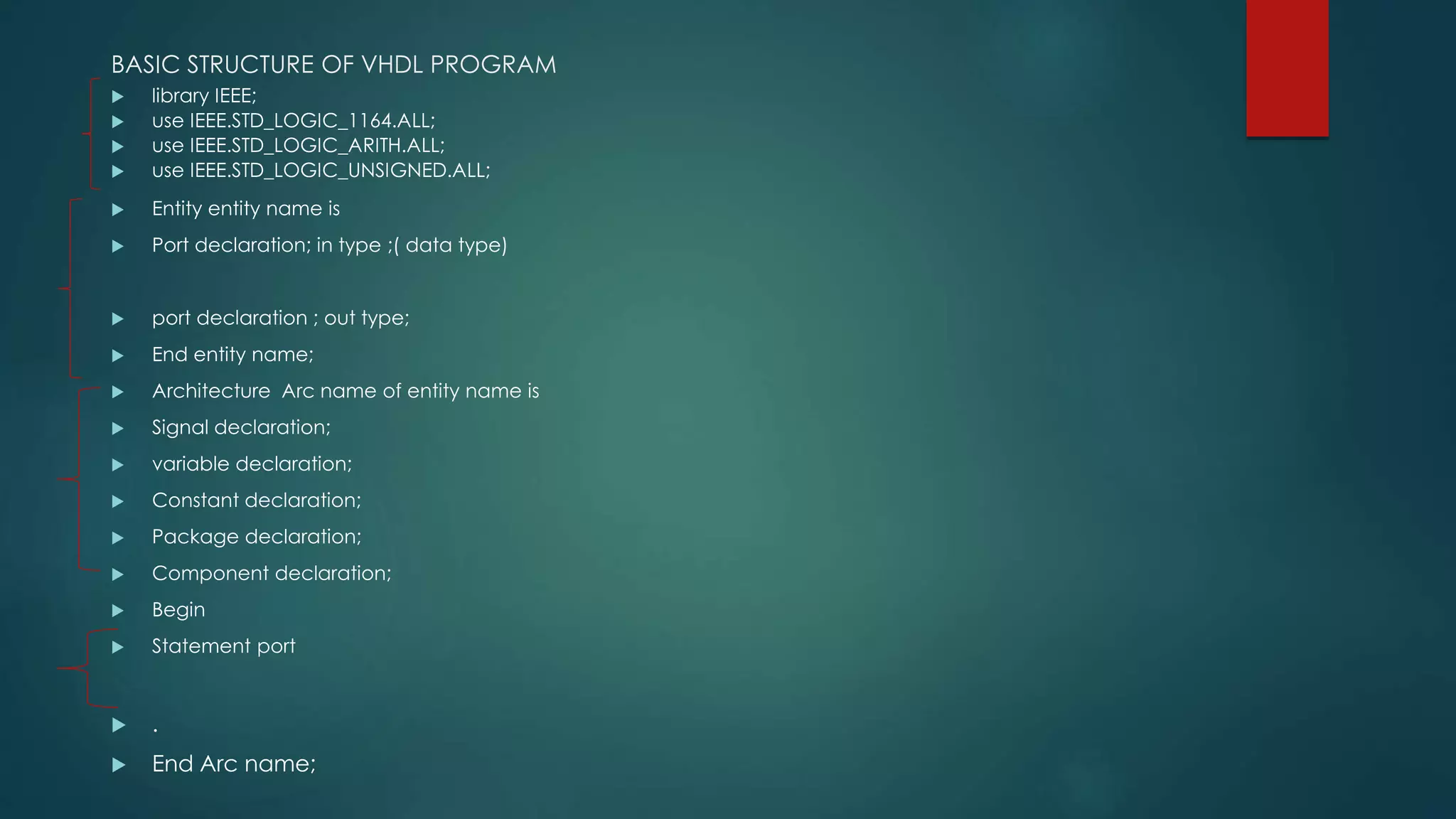

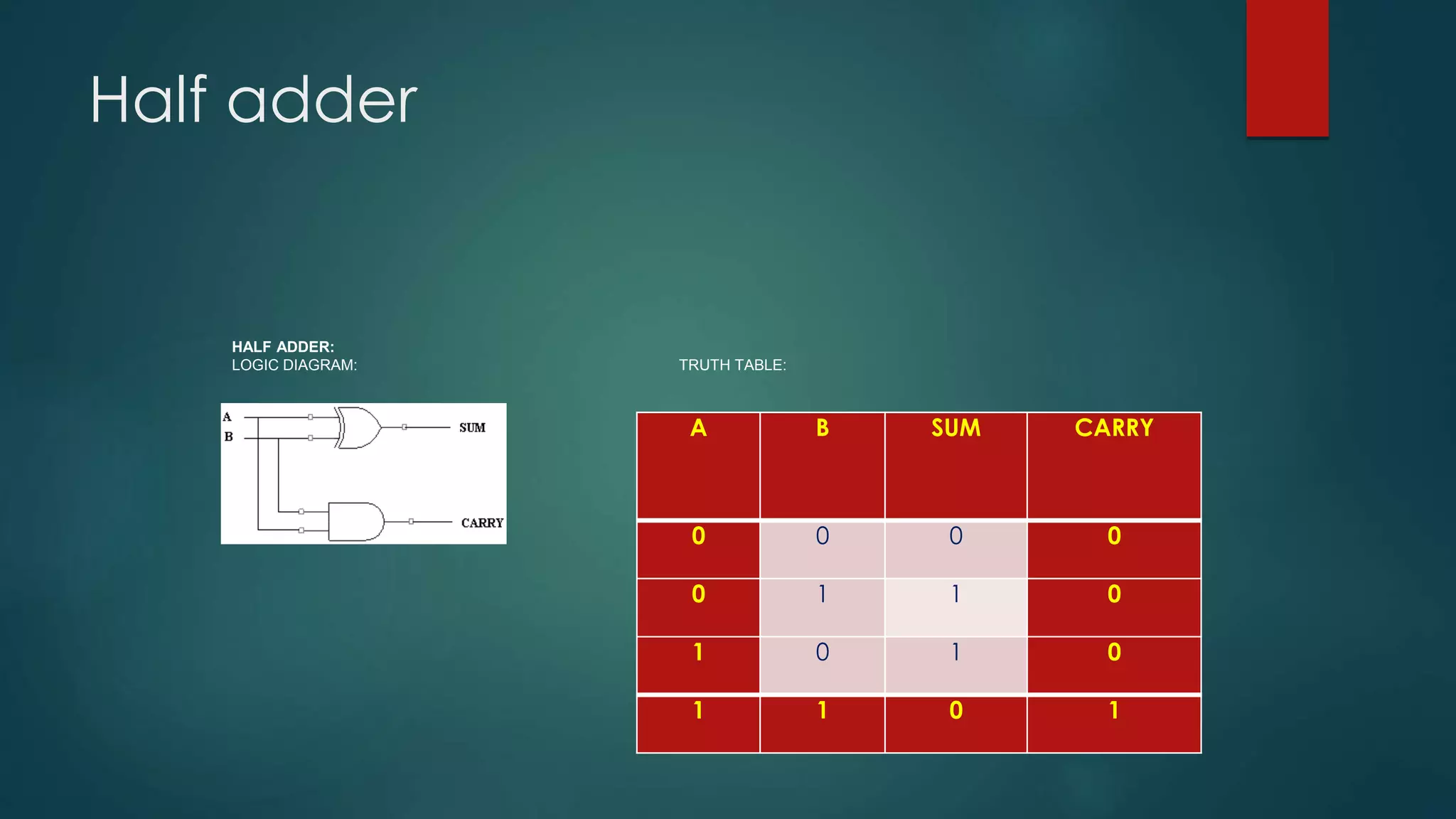

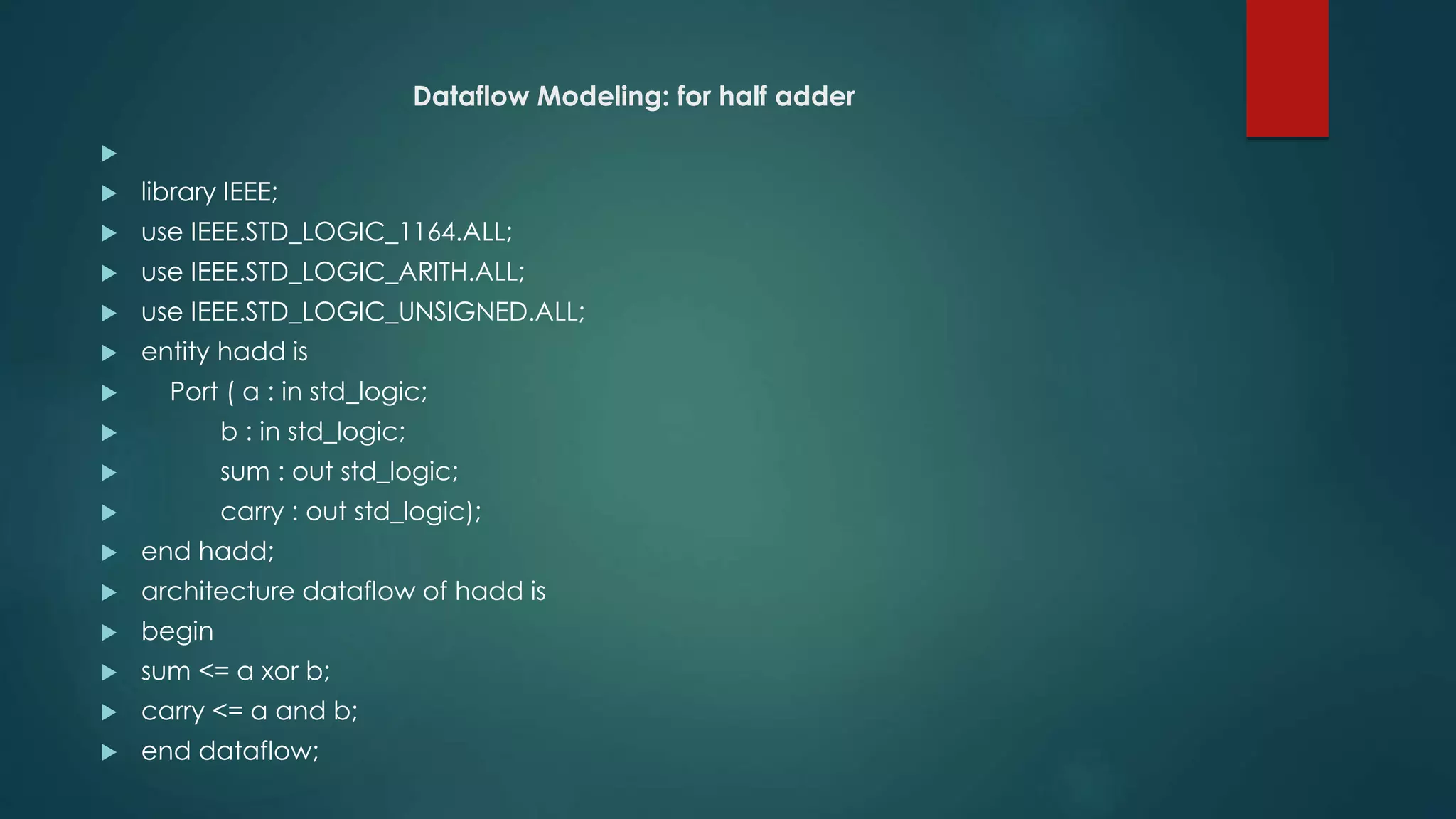

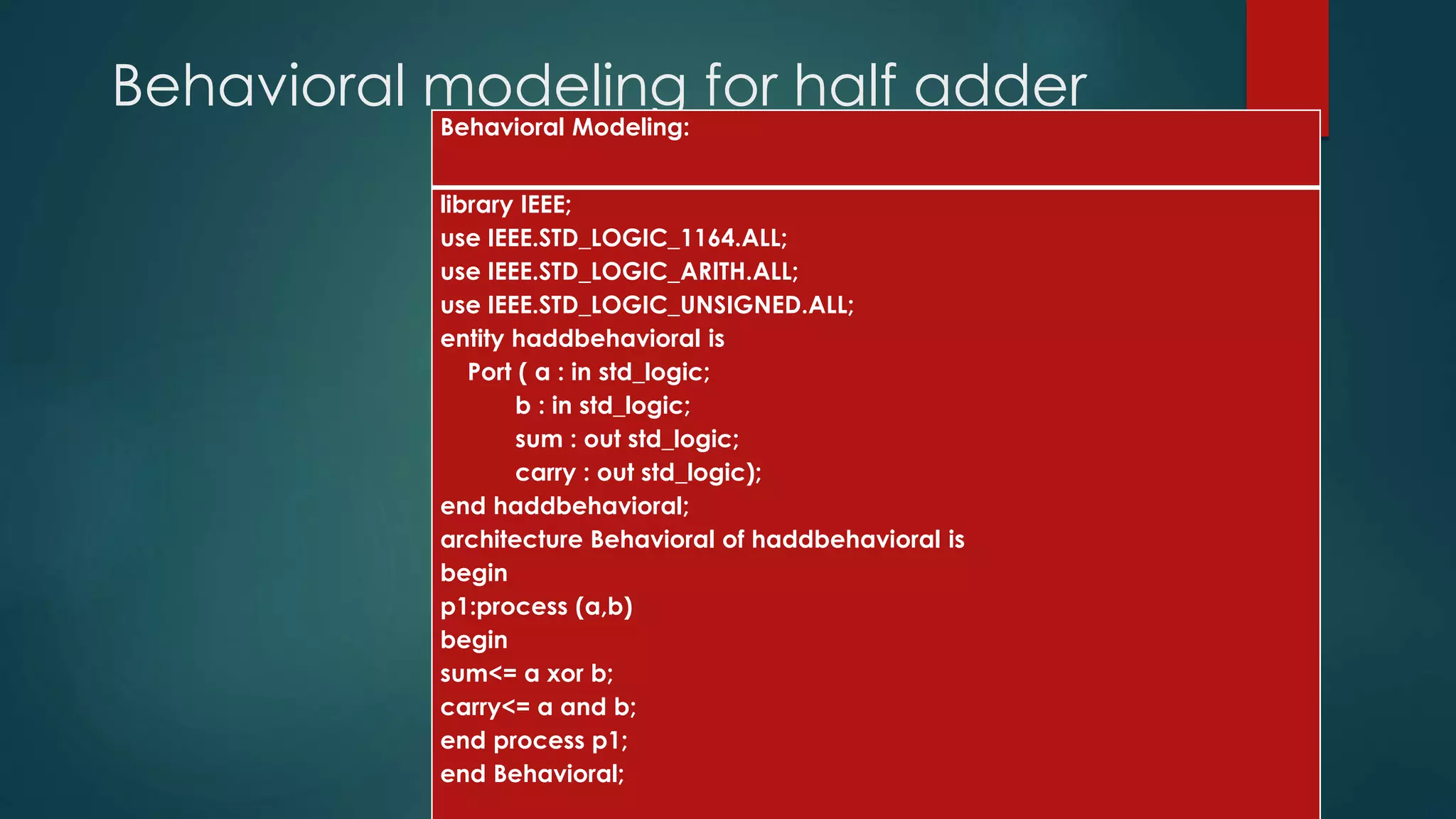

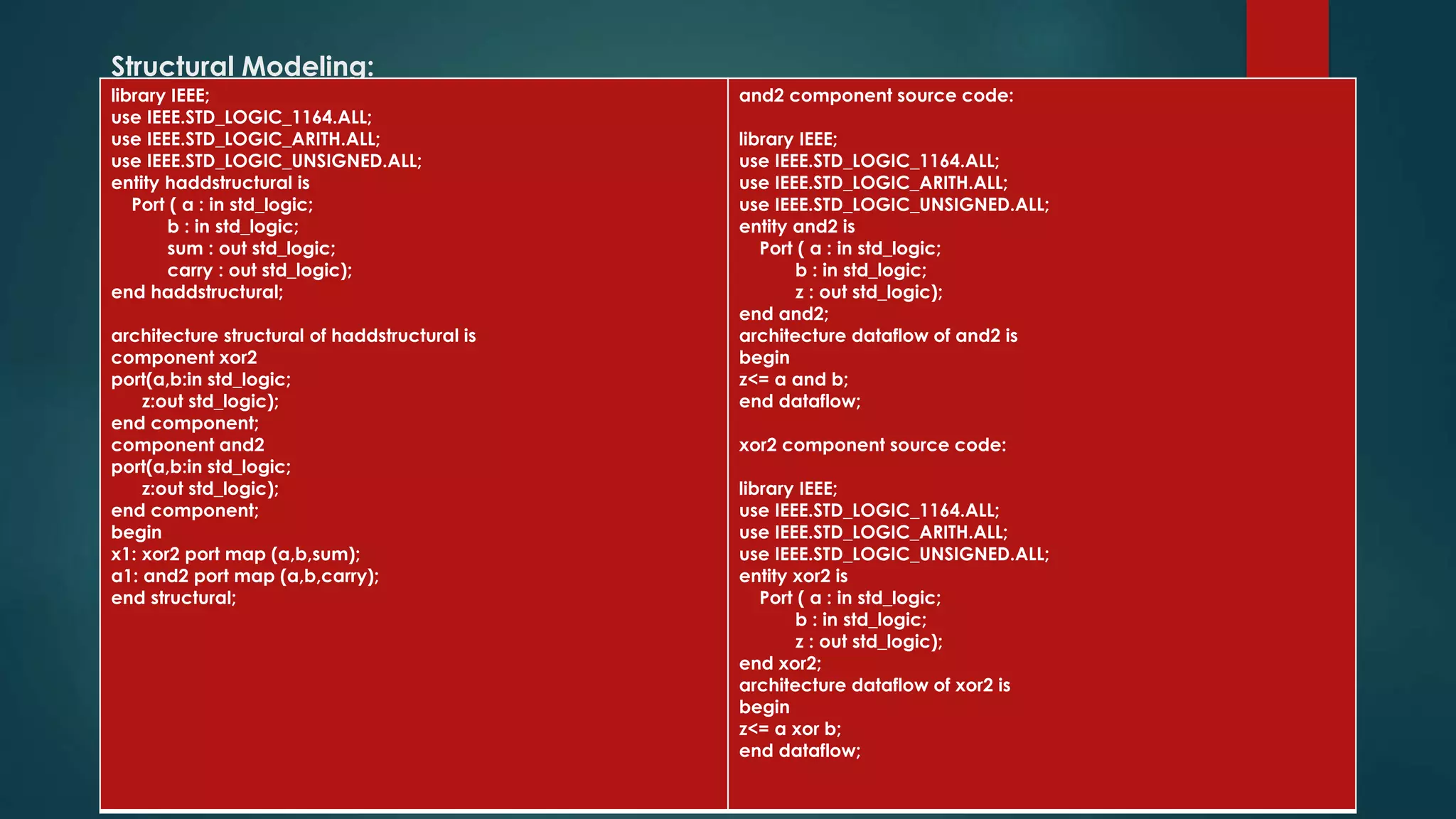

The document discusses VHDL (VHSIC Hardware Description Language), a hardware description language used to model, design, and test digital systems. It provides examples of modeling half adders and full adders in VHDL using different approaches like dataflow, behavioral, and structural modeling. It also compares VHDL with Verilog and provides code examples to implement basic logic gates in both languages. Test benches are demonstrated to verify and test VHDL designs.

![Gate code for verilog

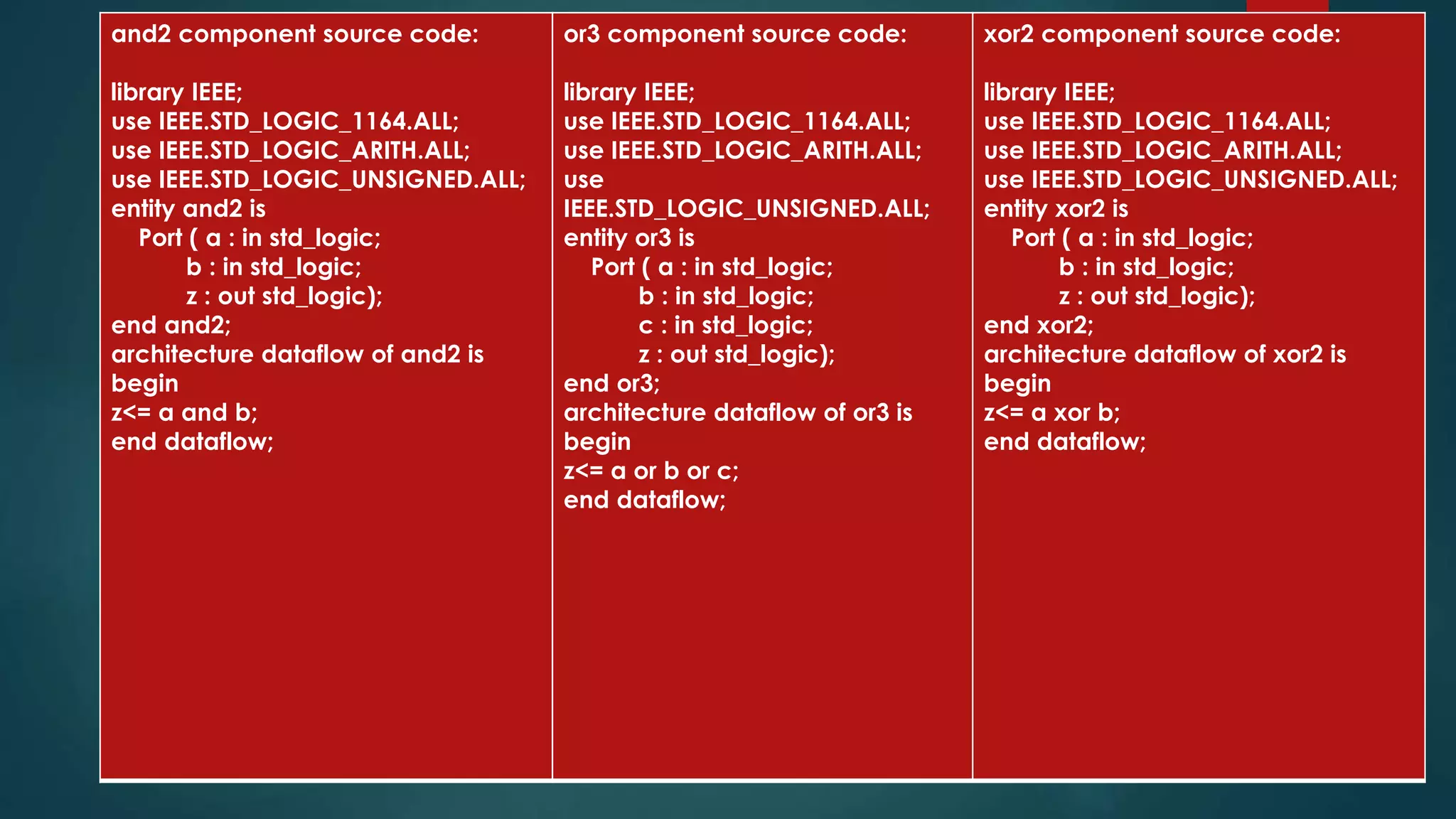

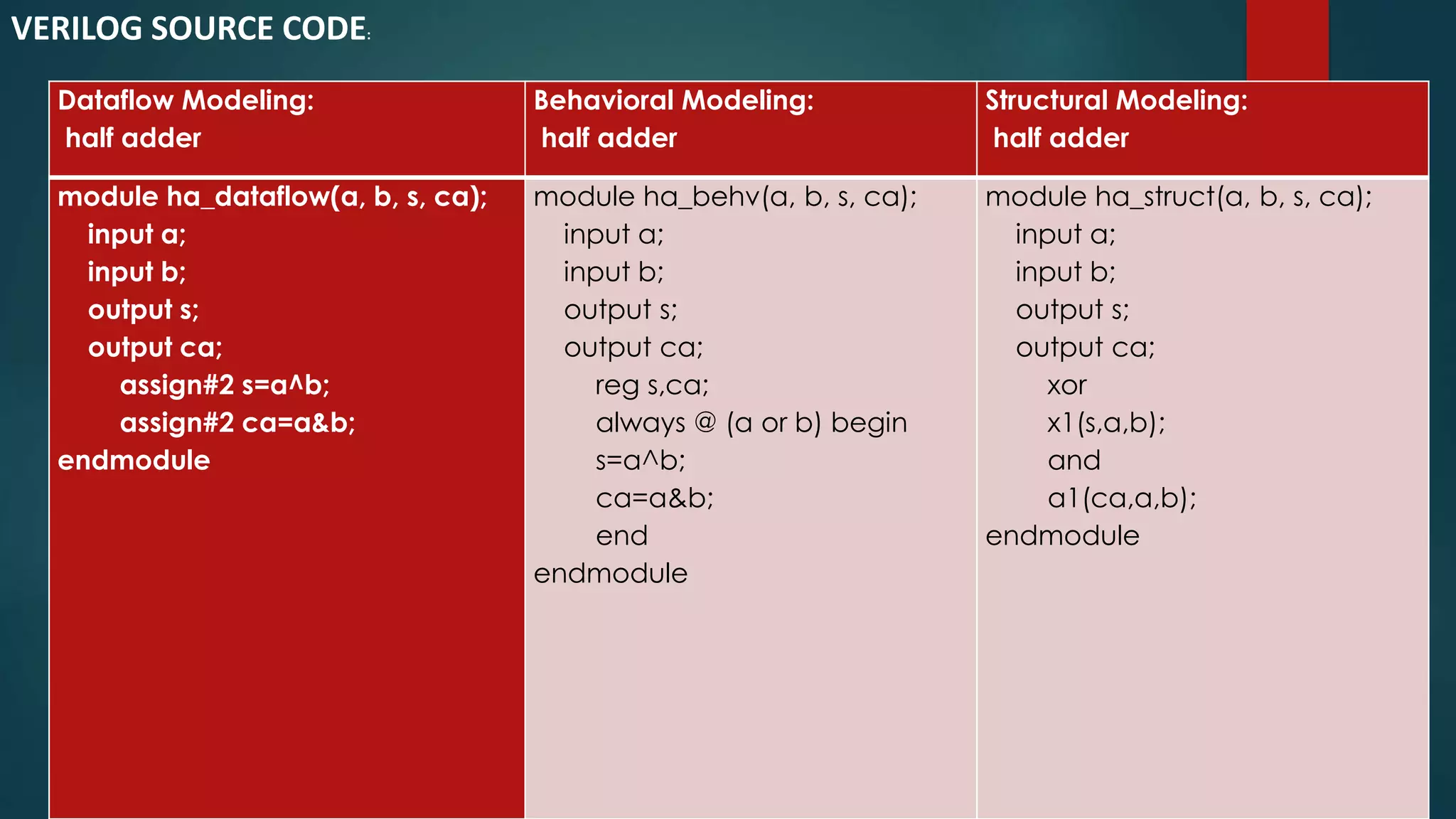

VERILOG SOURCE CODE:

module logicgates1(a, b, c);

input a;

input b;

OUTPUT: [6:0] c;

assign c[0]= a & b;

assign c[1]= a | b;

assign c[2]= ~(a & b);

assign c[3]= ~(a | b);

assign c[4]= a ^ b;

assign c[5]= ~(a ^ b);

assign c[6]= ~ a;

endmodule](https://image.slidesharecdn.com/vhdlbasic-unit-2-150317072543-conversion-gate01/75/Vhdl-basic-unit-2-16-2048.jpg)