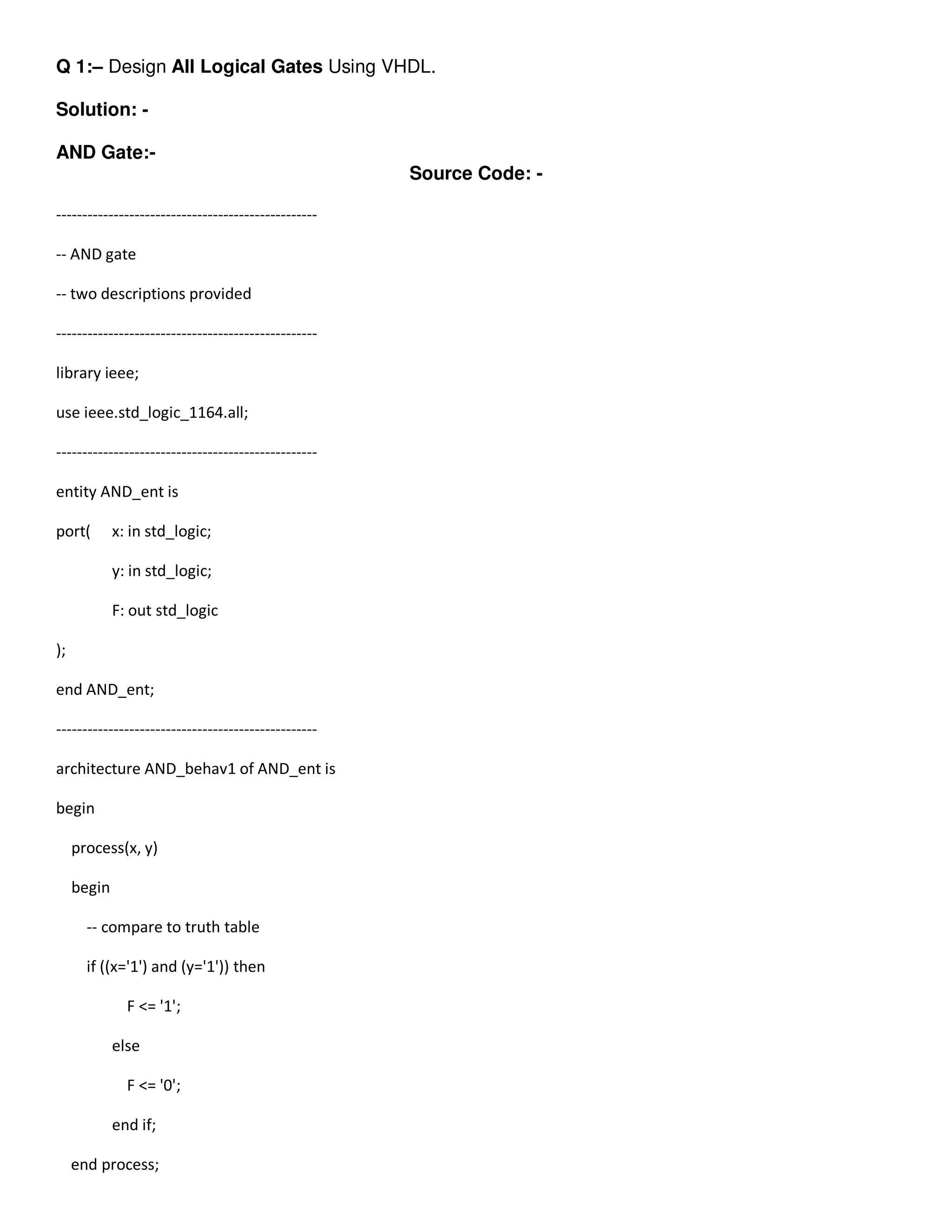

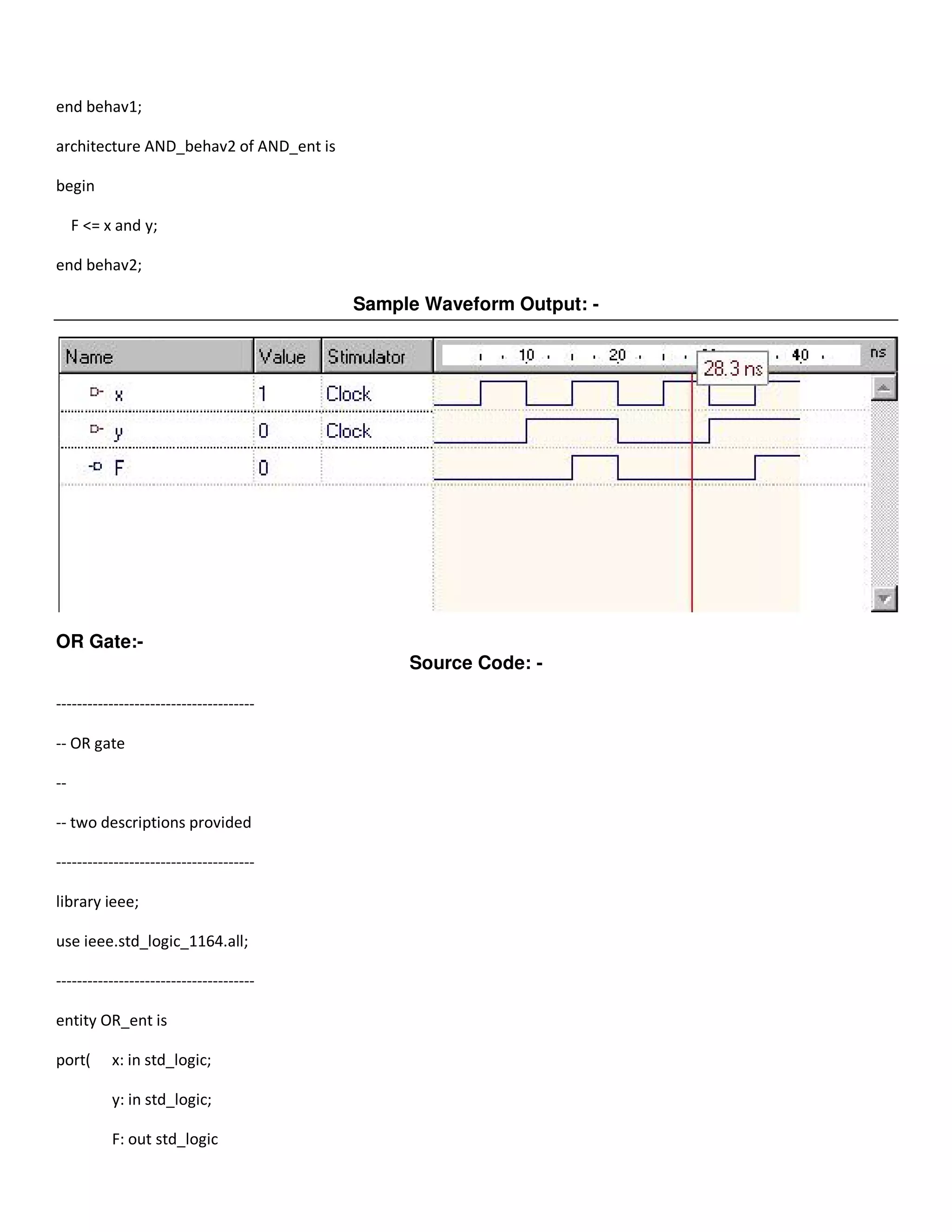

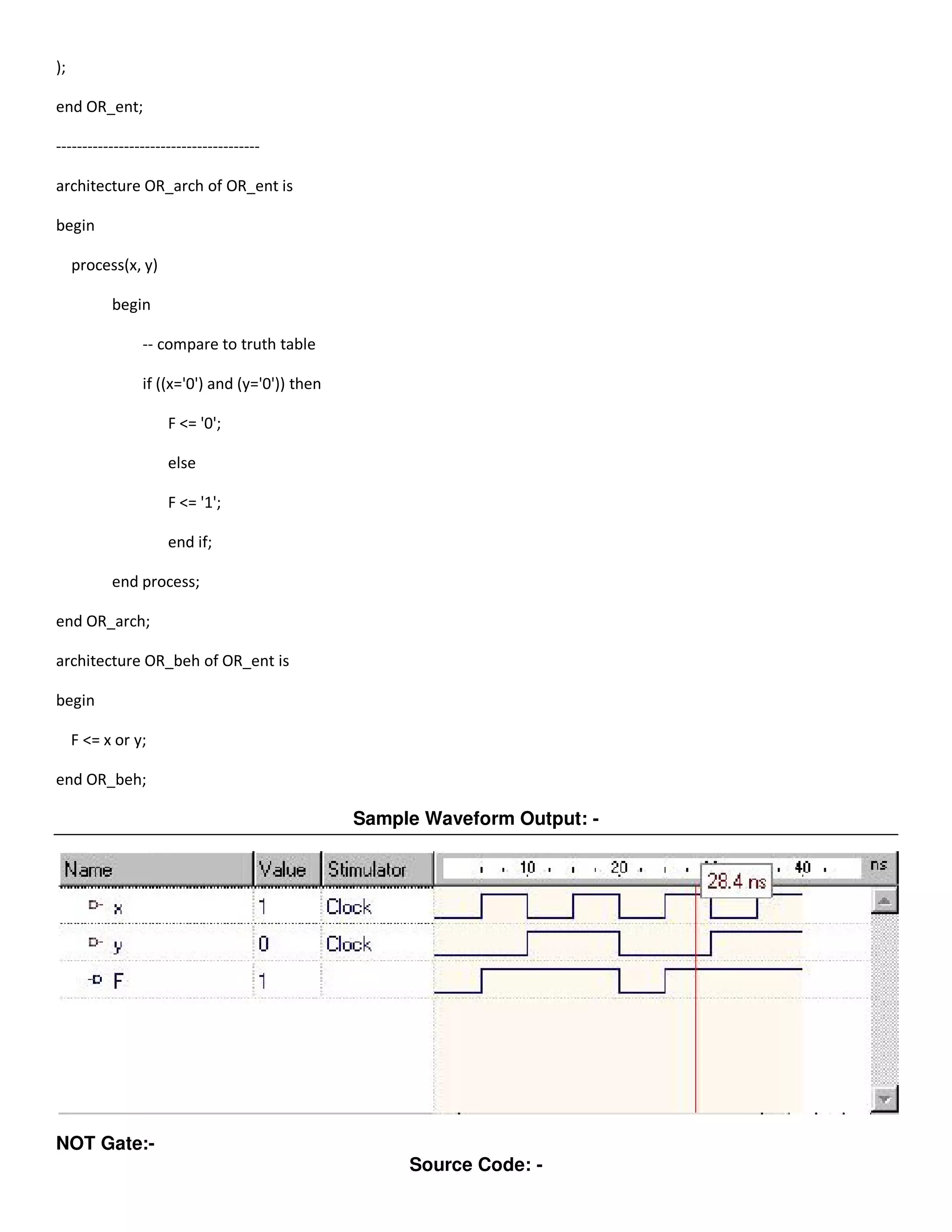

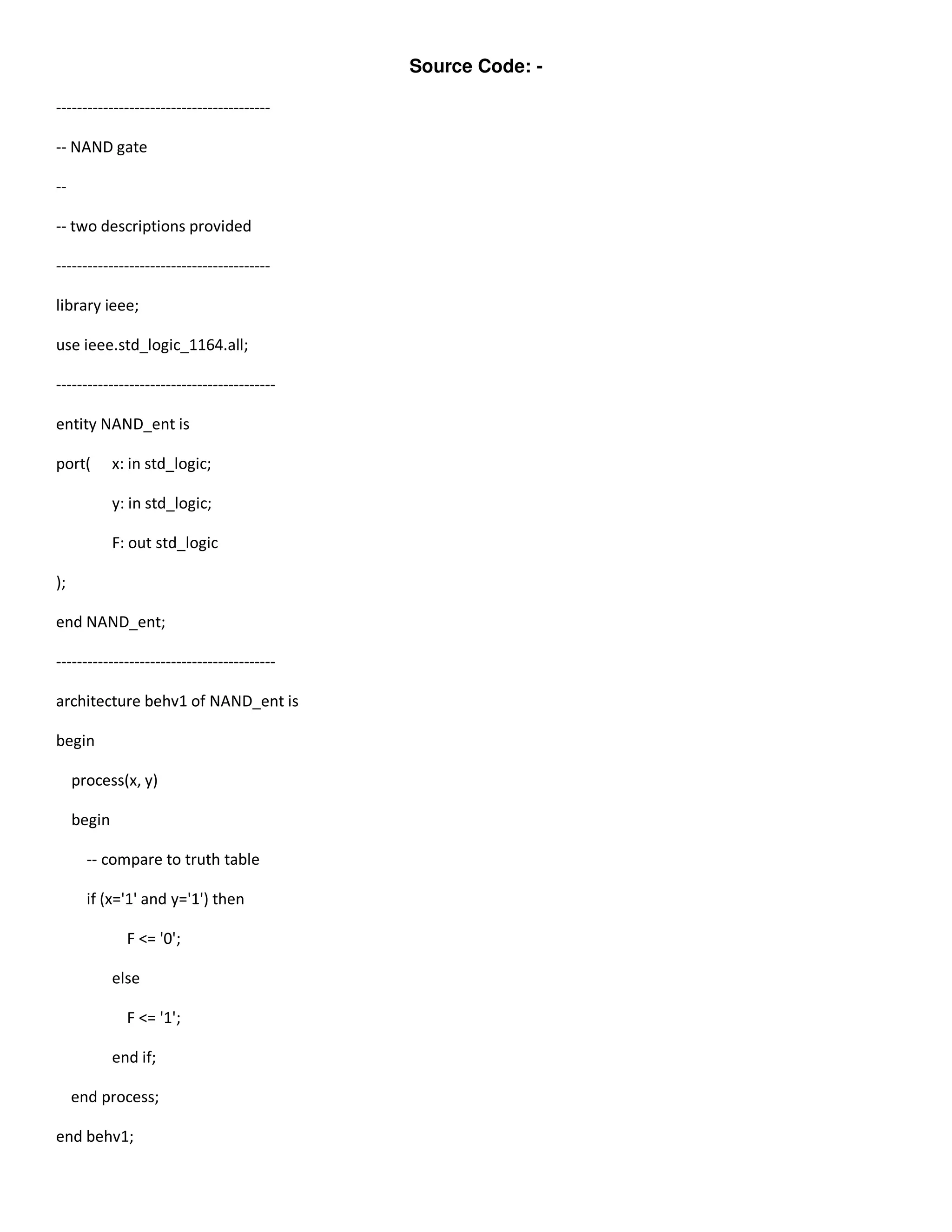

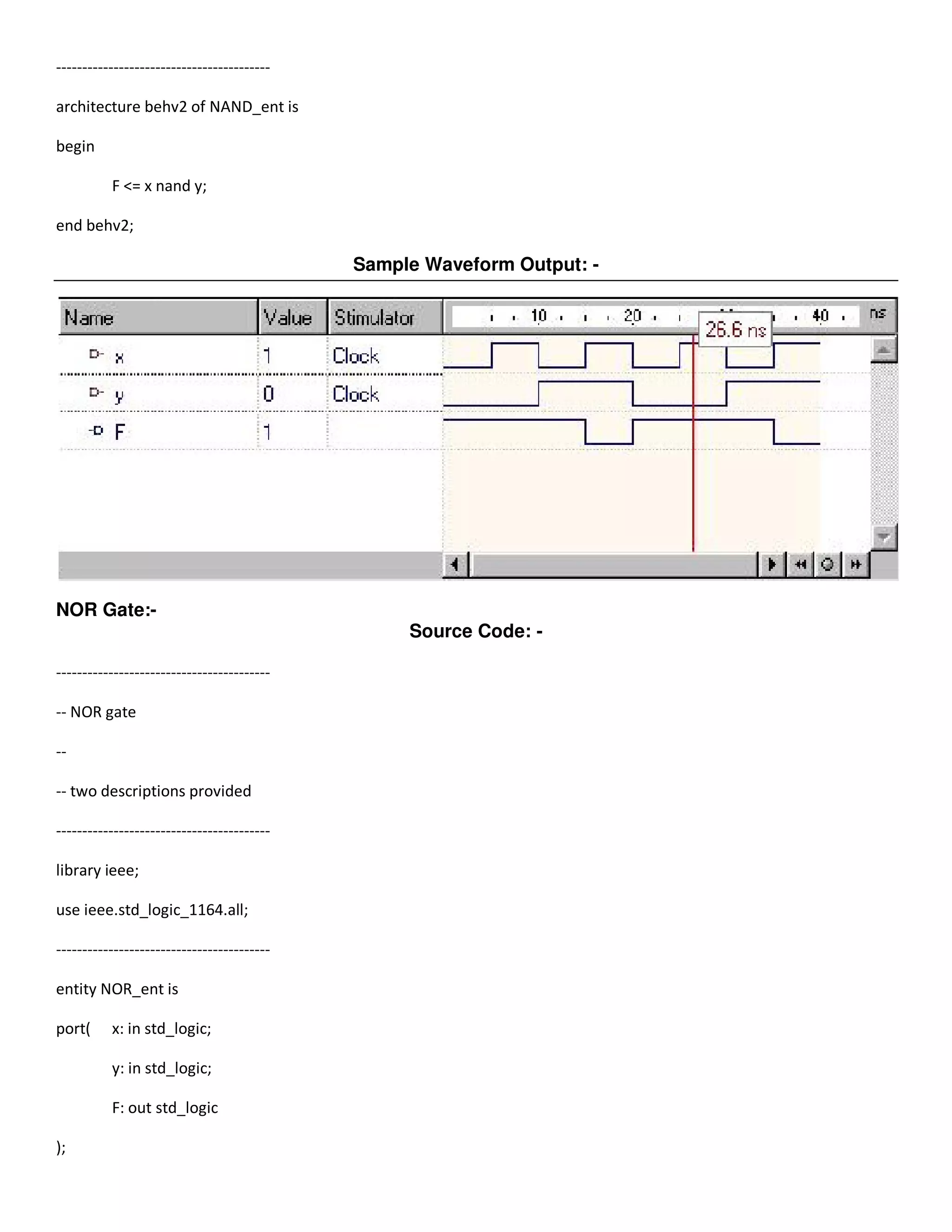

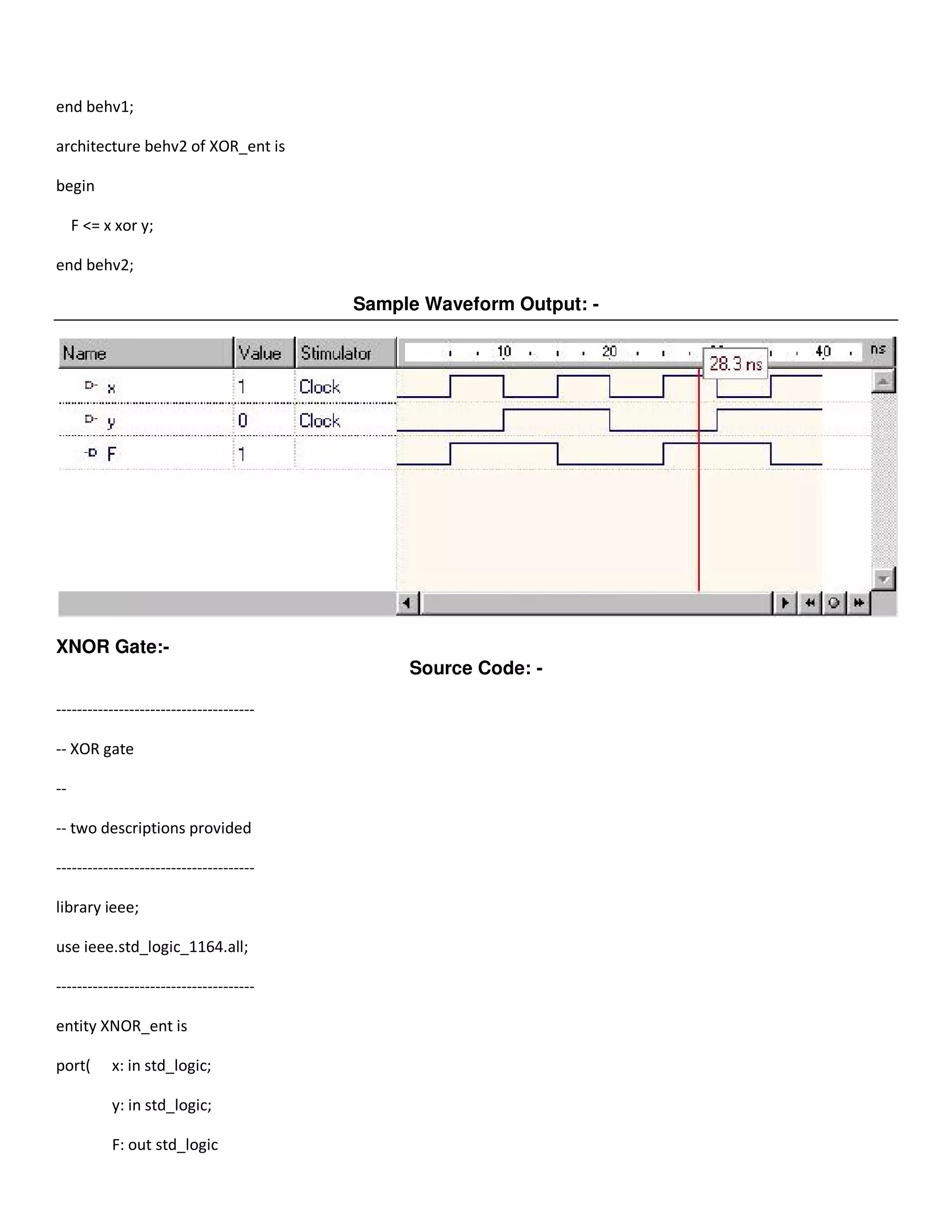

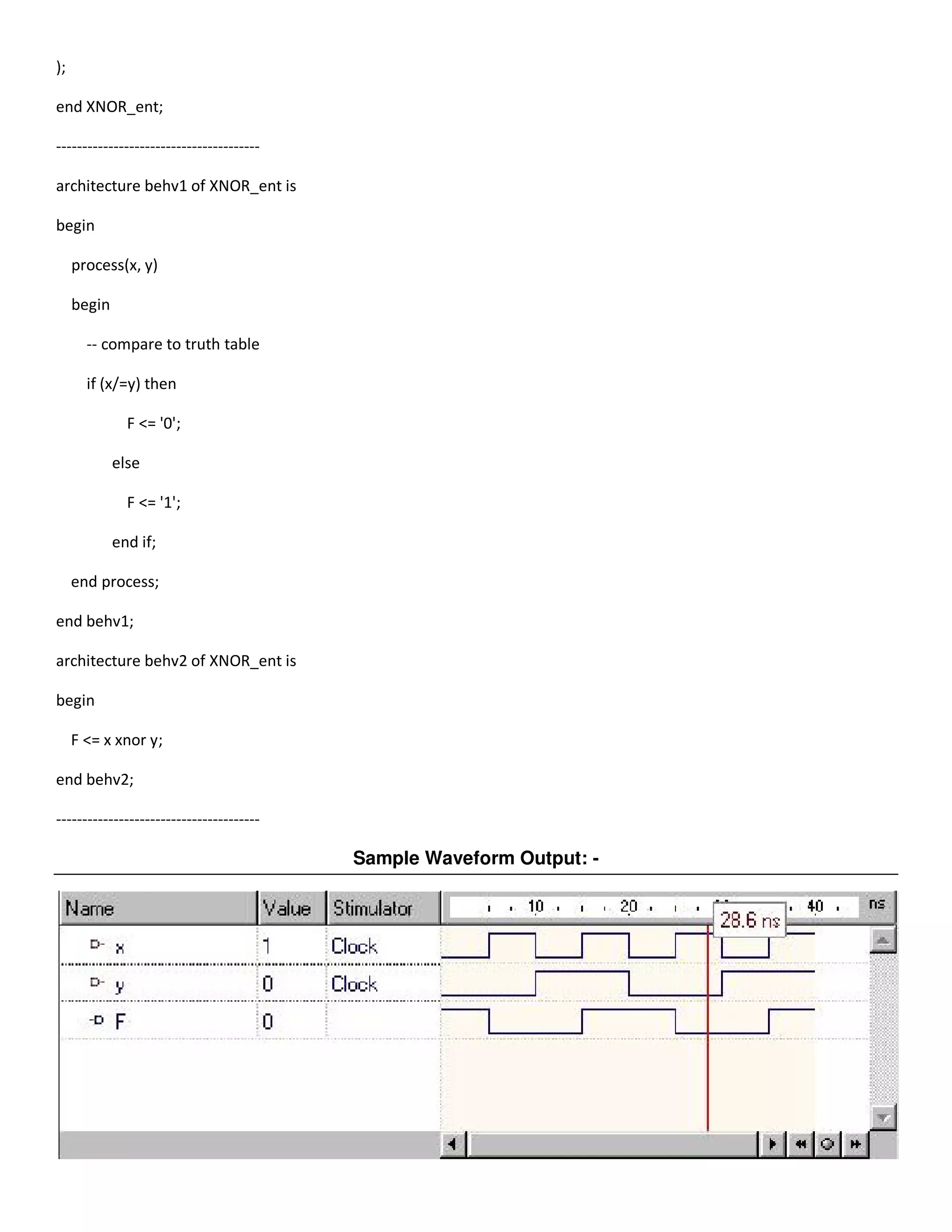

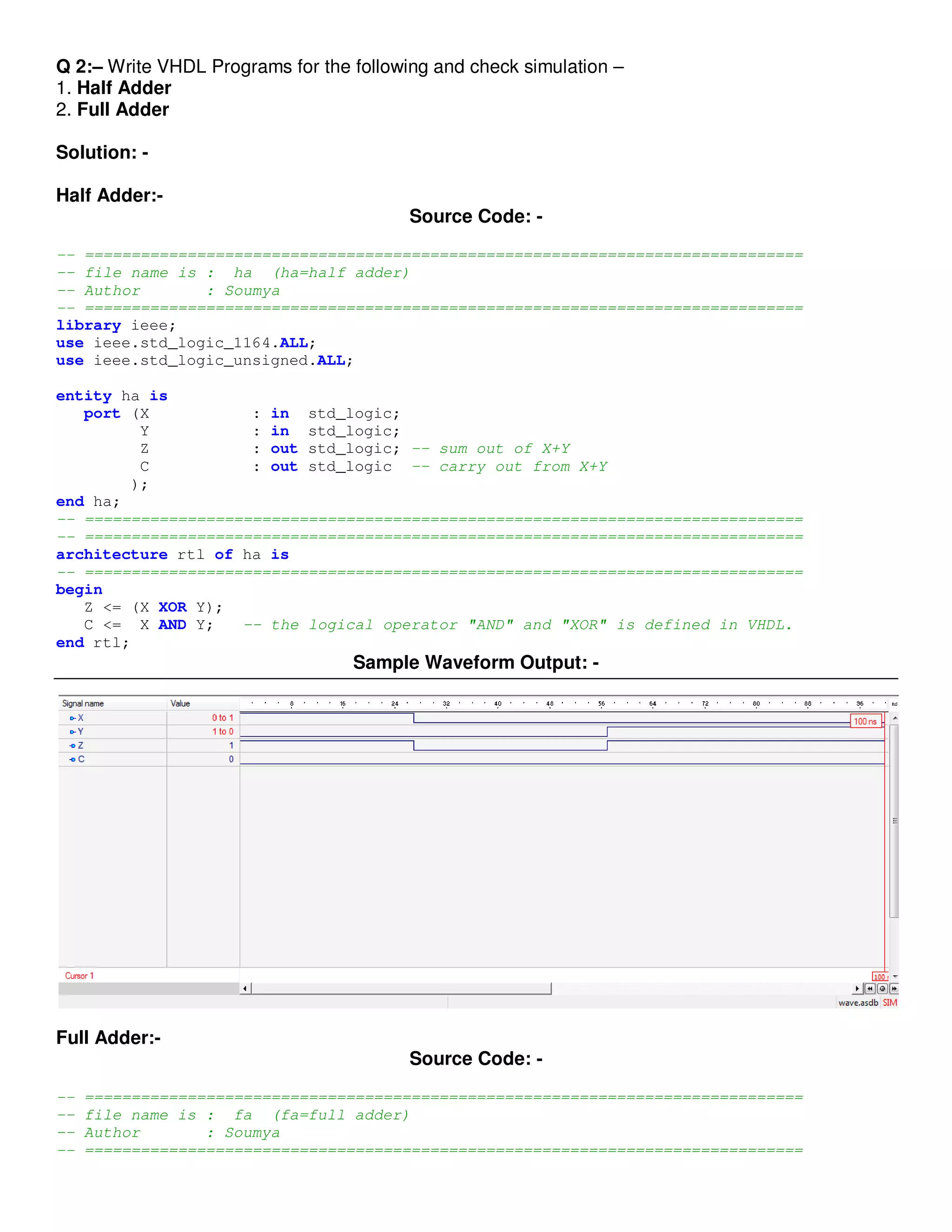

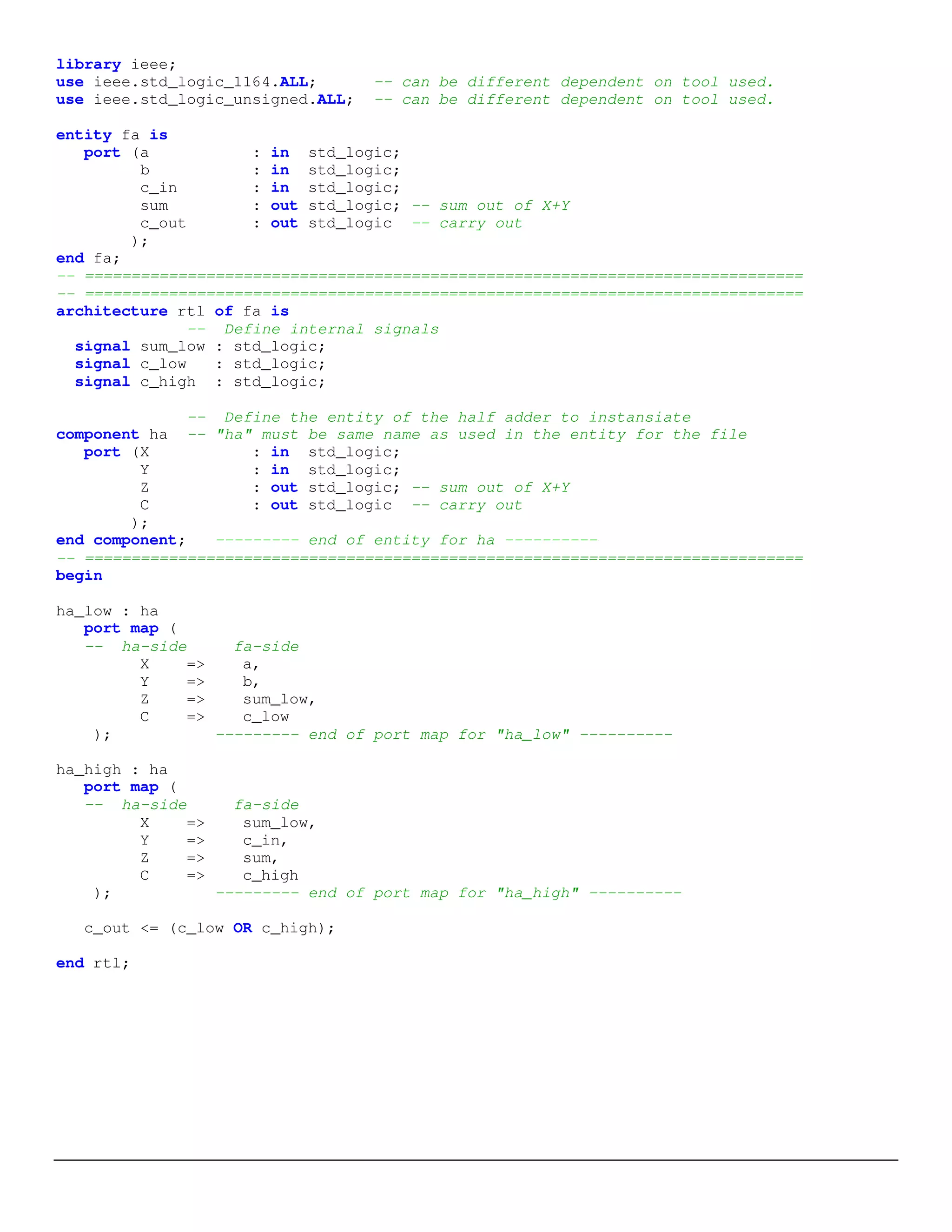

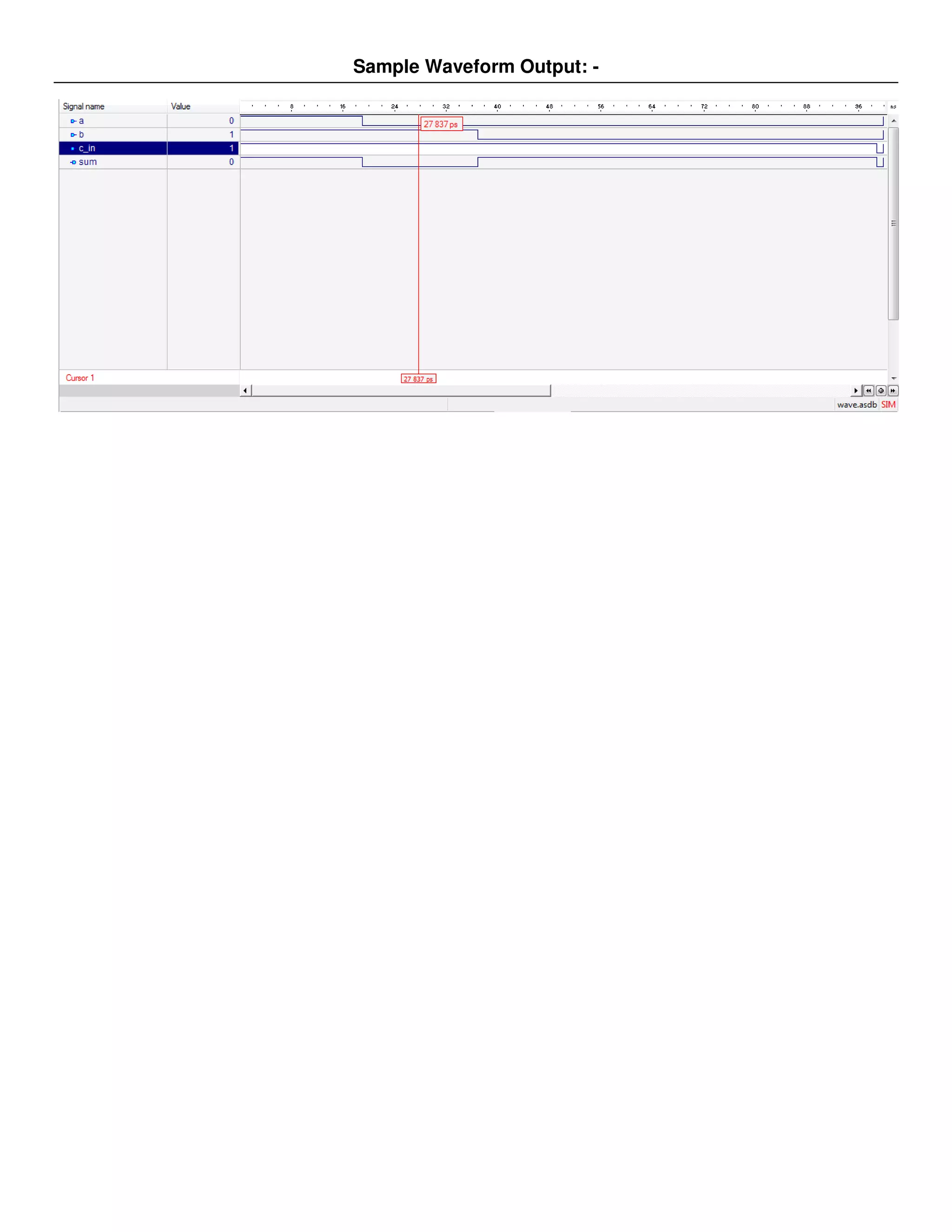

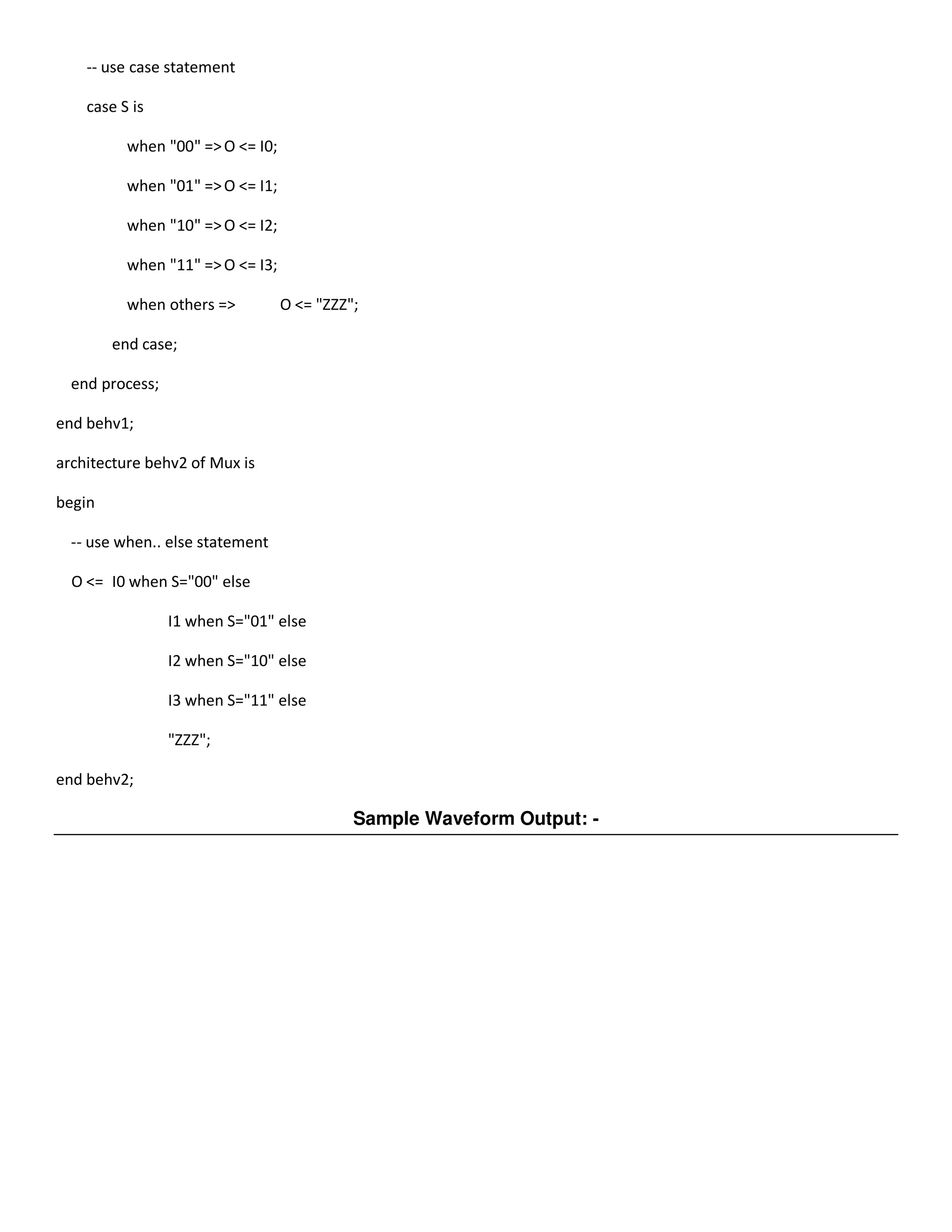

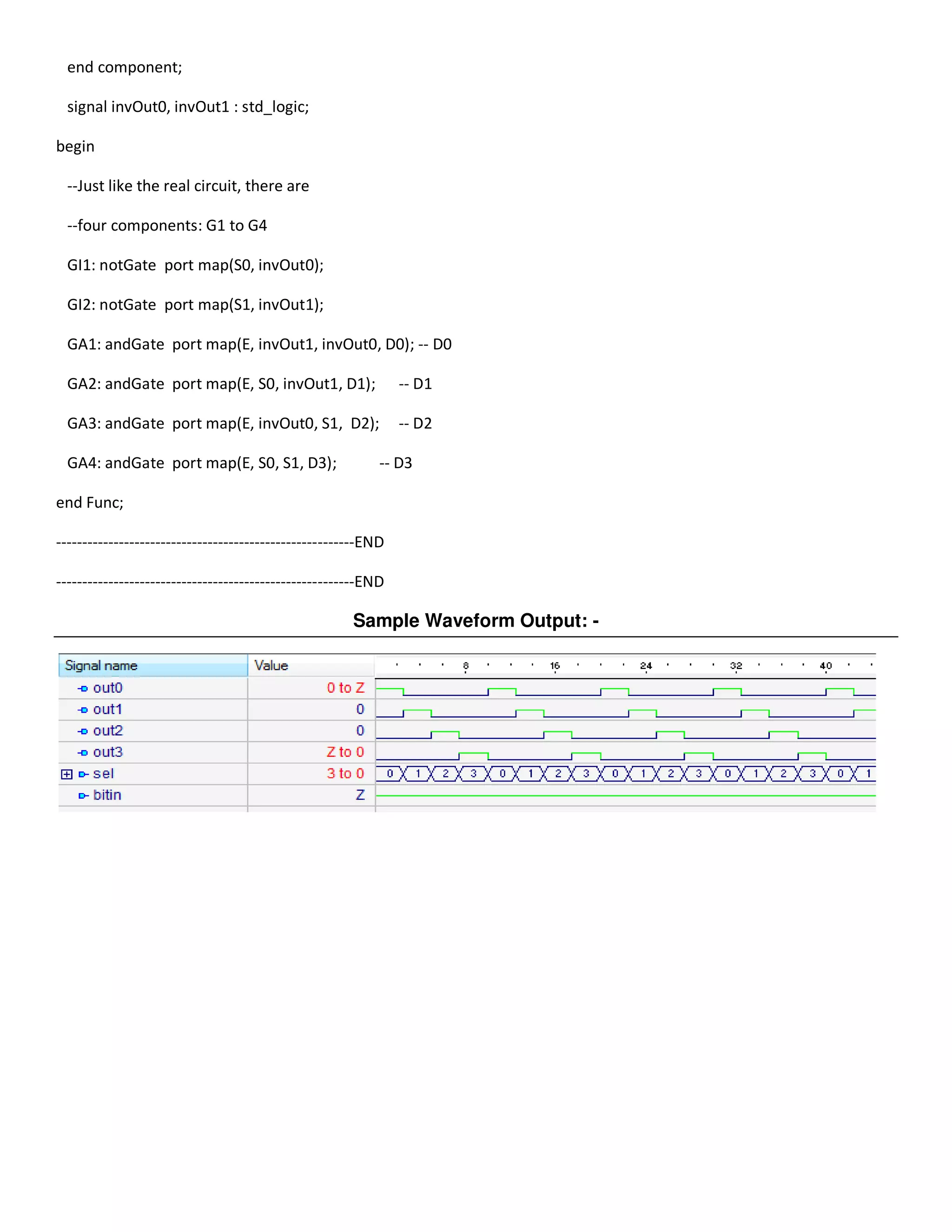

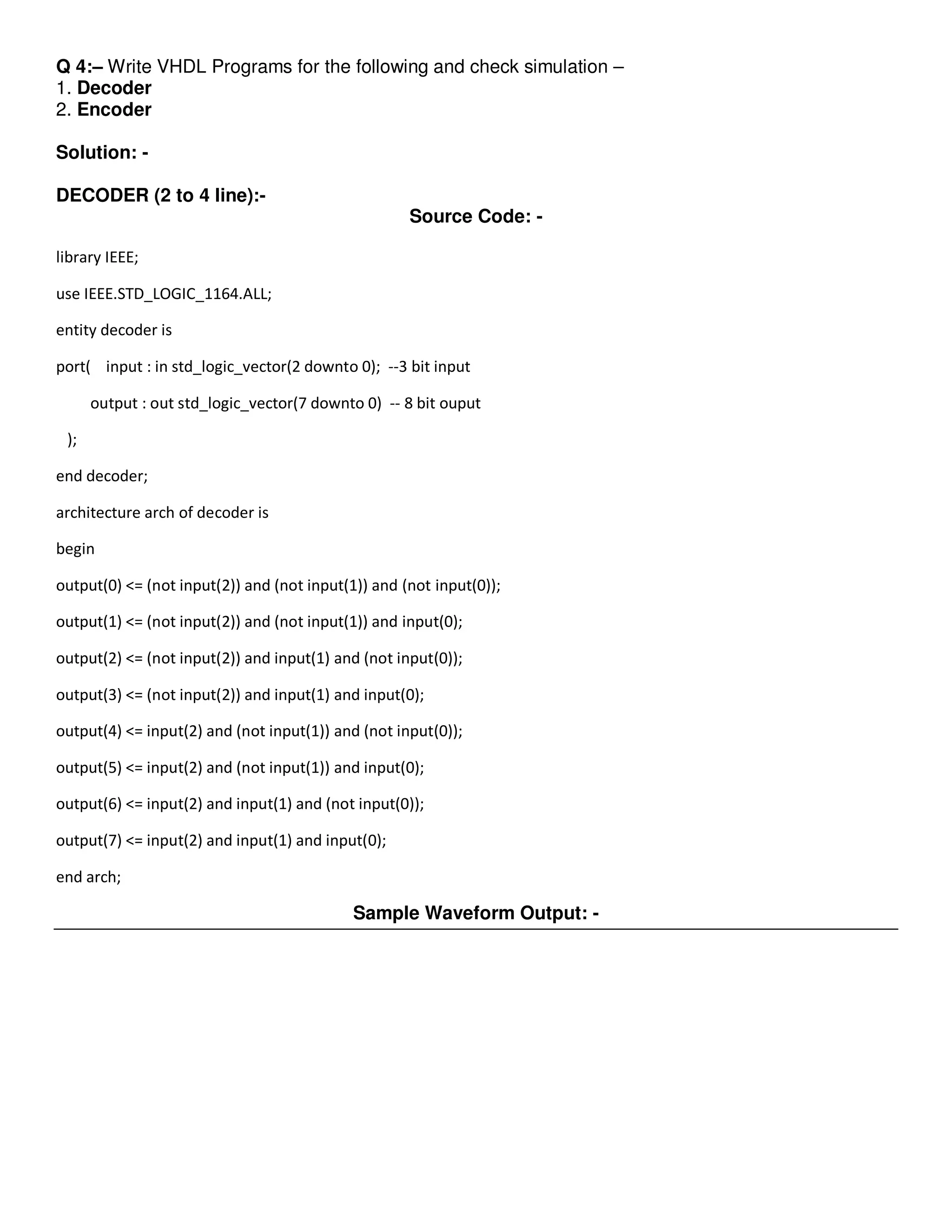

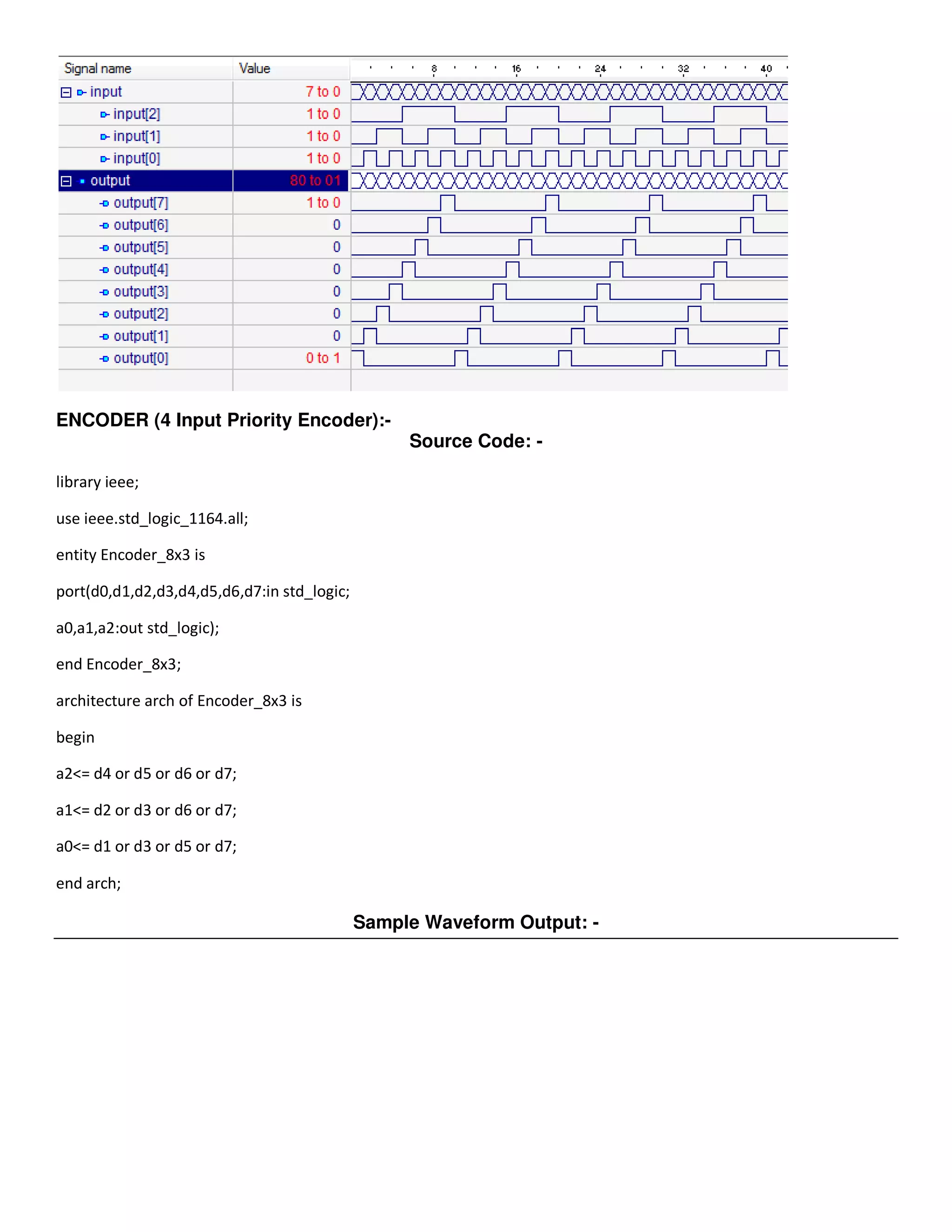

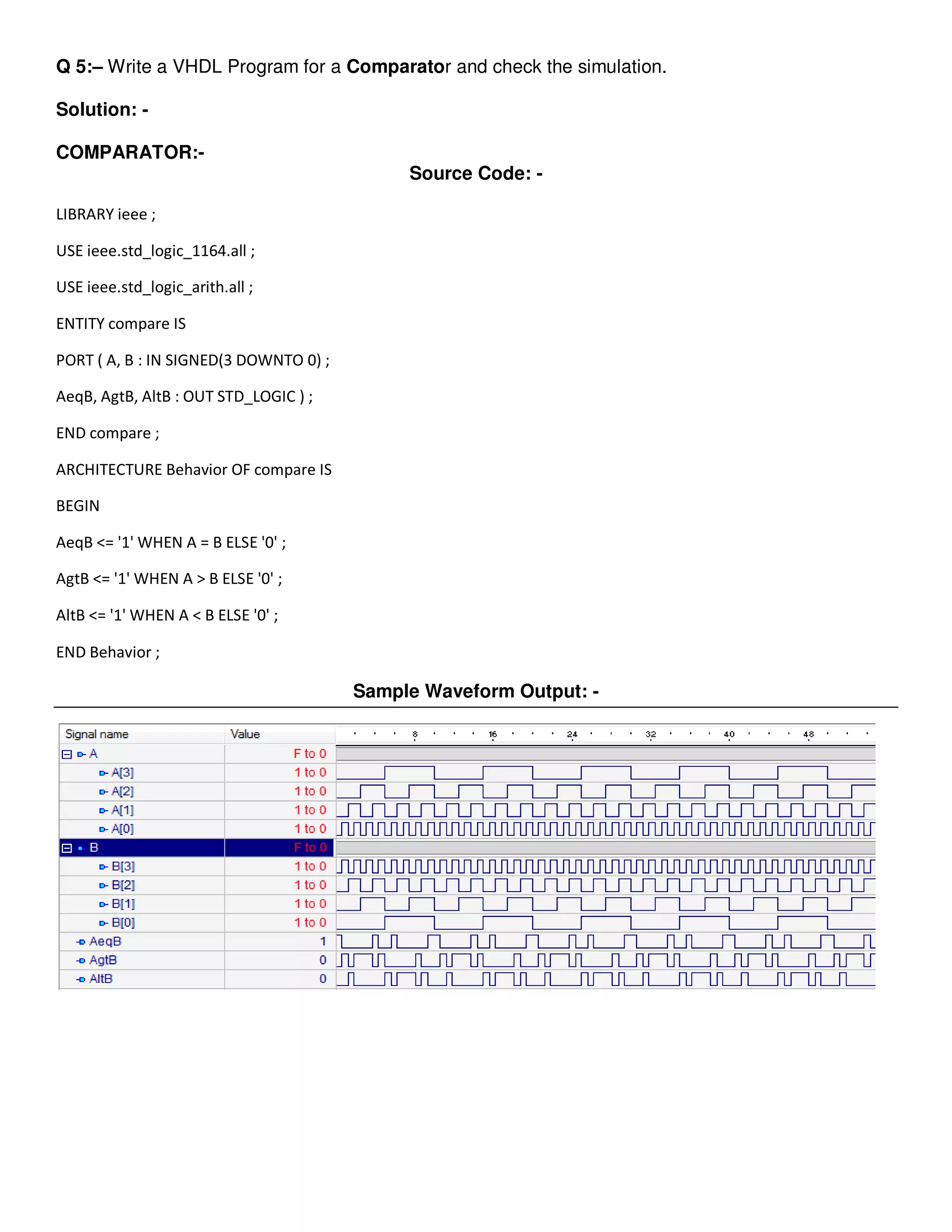

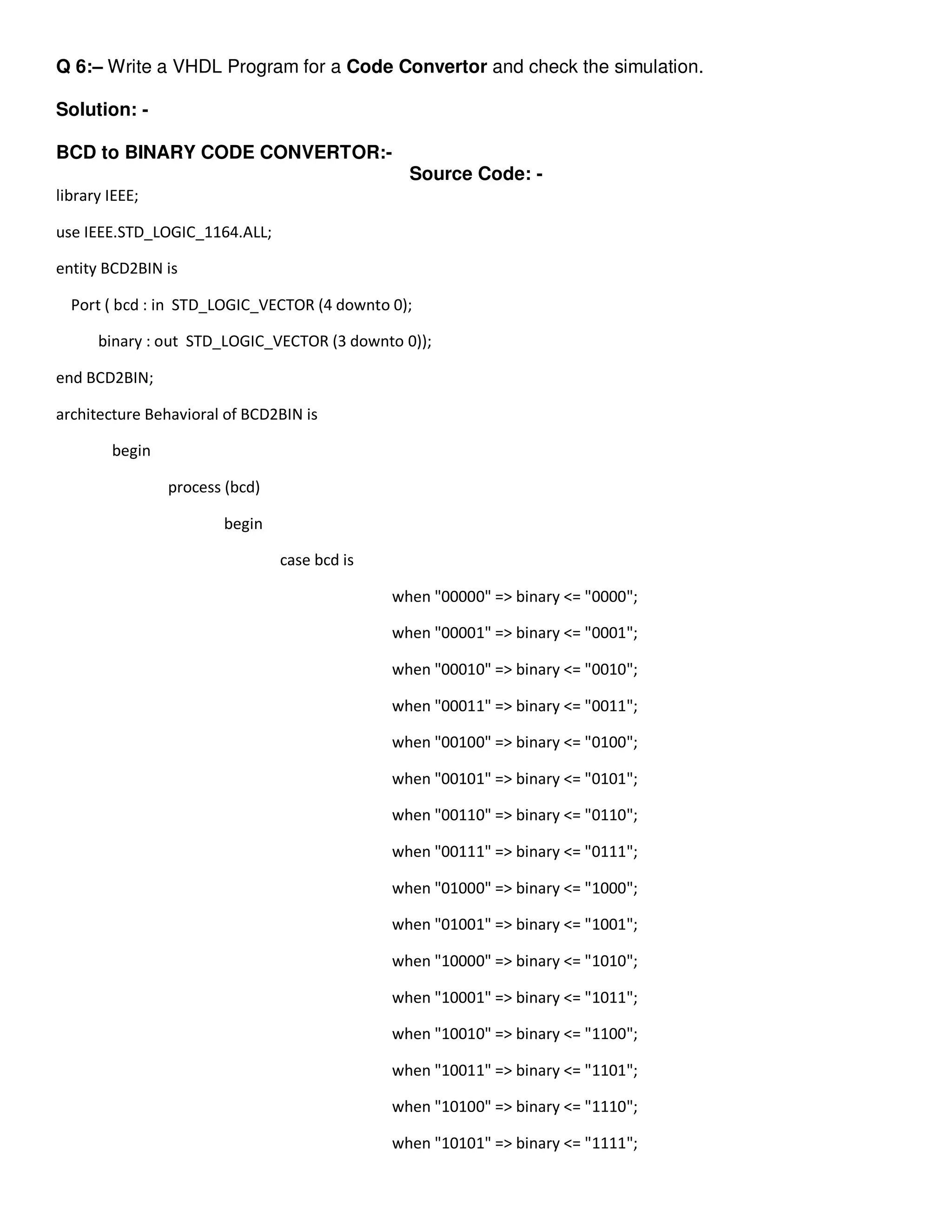

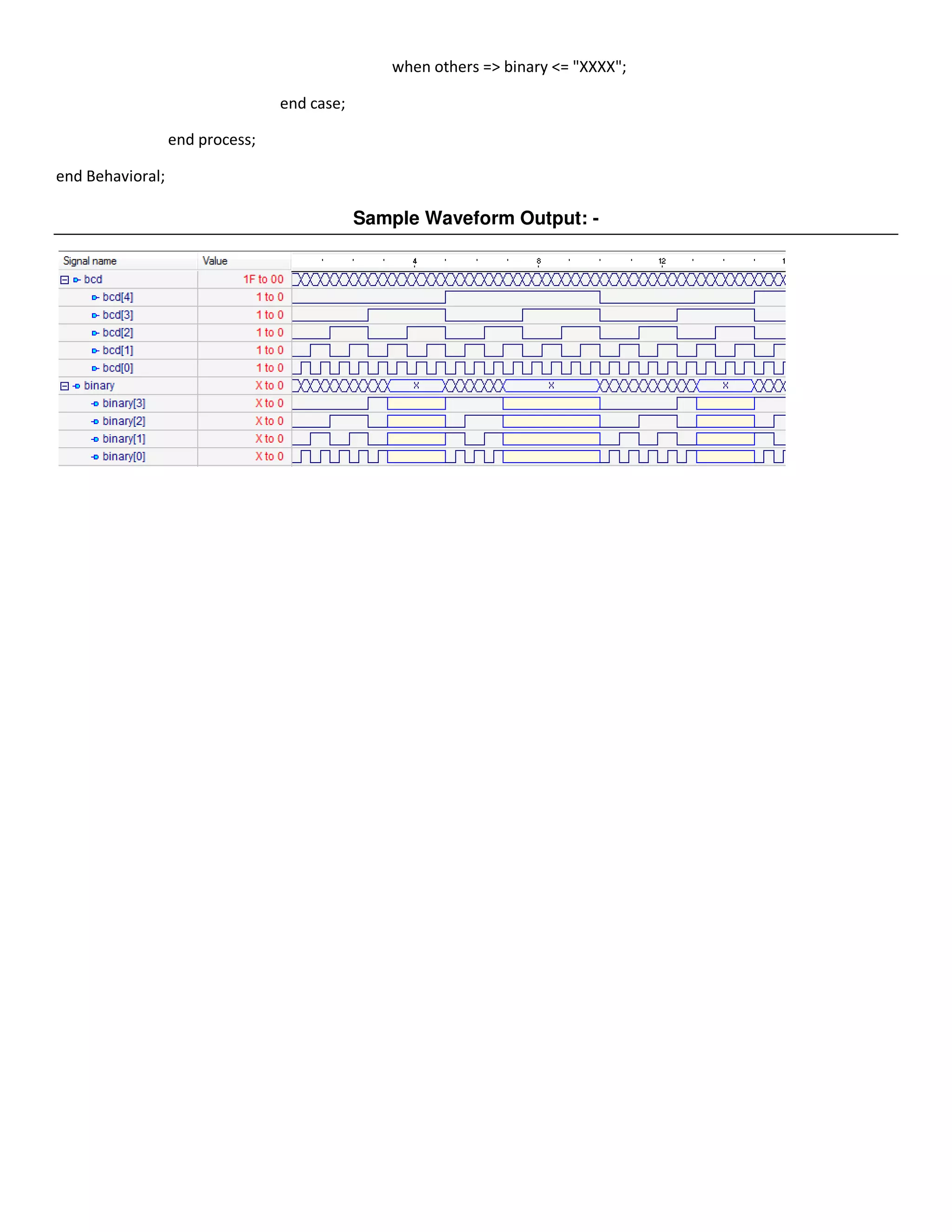

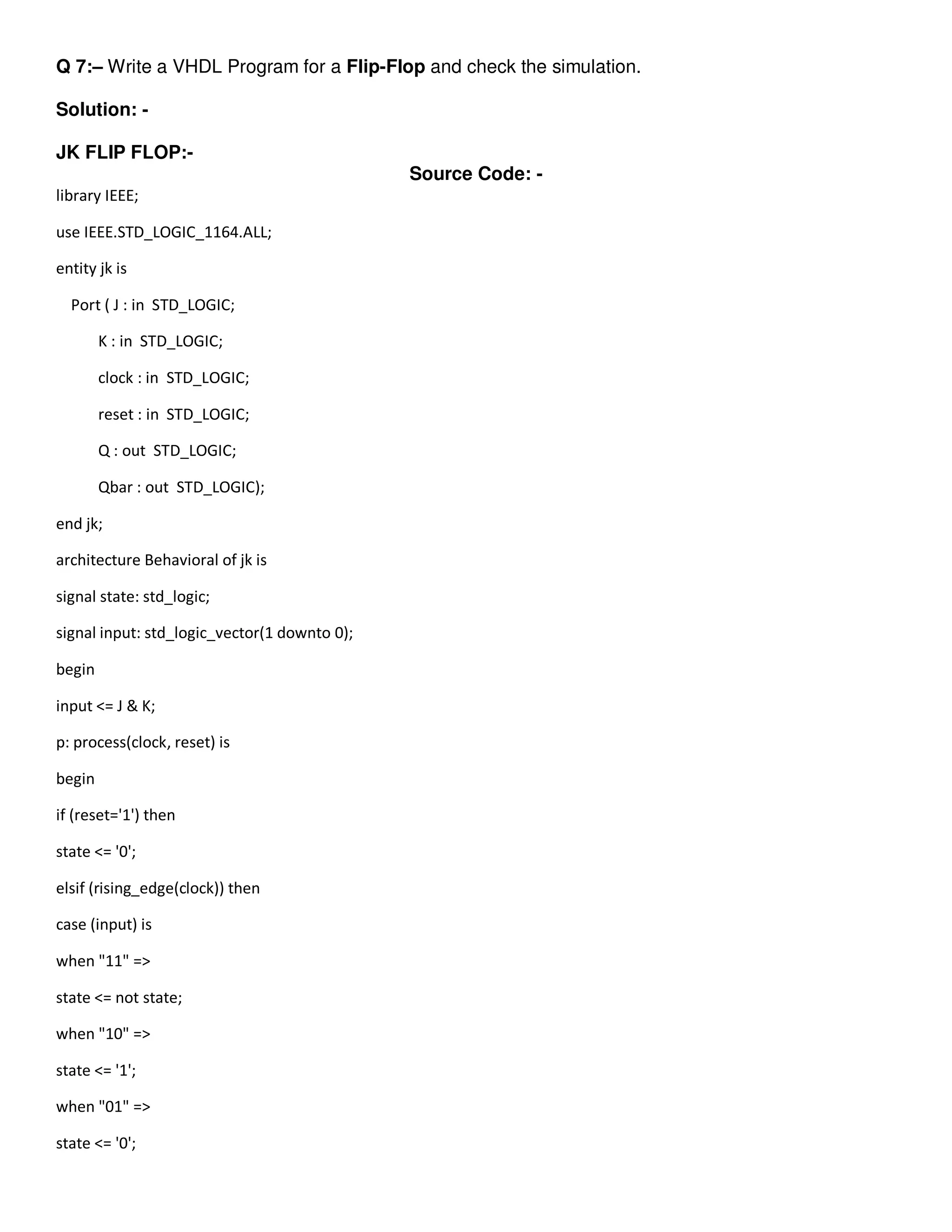

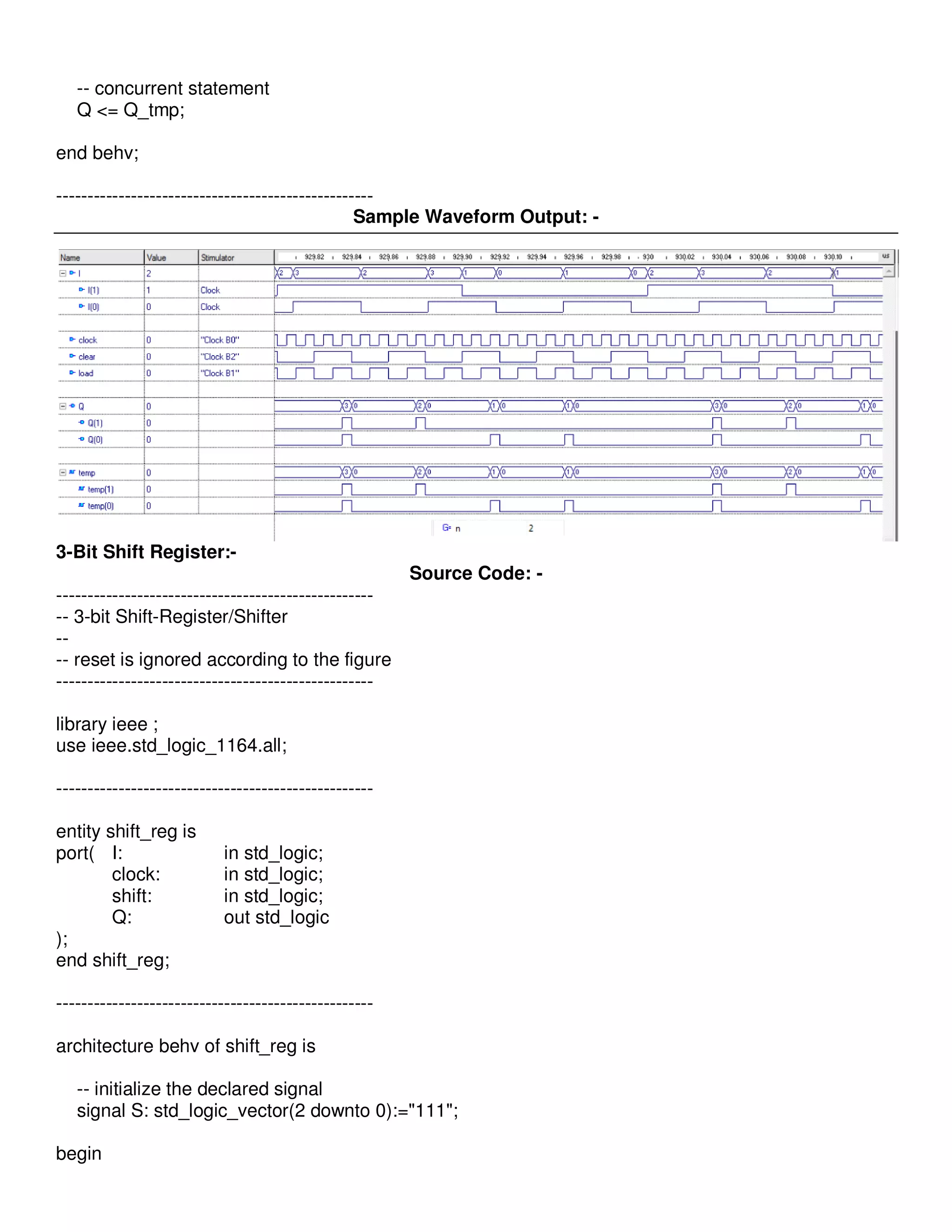

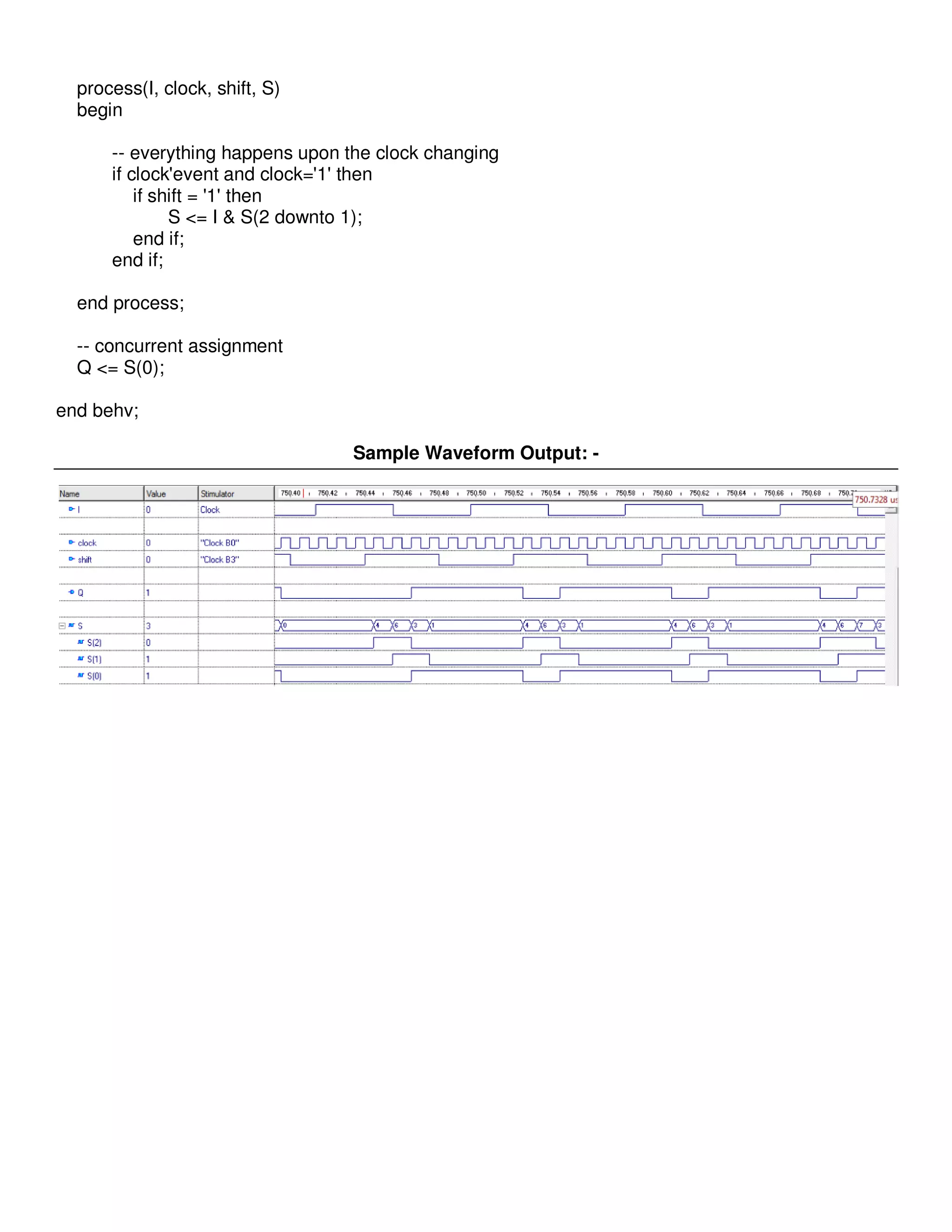

The document provides VHDL code to design various logic gates and combinational logic circuits. It includes code for AND, OR, NOT, NAND, NOR, XOR, XNOR gates. It also includes code for half adder, full adder, multiplexer, demultiplexer, decoder and encoder circuits. For each circuit, it provides the VHDL code along with a brief description and expected output waveforms.