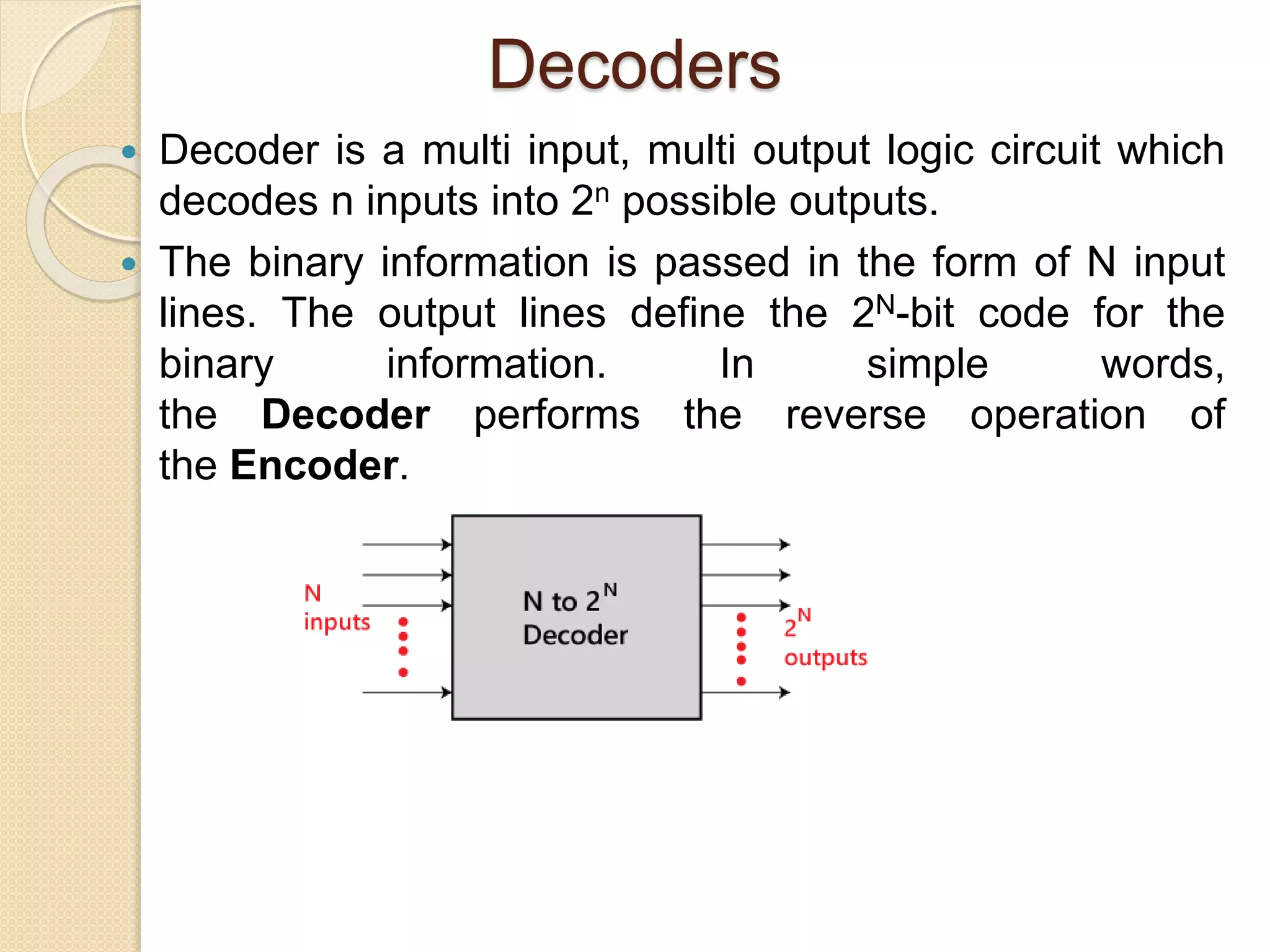

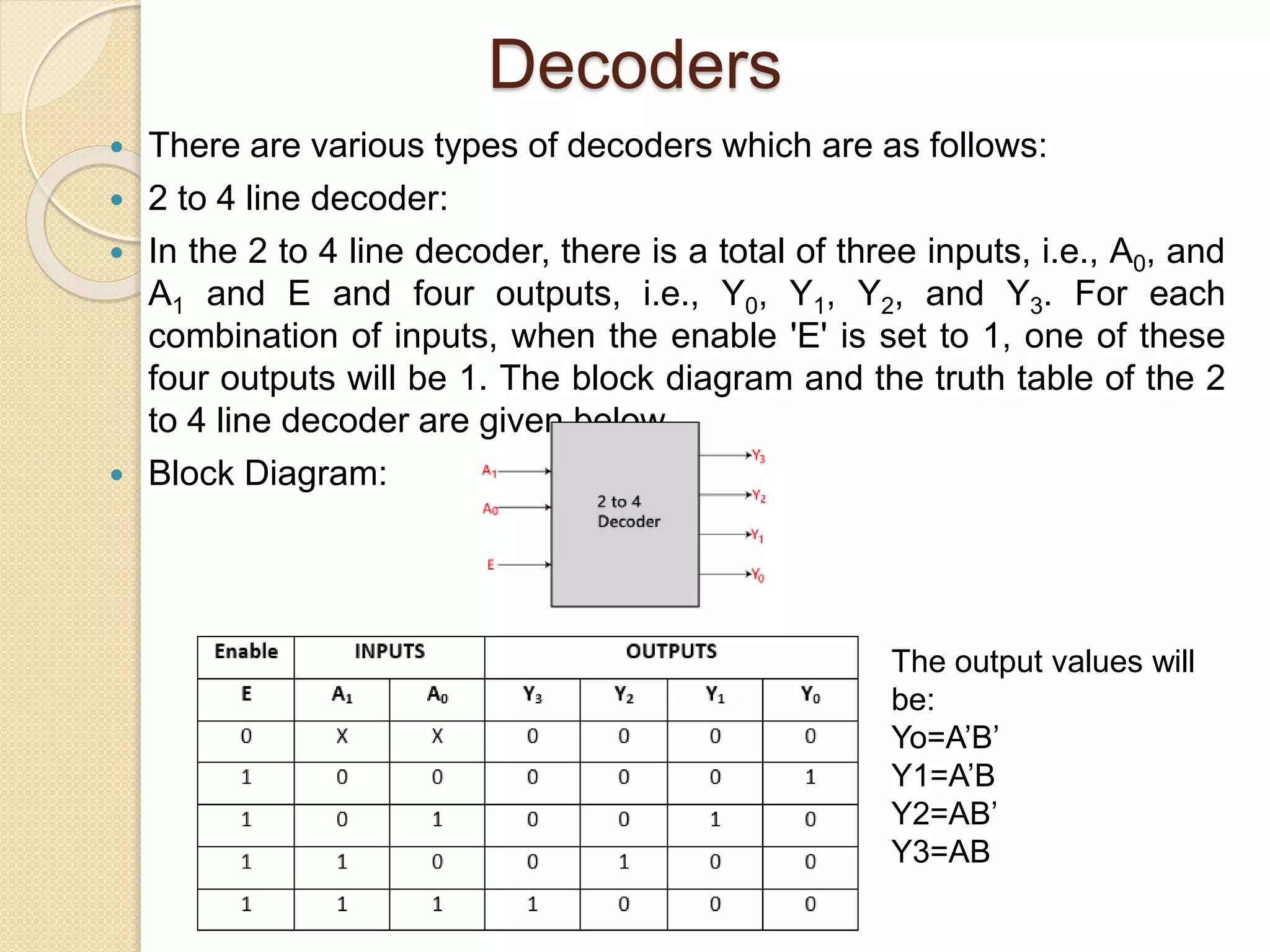

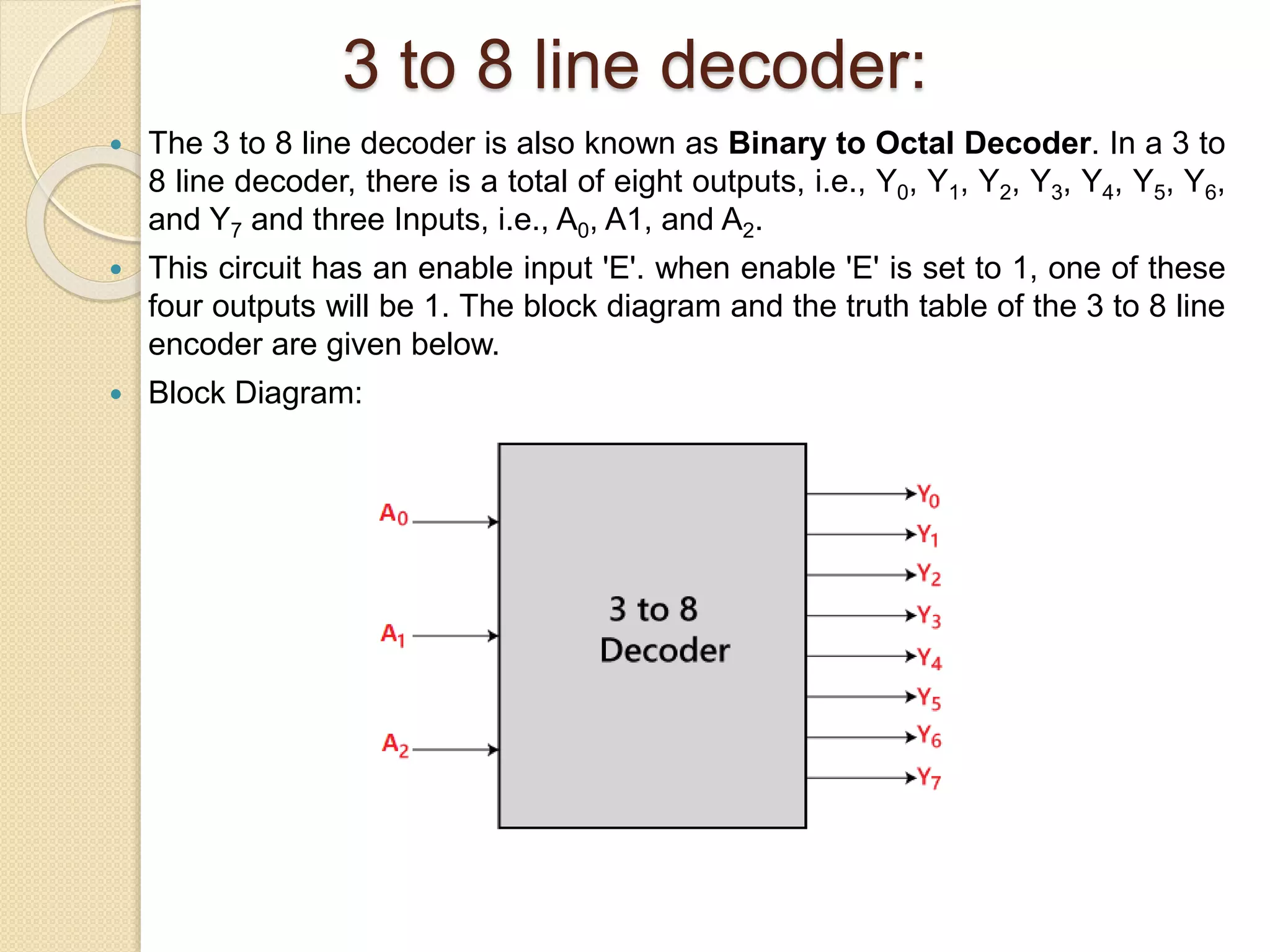

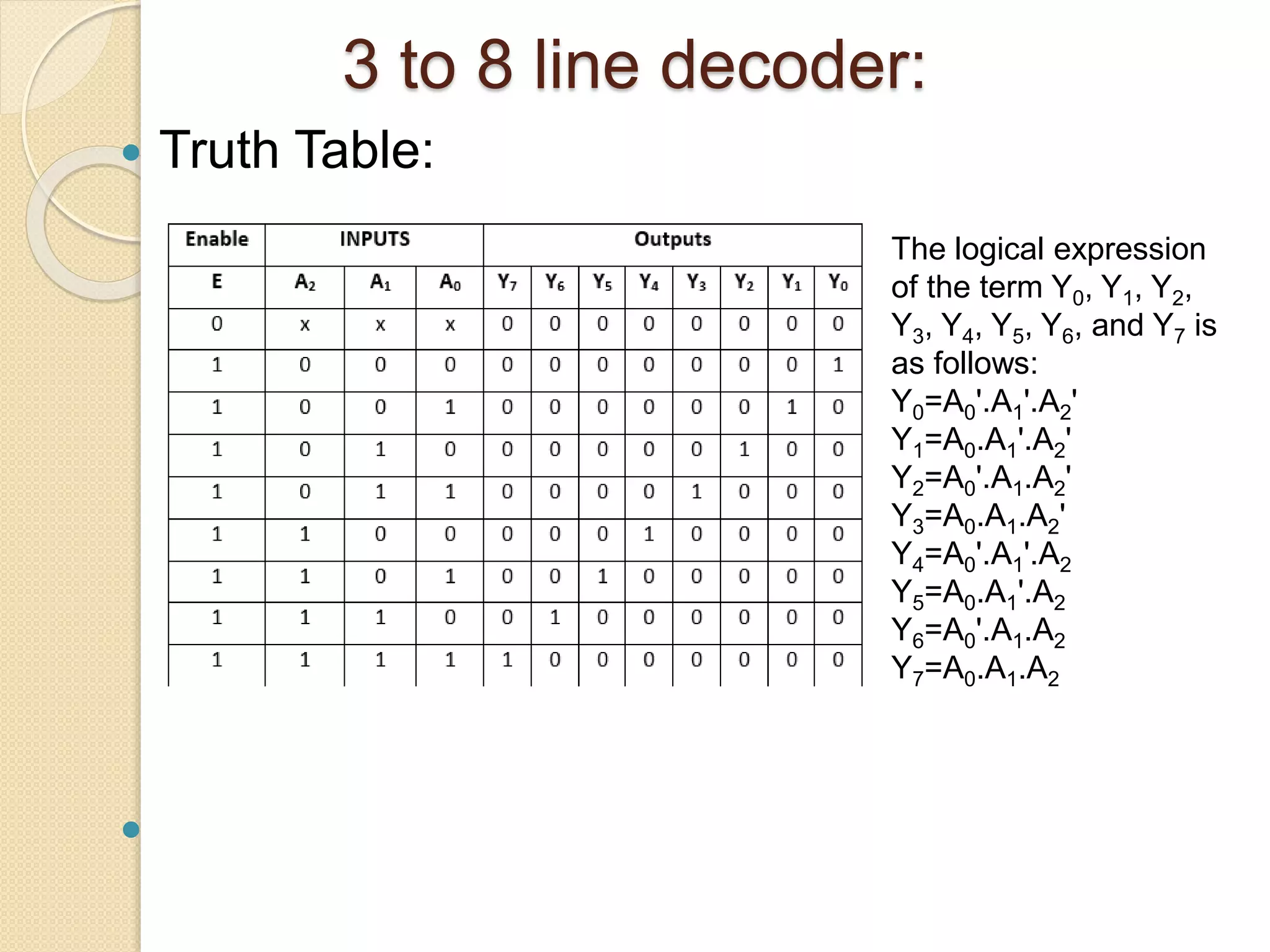

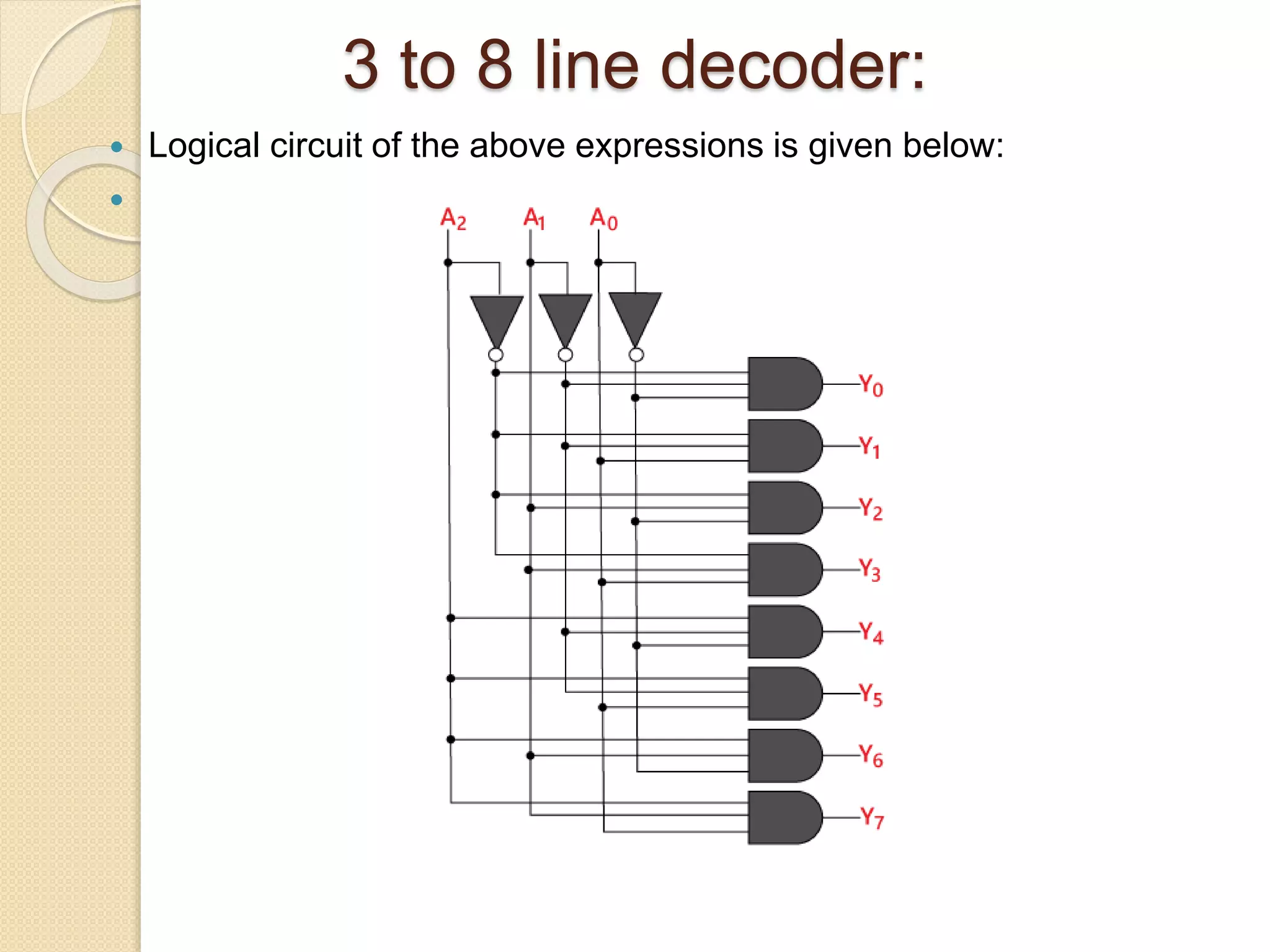

A decoder is a logic circuit that takes binary input and provides an output based on the input. It performs the reverse operation of an encoder. There are different types of decoders including a 2 to 4 line decoder and a 3 to 8 line decoder. A 2 to 4 line decoder has 3 inputs (A0, A1, E) and 4 outputs (Y0, Y1, Y2, Y3). It uses AND gates to activate one output based on the input. A 3 to 8 line decoder has 3 inputs (A0, A1, A2), 8 outputs (Y0-Y7), and an enable input. It uses AND gates and logic expressions to activate one of the 8 outputs based on the