JFET IDE

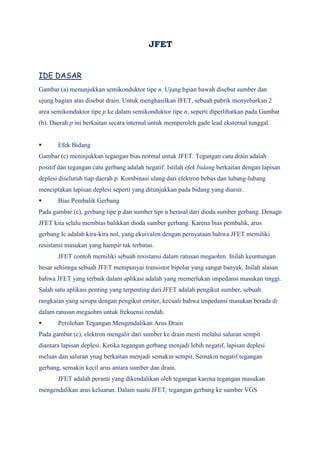

- 1. JFET IDE DASAR Gambar (a) menunjukkan semikonduktor tipe n. Ujung bgian bawah disebut sumber dan ujung bagian atas disebut drain. Untuk menghasilkan JFET, sebuah pabrik menyebarkan 2 area semikonduktor tipe p ke dalam semikonduktor tipe n, seperti diperlihatkan pada Gambar (b). Daerah p ini berkaitan secara internal untuk memperoleh gade lead eksternal tunggal. Efek Bidang Gambar (c) meninjukkan tegangan bias normal untuk JFET. Tegangan catu drain adalah positif dan tegangan catu gerbang adalah negatif. Istilah efek bidang berkaitan dengan lapisan deplesi diseluruh tiap daerah p. Kombinasi ulang dari elektron bebas dan lubang-lubang menciptakan lapisan deplesi seperti yang ditunjukkan pada bidang yang diarsir. Bias Pembalik Gerbang Pada gambar (c), gerbang tipe p dan sumber tipr n berasal dari dioda sumber gerbang. Denagn JFET kita selalu membias balikkan dioda sumber gerbang. Karena bias pembalik, arus gerbang Ic adalah kira-kira nol, yang ekuivalen dengan pernyataan bahwa JFET memiliki resistansi masukan yang hampir tak terbatas. JFET contoh memiliki sebuah resistansi dalam ratusan megaohm. Inilah keuntungan besar sehinnga sebuah JFET mempunyai transistor bipolar yang sangat banyak. Inilah alasan bahwa JFET yang terbaik dalam aplikasi adalah yang memerlukan impedansi masukan tinggi. Salah satu aplikasi penting yang terpenting dari JFET adalah pengikut sumber, sebuah rangkaian yang serupa dengan pengikut emiter, kecuali bahwa impedansi masukan berada di dalam ratusan megaohm untuk frekuensi rendah. Perolehan Tegangan Mengendalikan Arus Drain Pada gambar (c), elektron mengalir dari sumber ke drain mesti melalui saluran sempit diantara lapisan deplesi. Ketika tegangan gerbang menjadi lebih negatif, lapisan deplesi meluas dan saluran ynag berkaitan menjadi semakin sempit. Semakin negatif tegangan gerbang, semakin kecil arus antara sumber dan drain. JFET adalah peranti yang dikendalikan oleh tegangan karena tegangan masukan mengendalikan arus keluaran. Dalam suatu JFET, tegangan gerbang ke sumber VGS

- 2. DRAIN n GATE p p n SUMBER (a) (b) Gambar (a) Bagian dari JFET ; (b) JFET gerbang tunggal DRAIN n + GATE VPP - p p - VGG n SOURCE + Gambar 13-2 Pembiasan JFET normal Menentukan seberapa besar aliran arus antara sumber dan drain ketika VGS menjadi nol, aliran drain maksimum menuju JFET. Di sisi lain, jika VGS menjadi cukup negatif, sentuhan lapisan deplesi dan arus drain akan mati Simbol Skematik JFET pada gambar (c) adalah sebuah saluran JFET karena saluran antara sumber dan drain adalah semikonduktor tipe n. Gambar (d) menunjukkan sumbol skematik untuk sebuah JFET saluaran n. Pada banyak aplikasi frekuensi rendah, sumber dan drain dapat saling

- 3. dipertukarkan karena nada dapat menggunakan salah satu ujung sebagai sumber dan ujung yang lainnya sebagai drain. Terminal sumber dan drain dapat dipertukarkan pada frekuensi tinngi. Hampir selalu, pabrik meminimumkan kapasitansi internal pada sisi drain dari JFET. Dengan kata lain, kapasitansi antara gerbang dan drain lebih kecil daripada kapasitansi antara gerbang dan sumber. Gambar (e) menunjukkan sebuah simbol alternatif untuk JFET saluran n. Simbol dengan gerbang offset ini dipilih oleh banyak ahli mesin dan ahli teknik. Gerbang offset menegaskan ujung sumber dari peranti ini, sebuah keuntungan terbatas pada rangkaian multitingkat yang canggih. Adapila JFET kanal-p. Simbol skematik untuk JFET kanal-p adalah sama dengan kanal-n , kecuali bahwa titik panah gerbang tersebut mempunyai arah yang berlawanan. Aksi JFET kanal-p adalah melengkapi; yaitu semua tegangan dan arus berlawanan. DRAIN DRAIN GATE GATE SOURCE SOURCE (d) (e) Gambar (d) Simbol Skematik; (e) Simbol Gerbang Offset KURVA DRAIN Gambar (f) menunjukkan sebuah JFET dengan tegangan bias normal. Dalam rangkaian ini, tegangan gate-source VGS sama dengan tegangan catu gate VGG, dan tegangan drain-source VDS sama dengan tegangan catu drain VDD. Arus Drain Maksimum Jika kita menghubungsingkatkan gate ke sumber, seperti pada gambar (g) , kita akan memperoleh arus drain maksimum karena VGS =0. Gambar (h) menunjukkan grafik arus drain ID terhadap sumber tegangan Drain VDS untuk kondisi gate terhubung singkat.

- 4. + + VPP VPP - - (f) (g) ID GATE SINGKAT IDSS DAERAH AKTIF VDS VP VDS(MAX) (h) Gambar (f) Bias Normal; (g)tegangan gate nol; (h)arus gate drain dihubung singkat Arus drain secara cepat dan kemudian hampir menjadi horizontal ketika VDS lebih besar daripada VP. Ketika VDS naik, lapisan depletion akan mengembang. Ketika VDS= VP , lapisan depletion hampir menyentuhnya. Kanal penghubung yang sempit akan menmutuskan atau mencegah kenaikan arus. Inilah sebabnya mengapa arus memiliki batas atas IDSS. Daerah aktif sebuah JFET adalah antara VP dan VDS(MAX) . Tegangan minimum VP disebut tegangan pinchoff , dan tegangan maksimum VDs(max) .Tegangan minimum VP disebut breakdown antara pinchoff dan breakdown, JFET bertindak seperti sebuah sumber arus yang besarnya mendekat VDSS ketika VGS =0. Daerah Ohmic Tegangan pinchoff memisahkan dua daerah operasi utama JFET. Daerah yang hampir Horizontal adalah daerah aktif. Bagian yang hampir vertikal pada kurva drain dibawah pinchoff dinamakan dengan daerah ohmic.

- 5. Ketika beroperasi pada daerah ohmic, sebuah JFET akan ekuivalen dengan sebuah resistor dengan sebuah nilai yang mendekati: RDS disebut dengan hambatan ohmic JFET. Tegangan Cutoof Gate Semakin negatif tegangan gate-sumber, maka semakin kecil arus drain. Sebuah VGS akan mengurangi arus drain sampai mendekati 0. Tegangan ini dinamakan dengan cutoff gate- source dan dilambangkan dengan VGS(off) . Pada tegangan cutoff lapisan deplation akan tercapai. Sebagai akibatnya, kanal penghubung akan hilang . Inilah sebabnya mengapa arus drain mendekati nol. Hal ini bukanlah kebetulan. Kedua tegangan akan memiliki besar yang sama karena kedua nilai tersebut adalah nilai ketika lapisan depletion tercapai atau hampir tercapai. Dalam bentuk rumus: VGS= -VP

- 6. KURVA TRANSKONDUKTANSI Kurva transkonduktansi sebuah JFET adalah sebuah grafik ID terhadap VGS , Dengan membaca nilai ID dan VGS dari tiap kerva drain.Kurva tidak linear karena arus meningkat lebih cepat saat VGS mencapai 0. Beberapa JFET memiliki kurva transkonduktansi. Titik akhir kurva adalah VGS(off) dan IDSS. Persamaan untuk grafik ini adalah : Karena danya kuadrat pada persamaan tersebut, maka JFET sering dinamakan peranti hukum-kuadrat. Pengkuadratan tersebut menghasilkan kurva nonlinear. Kurva transkonduktansi yang ternormalisasi artinya bahwa kita menggambar rasio seperti ID / IDDS dan VGS/ VGS(off). Rumus titik setengah cutoff: Menhasilkan arus ternormalisasi sebesar: Dengan kata-kata: Ketika tegangan gate adalah setengah dari tegangan cutoff, maka arus drain adalah seperempat dari nilai maksimum.

- 7. PEMBIASAN DALAM DAERAH OHMIC JFET dapat dibiaskan pada daerah ohmic ataupun pada daerah ohmic, JFET akan ekuivalen dengan hambatan. Ketika dibiaskan pada daerah aktif, JFET ekuivalen dengan sebuah sumber arus . Bias Gate Gambar (i) menujukkan bias gate Negatif-VGG diberikan ke gate melaui resistor pembias RG . Tegangan gate mengatur arus drain sehingga lebih kecil daripda IDDS . Ketika arus drain melalui RD, akan mengatur tegangan drain sebesar: VD= VDD-IDRD Bias gate adalah cara terburuk untuk membiaskan JFET pada daerah aktif sebab titik Q menjadi sangat tidak stabil. Sebagai contoh, sebuah 2N5459 mempunyai kisaran maksimum dan minimum sebagai berikut: IDDS bervariasi dari 4-16 mA, dan VGSoff bervariasi dari -2 ssmpai -8 Volt. Hard Saturation Meskipun tidak sesuai untuk pembiasan pada daerah aktif, bias gate sangat bagus untuk pembiasan pada daerah ohmic karena kestabilan titik Q tidak menjadi masalah. Ujung atas pada garis beban dc memiliki arus jenuh drain sebesar: Untuk memastikan bahwa JFET dibias pada daerah ohmic, semua yang kita perlukan adalah menggunakan VGS=o dan: ID(sat)<<IDDS Simbol <<berarti “jauh lebih kecil daripada”. Persamaan ini menyatakan bahwa arus jenuh drain harus jauh lebih kecil daripada arus drain maksimum. Sebagai contoh, jika sebuah JFET memiliki IDDS= 10 mA, maka Hard Saturation akan muncul jika VGS=0 dan ID(sat)=1mA. Ketika sebuah JFET dibiaskan pada daerah ohmic , kita dapat menggantinya dengan sebuah hambatan RDS. Dengan rangkaian yang sudah ekuivalen maka kita dapat menghitung tegangan drain . Ketika RDS jauh lebih kecil daripada RD, tegangan drain akan mendekati 0.