The document discusses VLSI education and development in India, including:

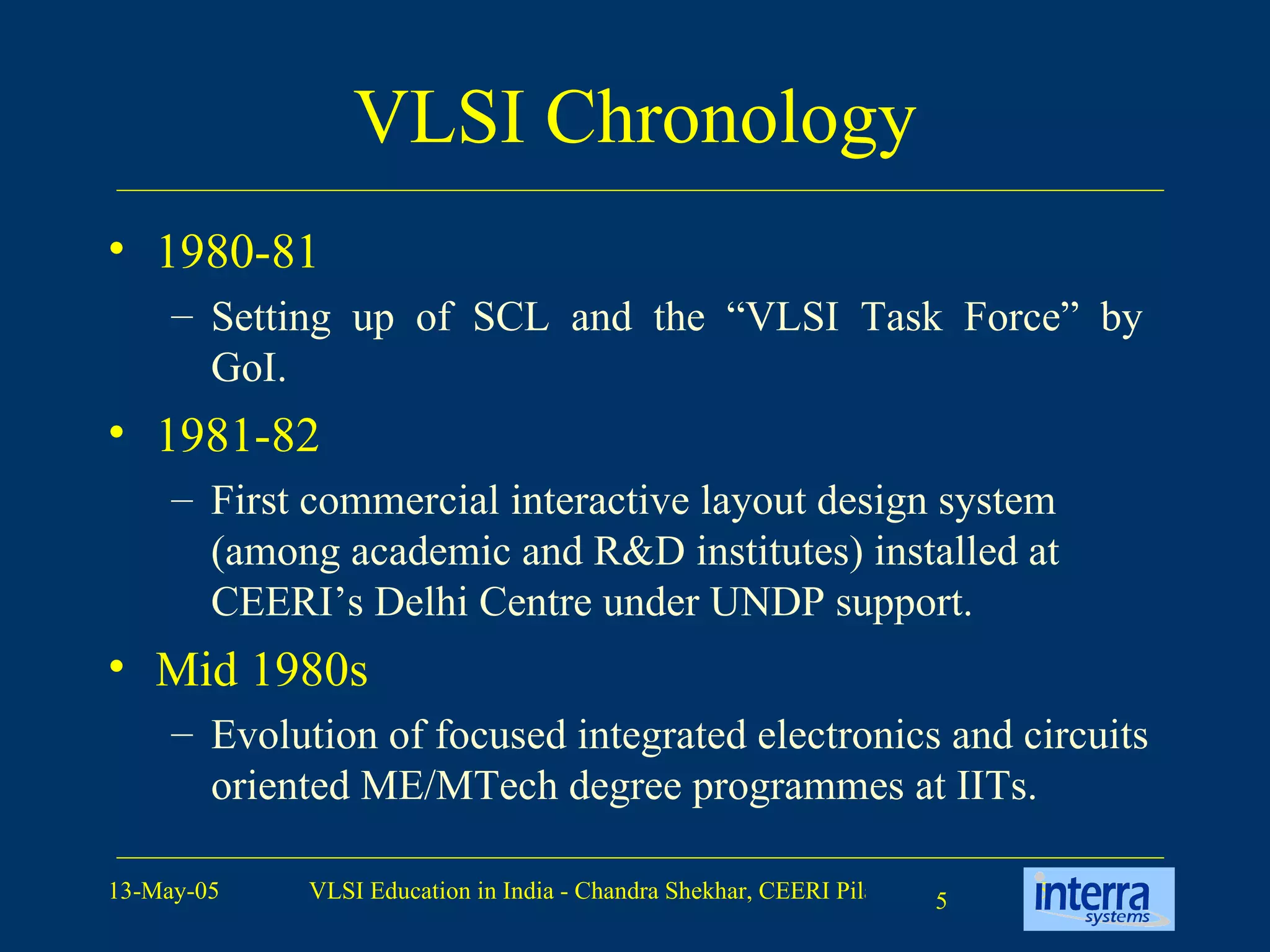

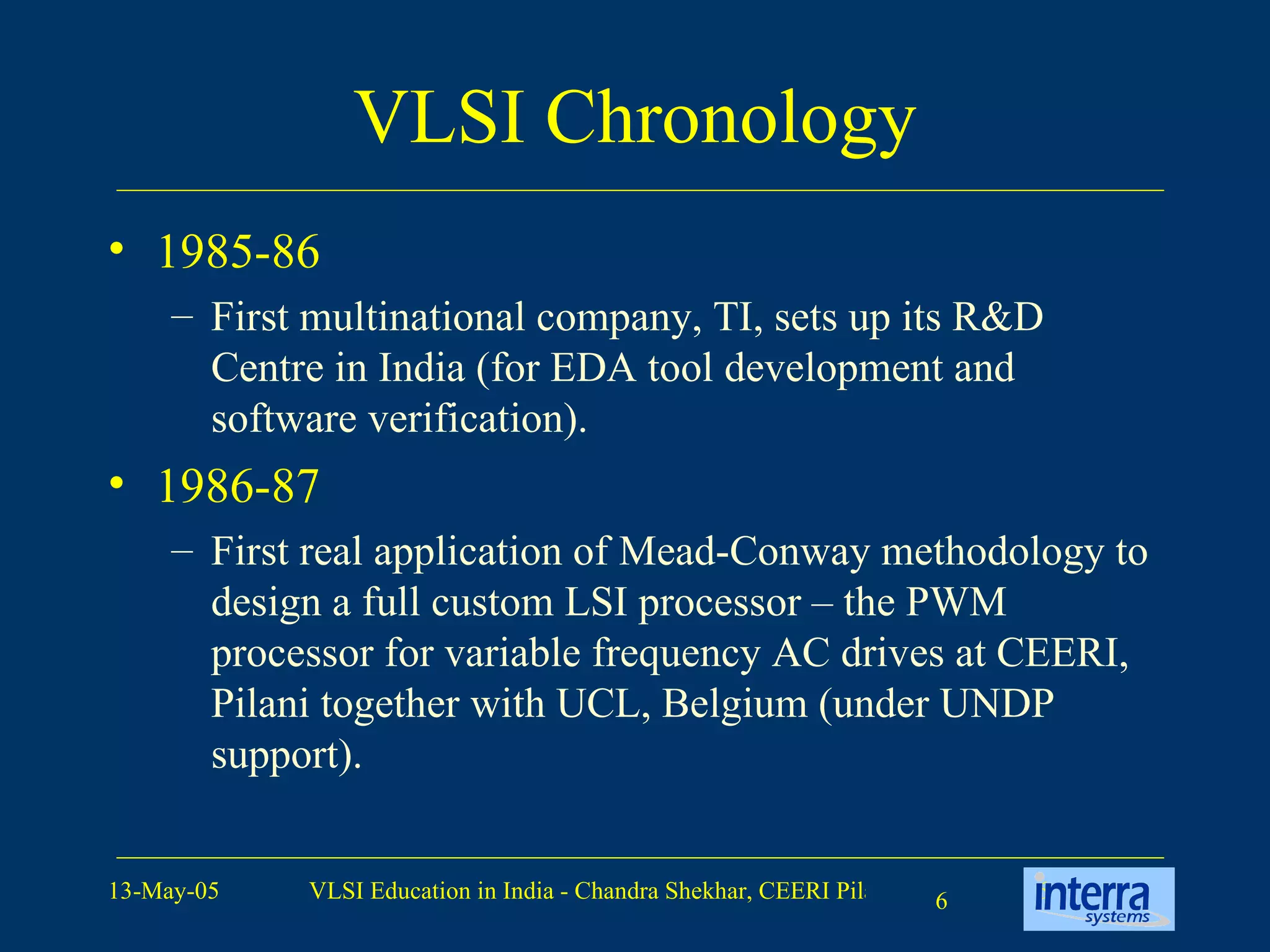

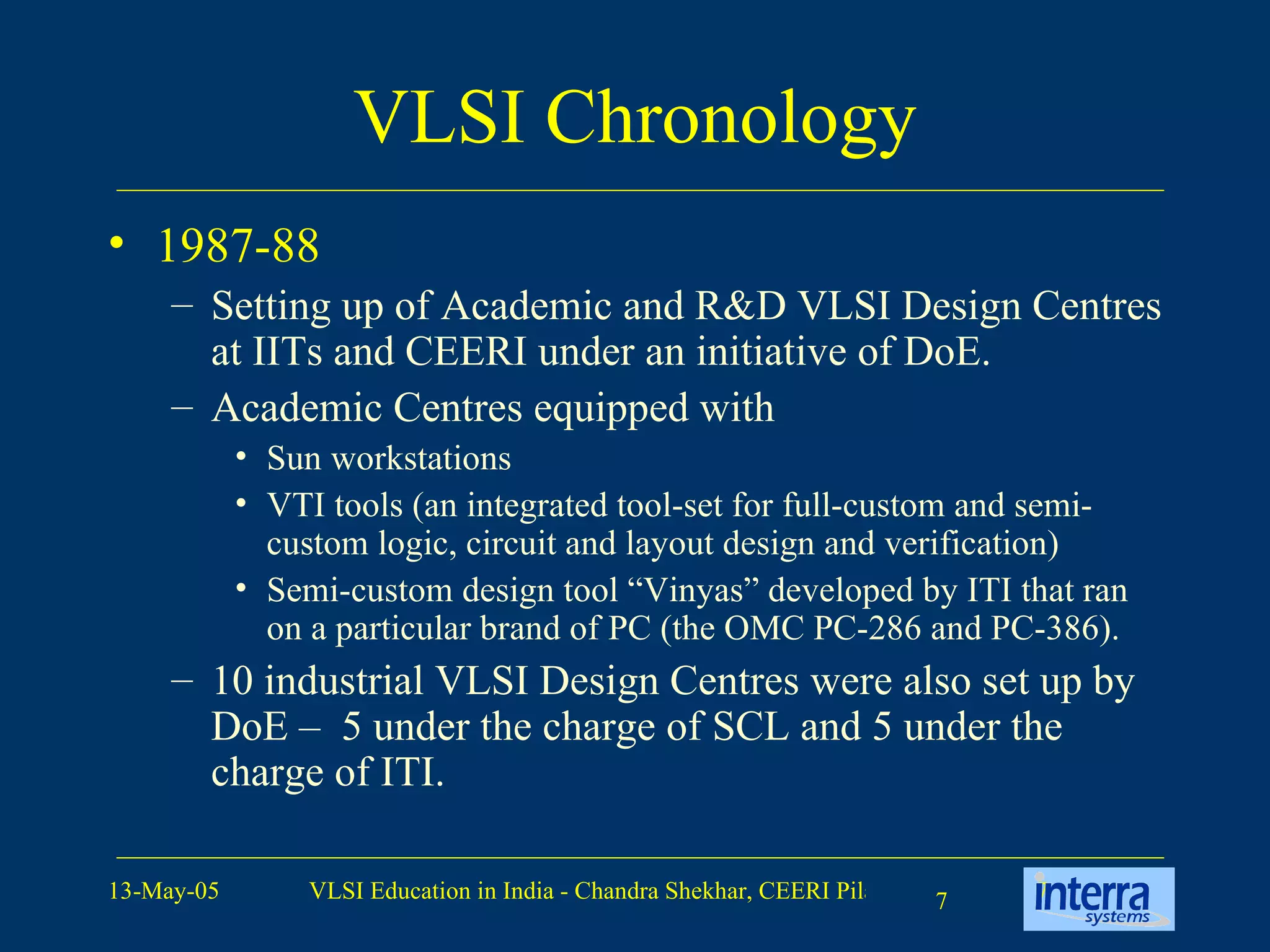

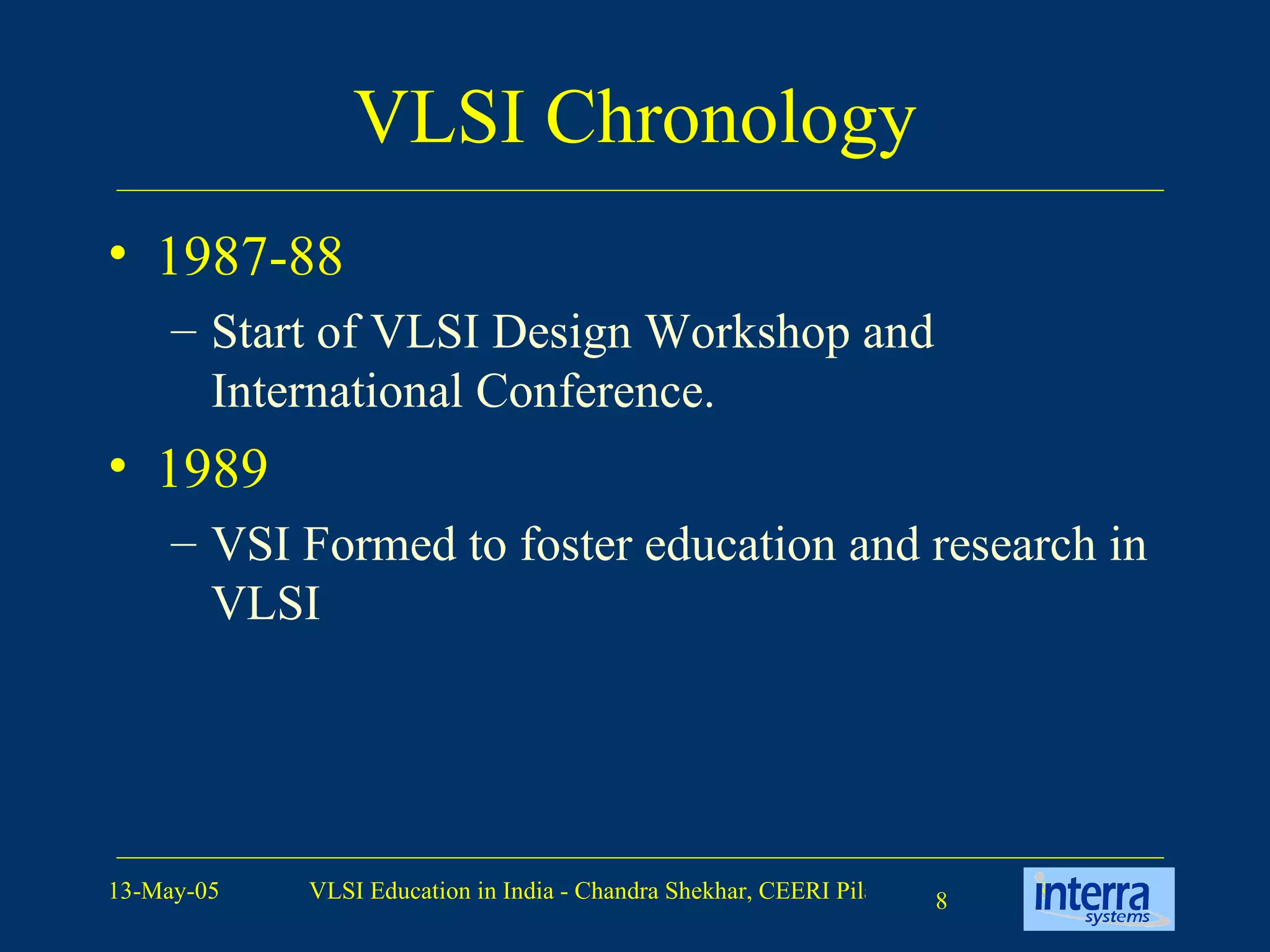

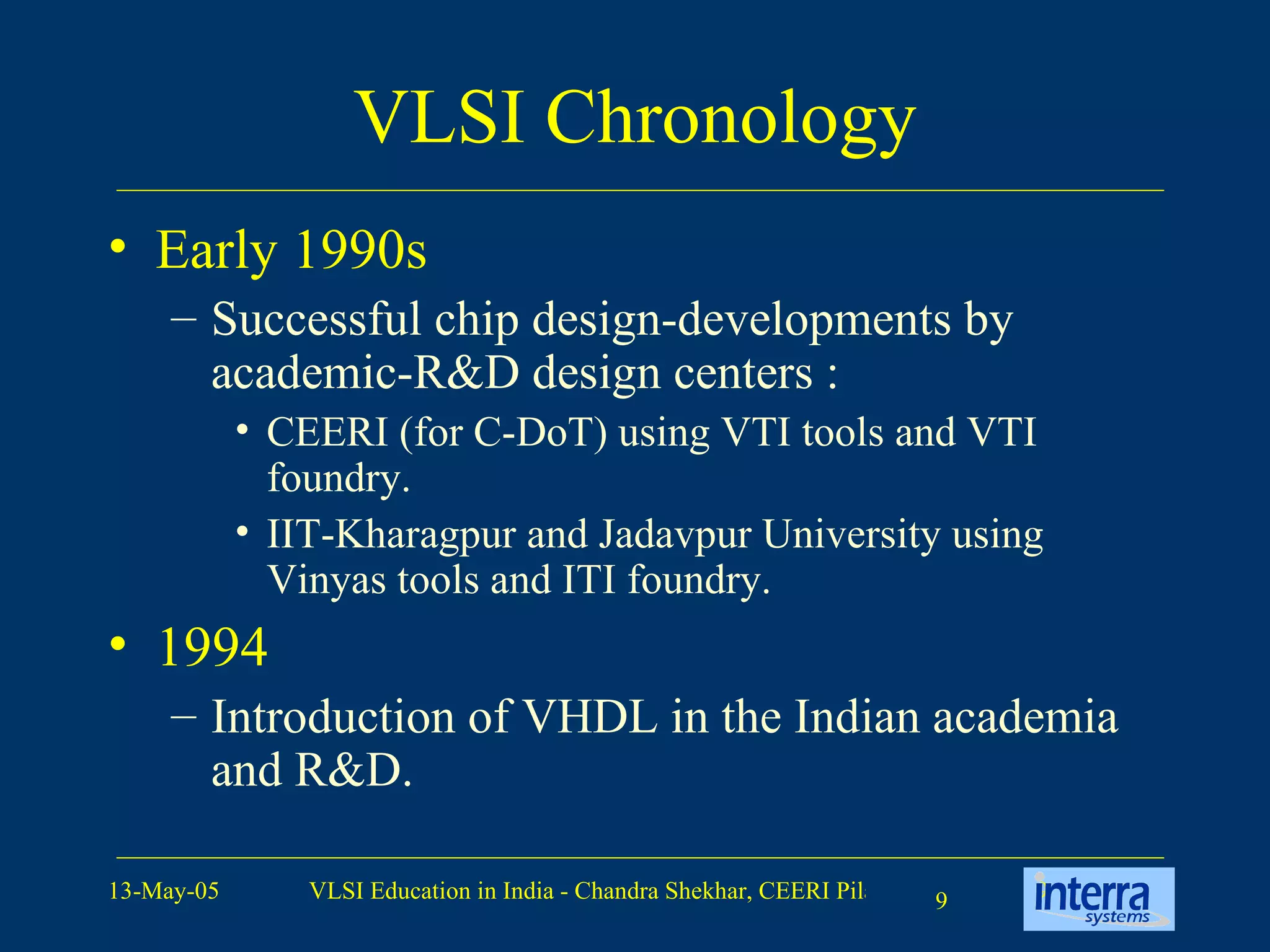

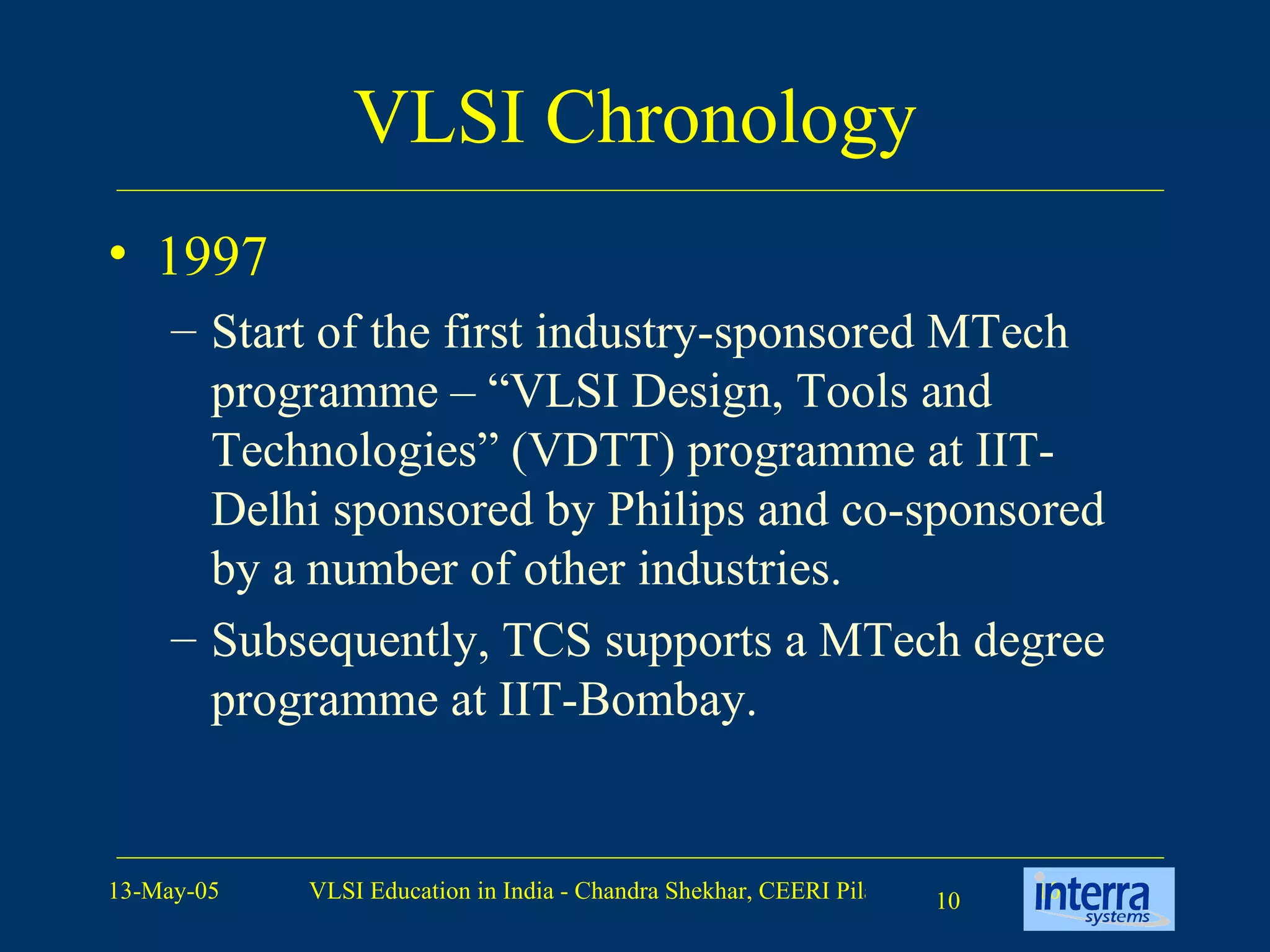

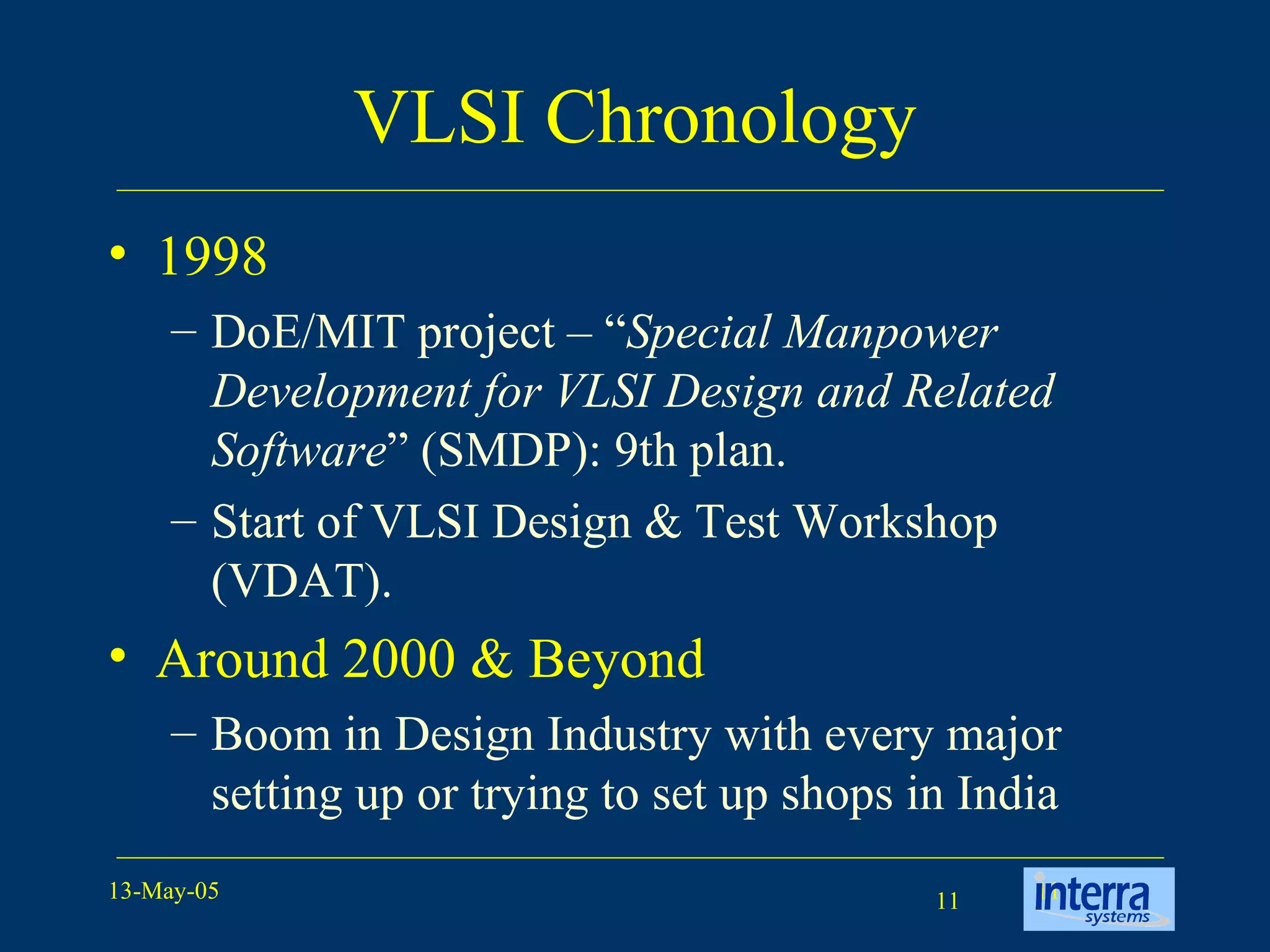

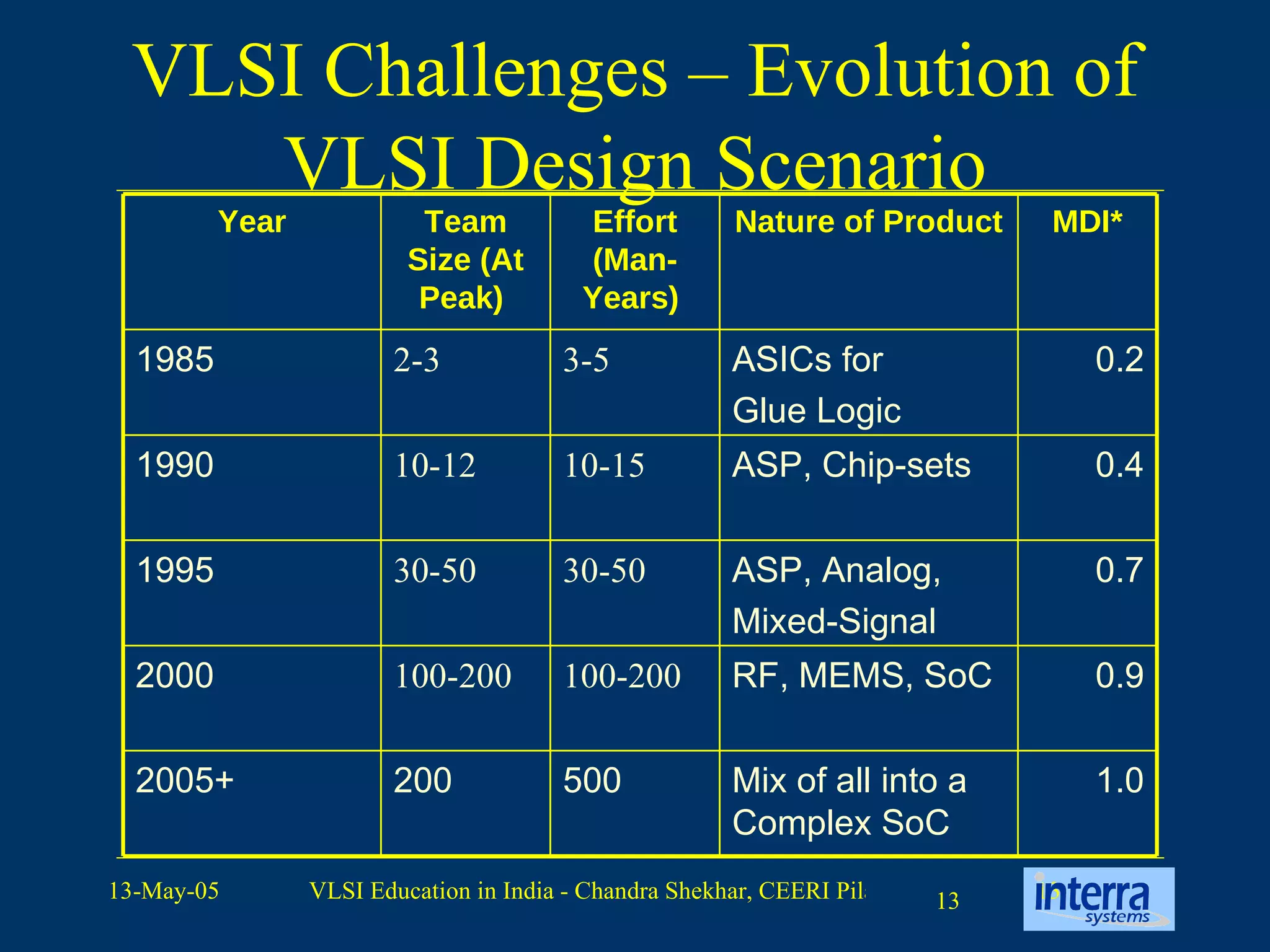

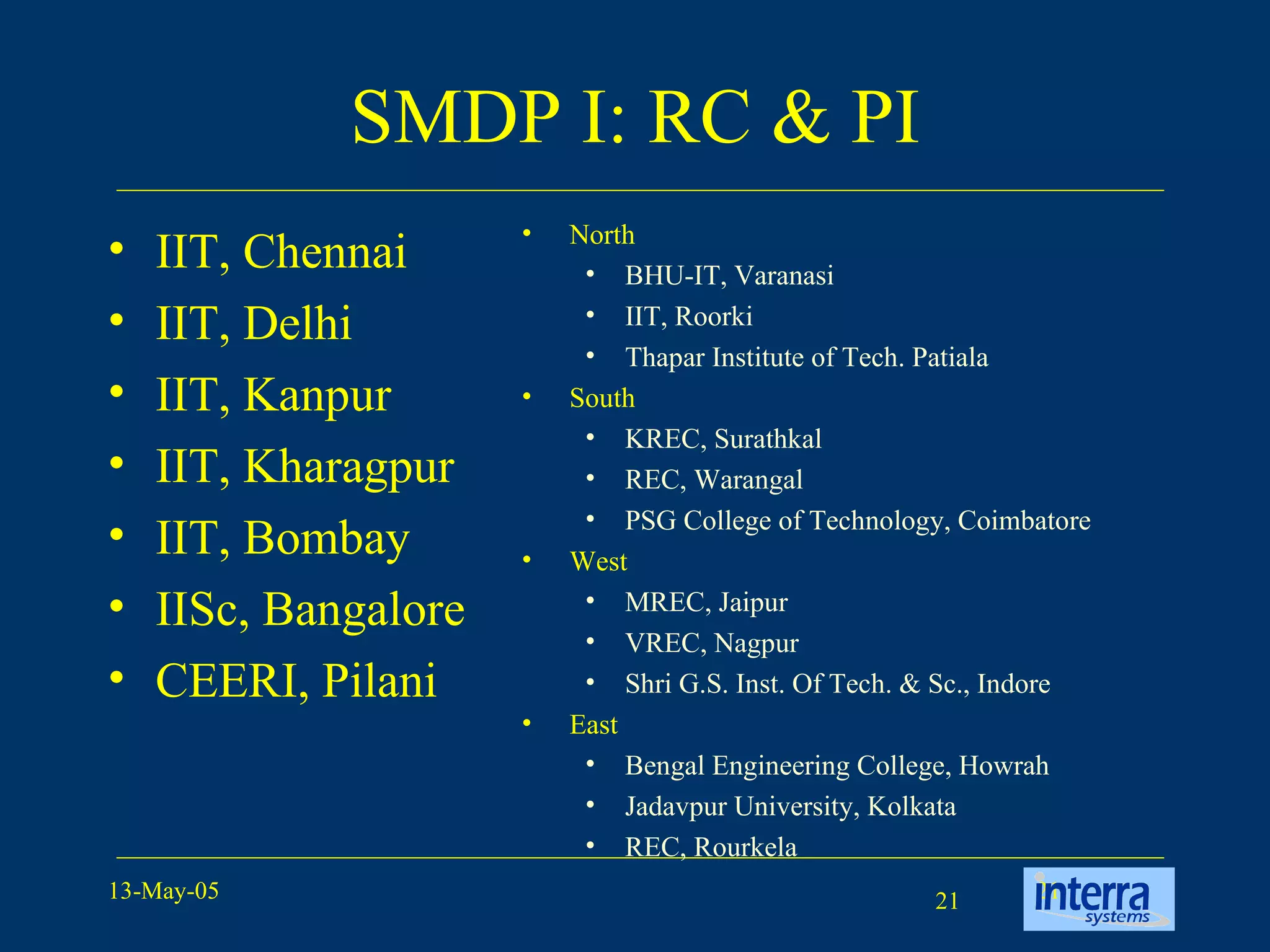

1. A chronology of VLSI education from 1979-2005, including government initiatives like SMDP to boost VLSI design manpower and establish academic centers.

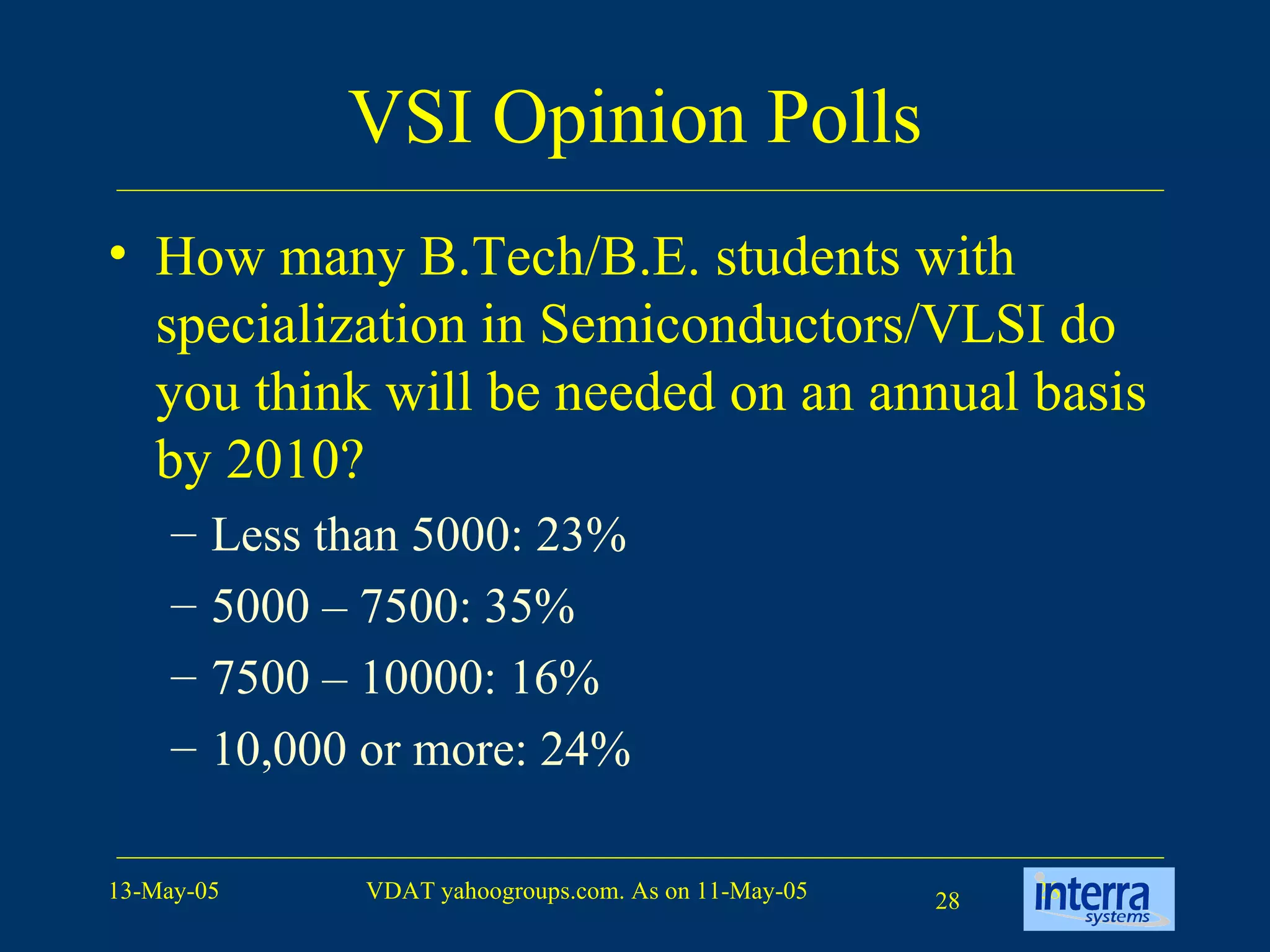

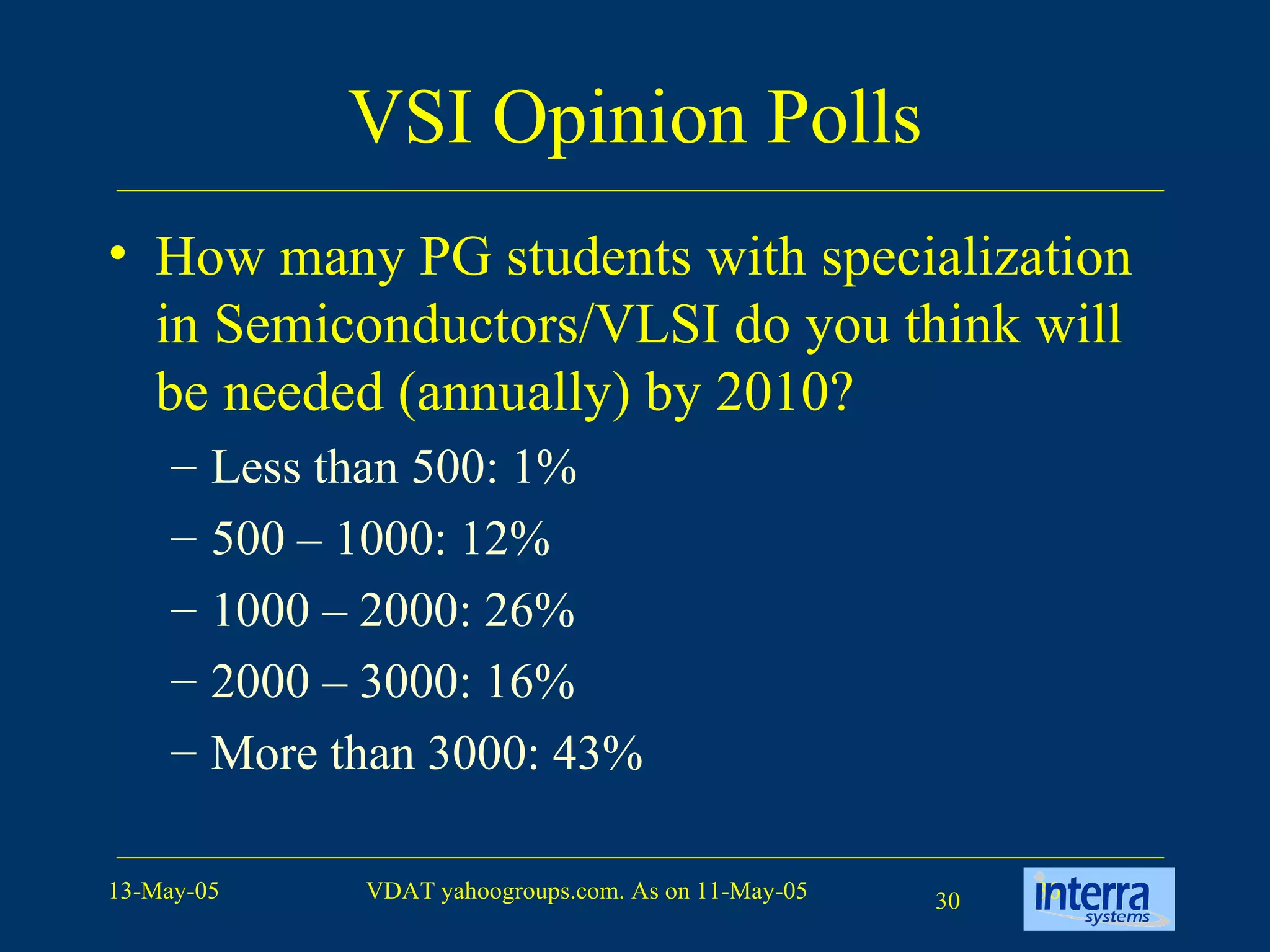

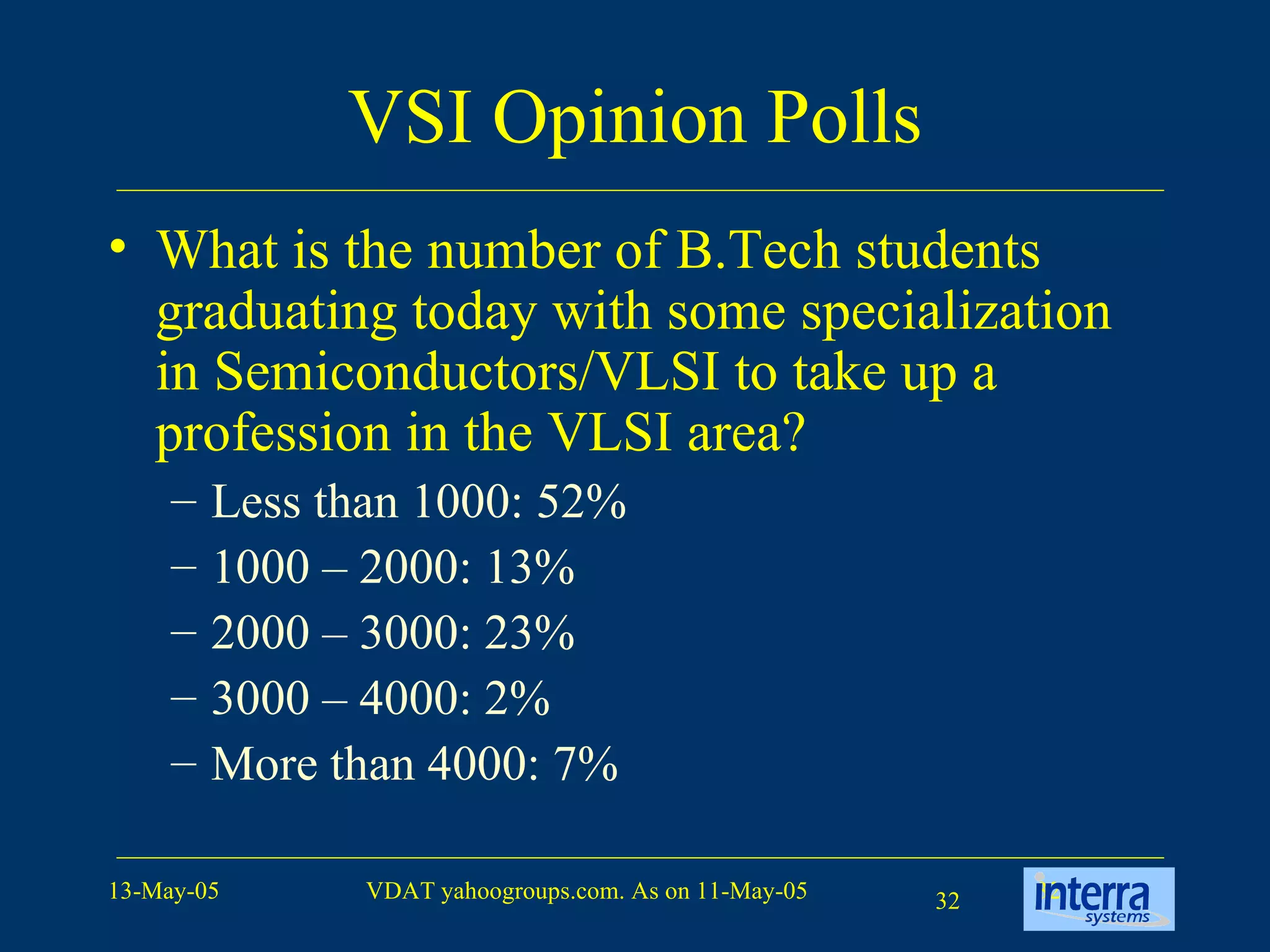

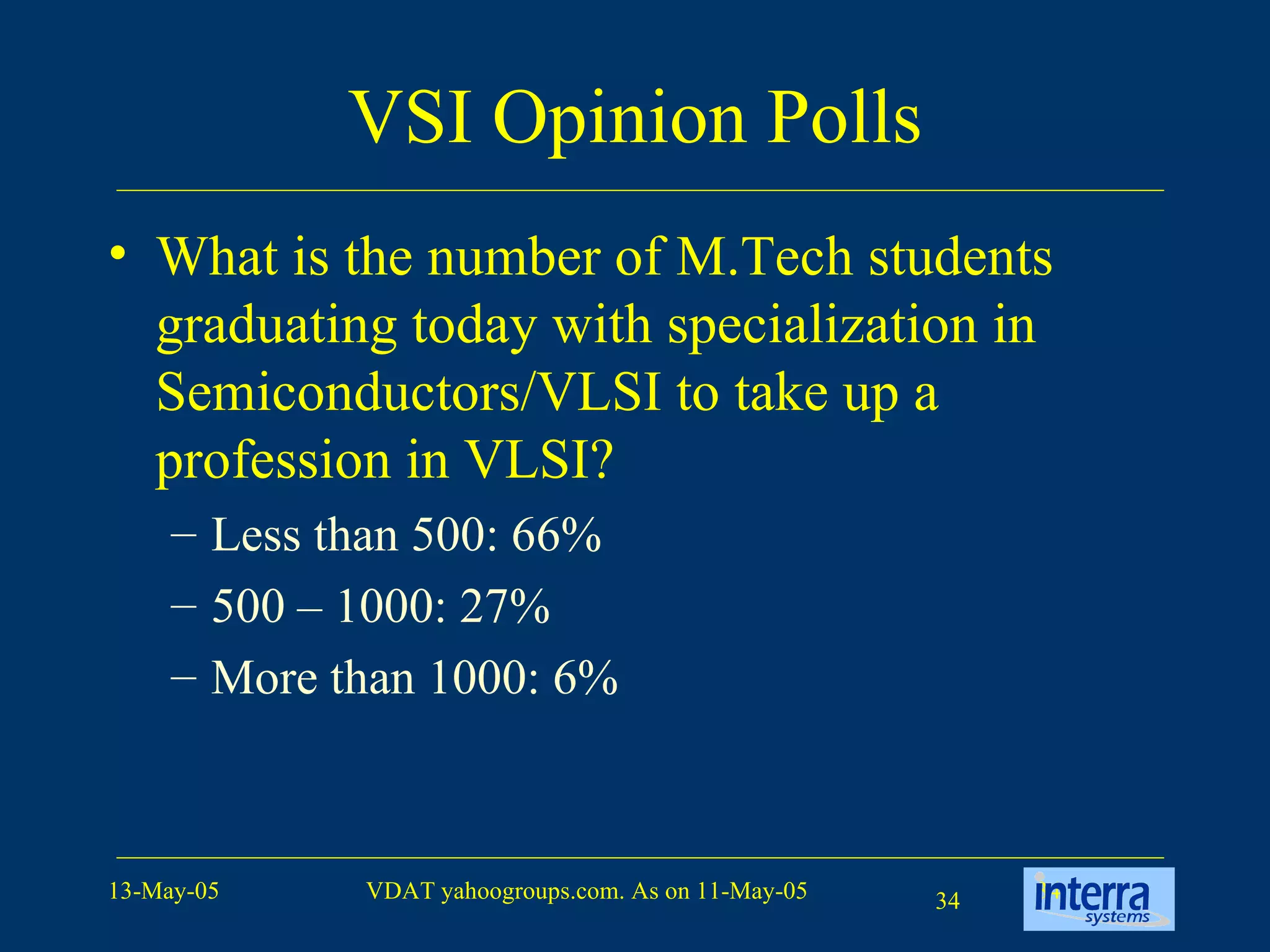

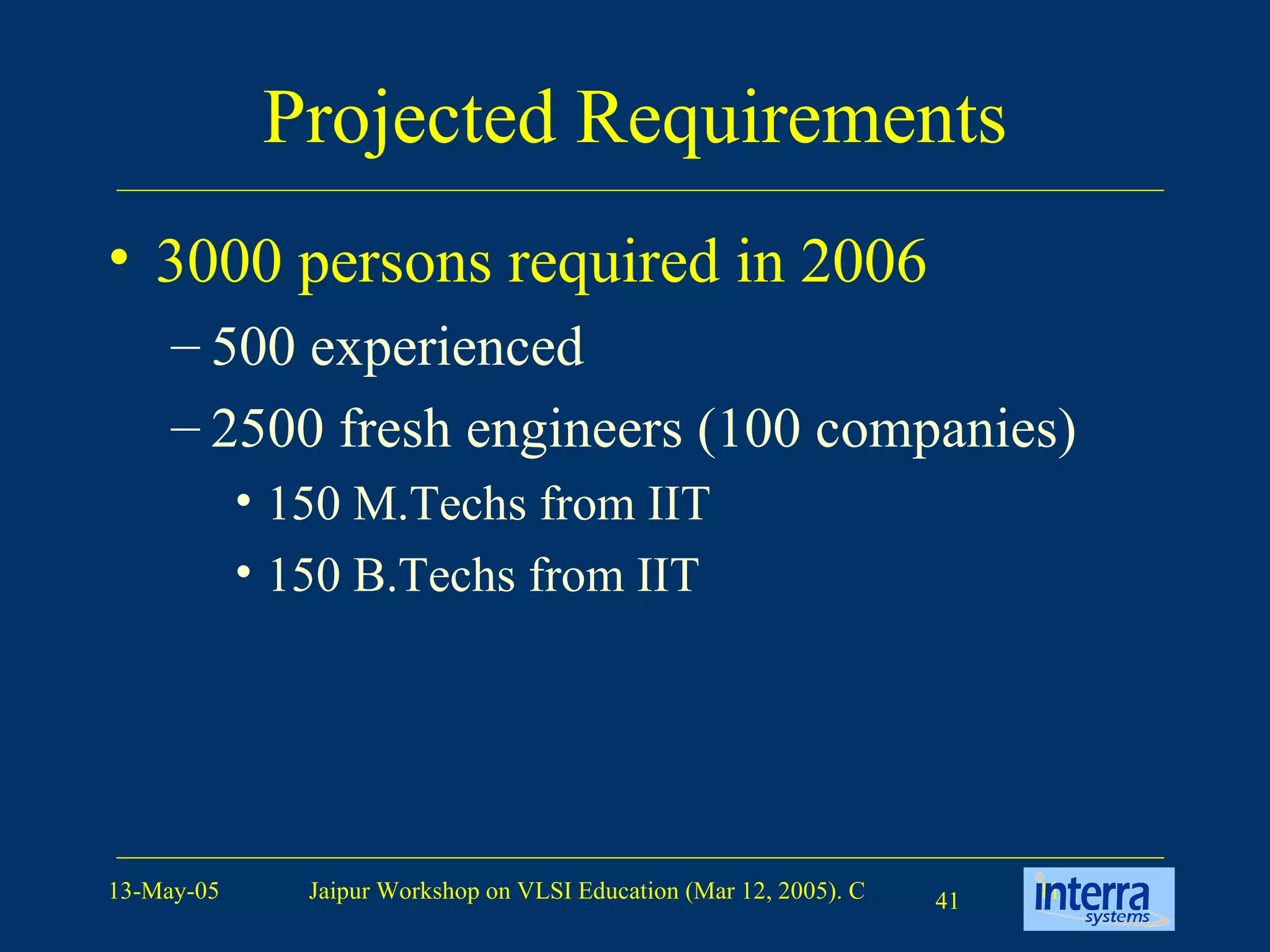

2. Surveys by VSI that found a growing gap between projected VLSI manpower needs and current outputs from Indian universities.

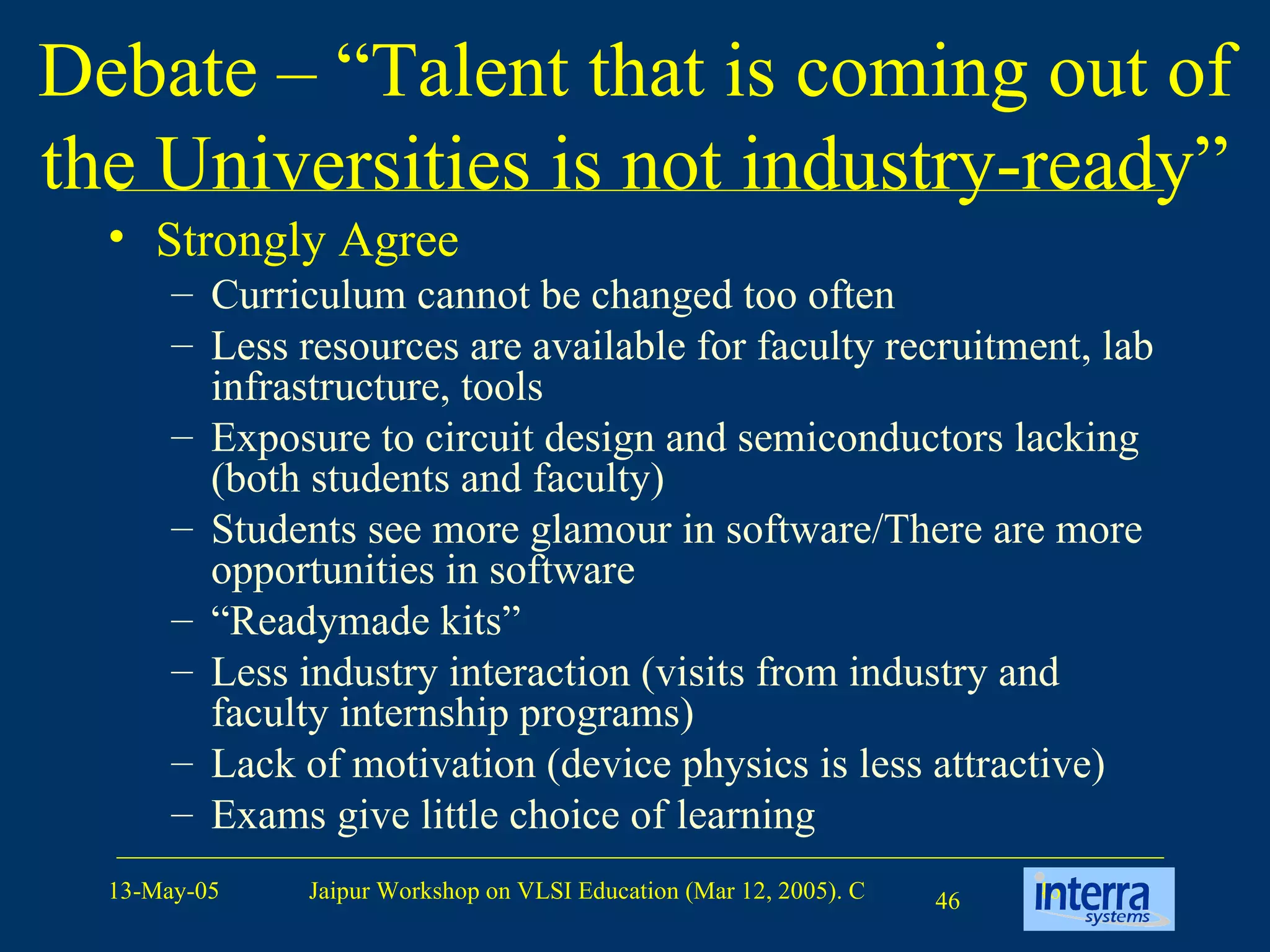

3. A workshop discussing goals of university-industry collaboration and feedback that graduating students lack industry readiness in areas like design skills and experience with industrial tools.