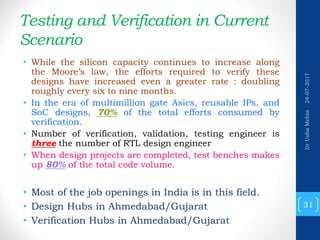

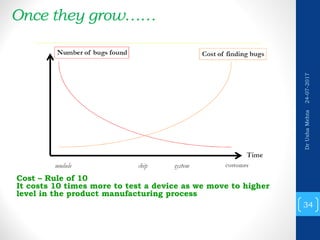

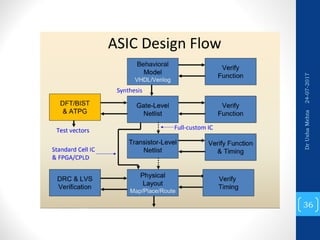

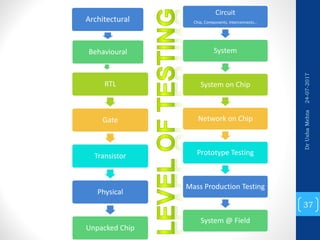

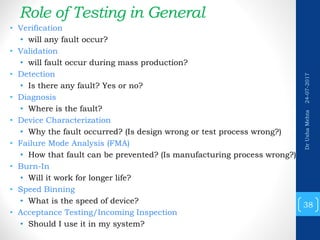

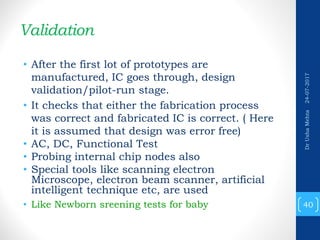

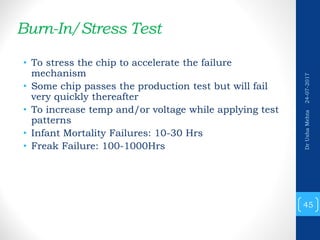

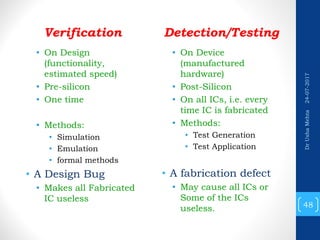

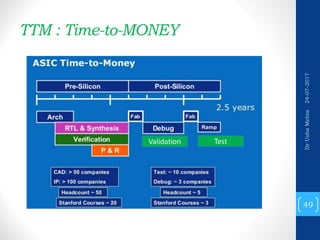

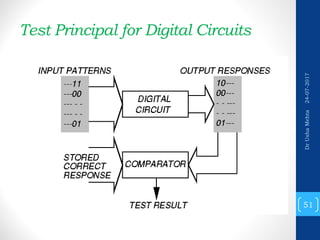

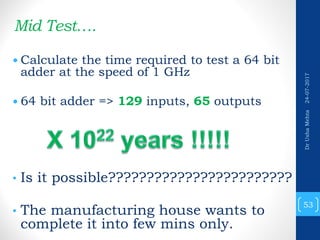

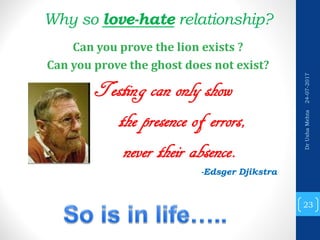

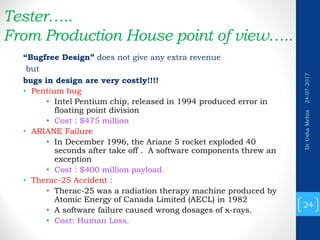

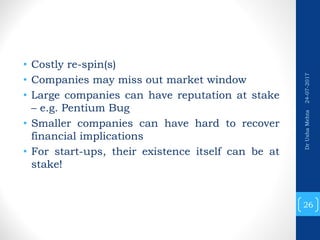

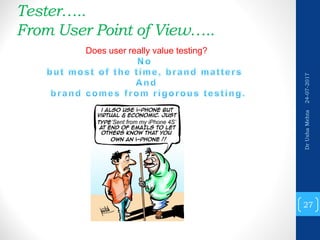

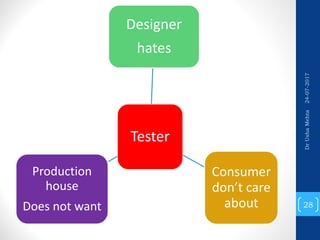

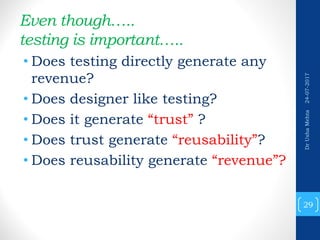

This document discusses testing and verification of electronic circuits. It begins by acknowledging sources used to create the presentation. It then discusses how testing has become increasingly important as designs grow more complex, with verification now consuming 70% of effort. Testing ensures functionality and finds defects, helping prevent costly issues later. The relationship between testers and other roles is sometimes tense as testing finds problems but does not generate revenue. However, thorough testing helps gain user trust and reuse, reducing costs from redesigns. It outlines the various stages of testing from verification to diagnose issues and improve processes. The goal is thorough testing to detect defects before systems reach users.

![Why testing is of too much

importance in today’s

semiconductor world…..

30

DrUshaMehta24-07-2017

[Courtesy: ITRS]](https://image.slidesharecdn.com/2017tvec1introduction-180131082824/85/Testing-and-Verification-of-Electronics-Circuits-Introduction-30-320.jpg)