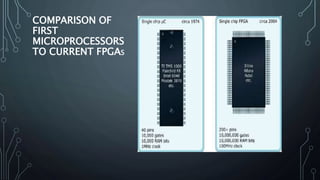

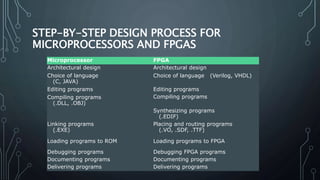

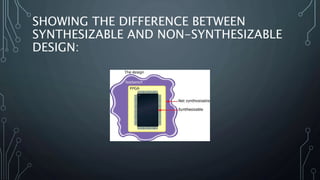

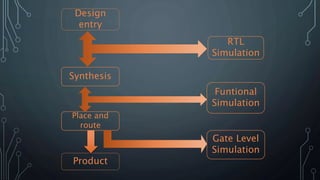

The document discusses programming FPGAs compared to microprocessors. It describes the FPGA design process including simulation with test benches, synthesis to convert code to a netlist, placement and routing of components, and in-system programming to update the FPGA design. The key differences between FPGAs and microprocessors are that FPGAs do not have fixed logic and their design is compiled to a configurable logic array rather than an executable program. Debugging FPGAs relies more on simulation of interactions with the external environment using test benches.