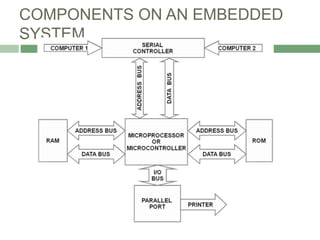

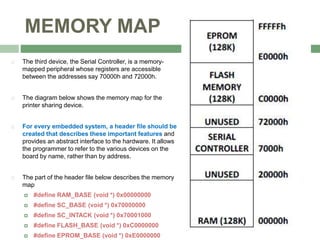

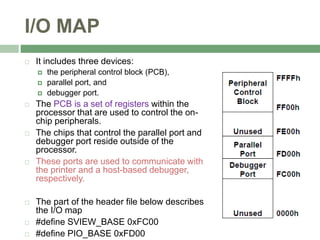

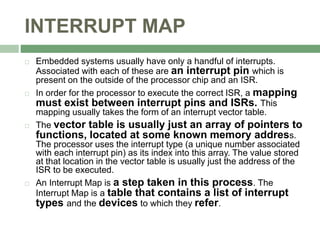

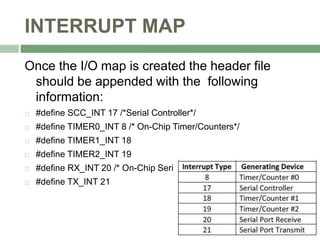

The document discusses the key components of an embedded system, including the memory map, I/O map, and interrupt map. The memory map shows the memory addresses for devices like RAM, ROM, and peripherals. The I/O map similarly lists addresses for devices that use a separate I/O space. The interrupt map defines interrupt numbers for devices that can trigger interrupts, like a serial controller. Together these maps provide an interface for the programmer to access hardware on the embedded board.