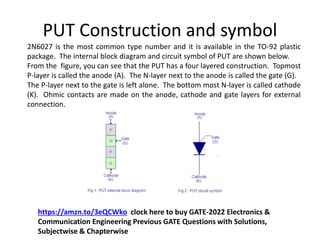

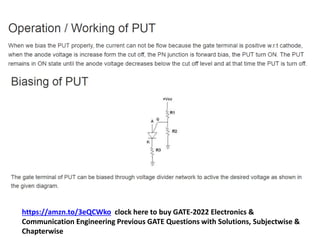

The Programmable Unijunction Transistor (PUT) is a semiconductor device similar to thyristors with programmable characteristics, allowing for variable parameters like intrinsic standoff ratio and peak voltage through external resistors. Its construction features a four-layer structure with terminals for the anode, cathode, and gate, and its operation is characterized by a negative resistance region used in applications such as relaxation oscillators and pulse circuits. The PUT's characteristics, including the relationship between anode voltage and current, are crucial for its functionality in electronic circuits.