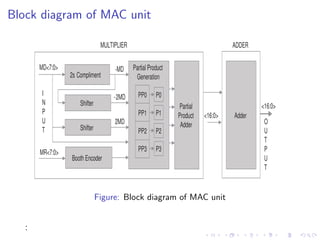

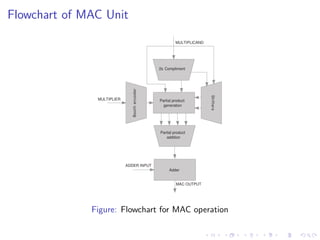

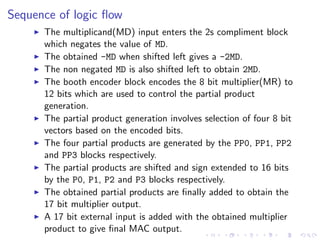

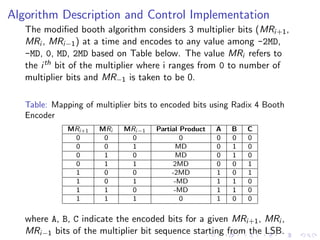

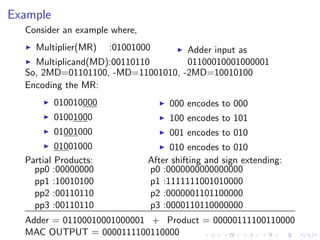

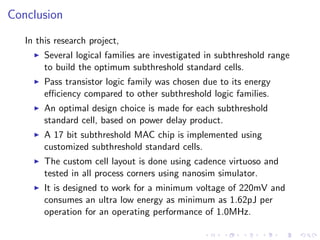

This document discusses the design of an energy efficient sub-threshold multiplication and accumulation (MAC) unit for low power digital signal processing applications. It describes the following:

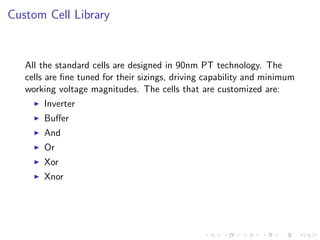

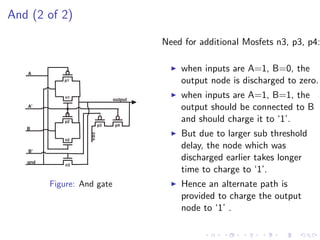

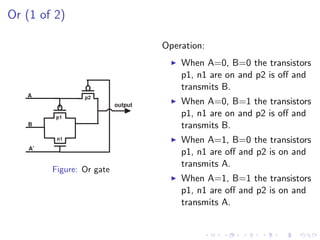

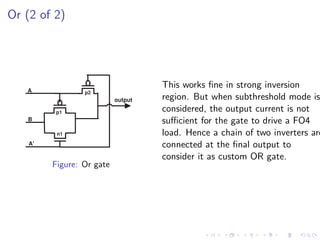

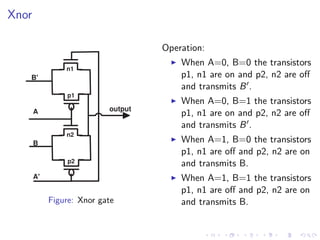

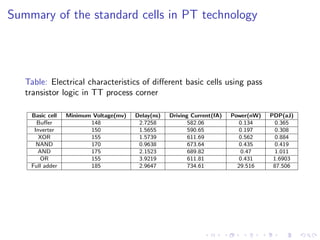

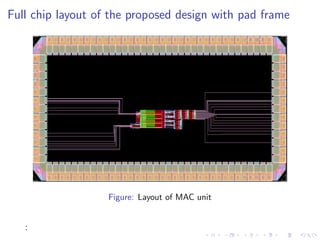

1. The technologies used including 90nm pass transistor technology and Cadence and Synopsys design tools.

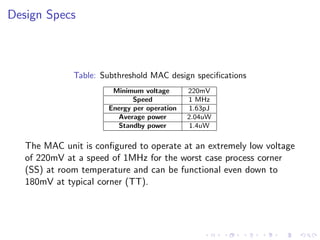

2. The objectives of the project which are to design an energy efficient circuit in 90nm technology emphasizing sub-threshold operation and gaining expertise in design tools.

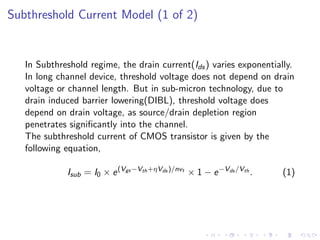

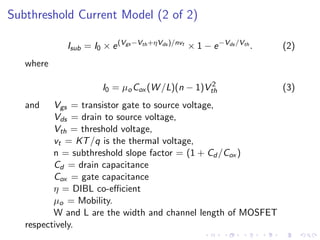

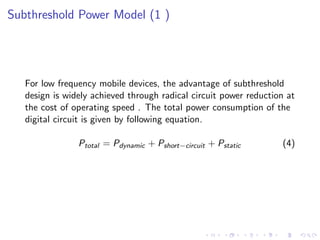

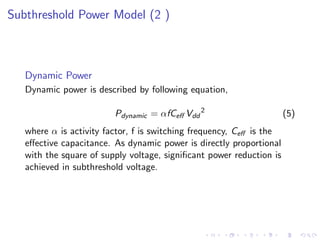

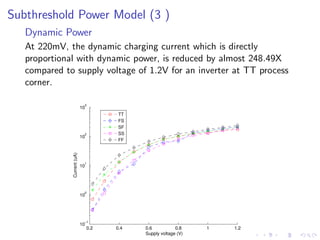

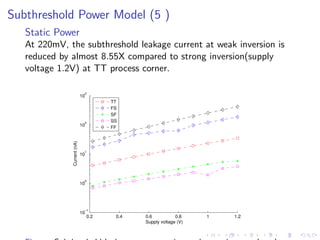

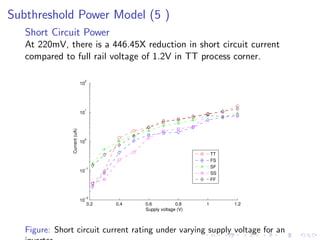

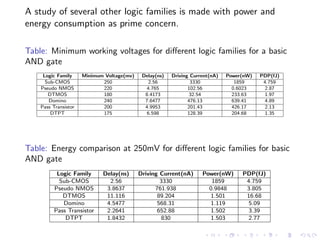

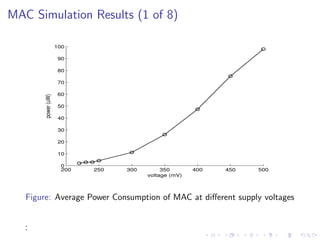

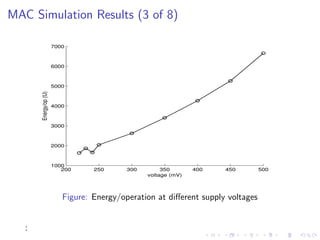

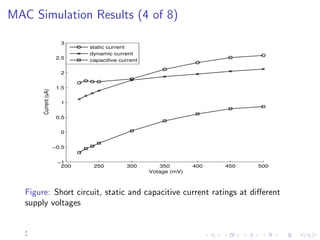

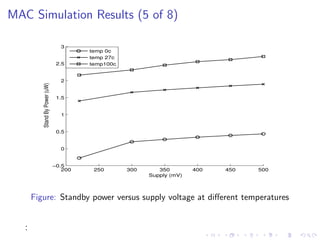

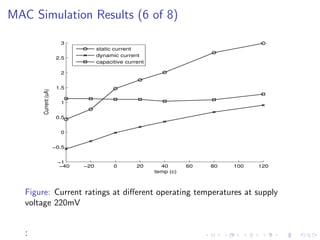

3. An overview of sub-threshold operation of MOS transistors and models for sub-threshold current and power consumption showing significant reductions in dynamic, static, and short circuit power at sub-threshold voltages.

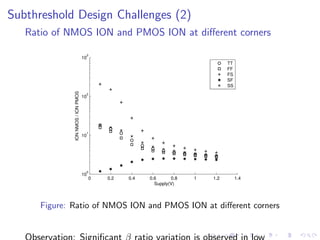

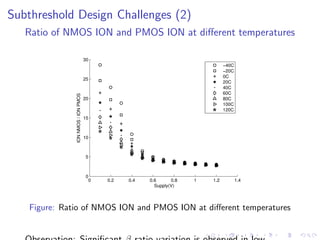

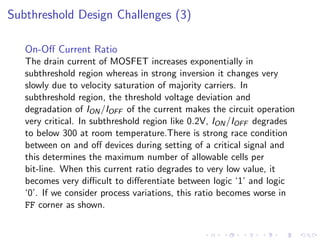

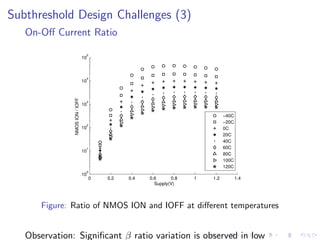

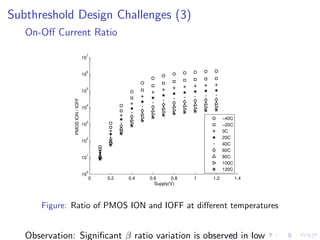

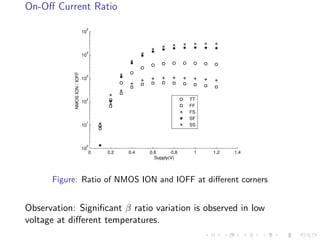

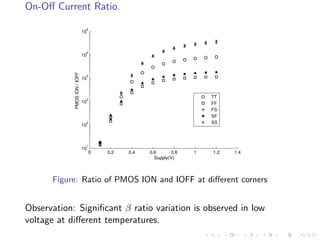

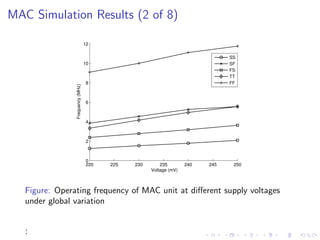

4. Challenges of sub-threshold design including