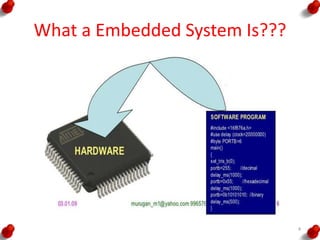

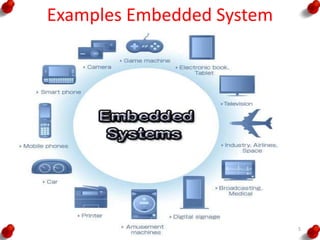

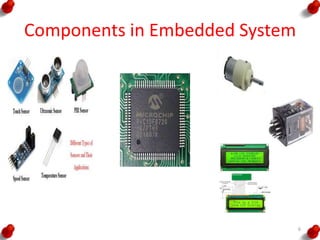

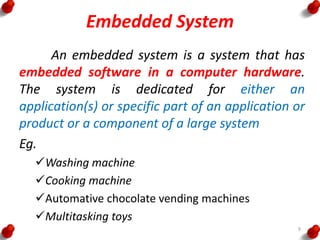

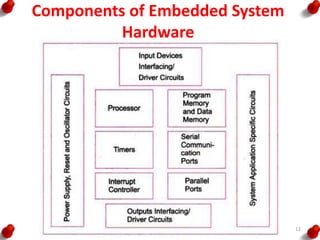

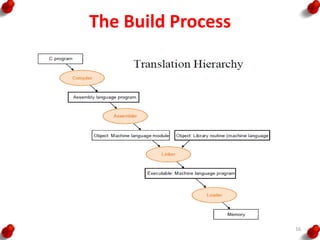

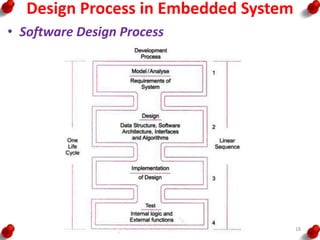

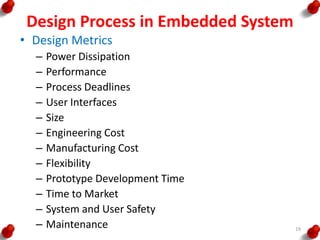

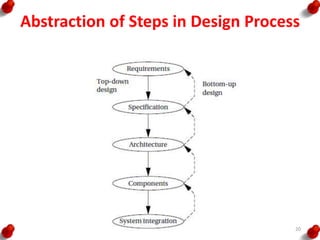

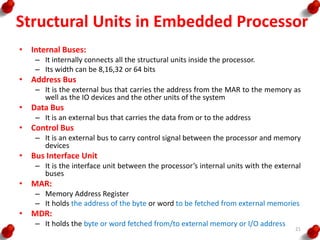

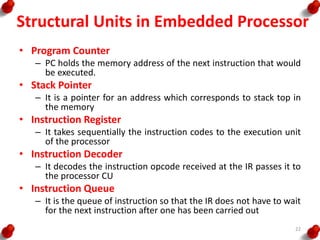

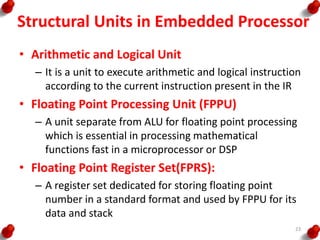

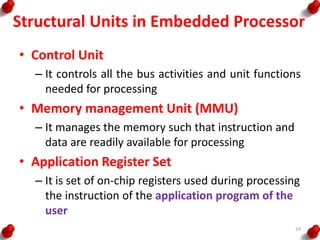

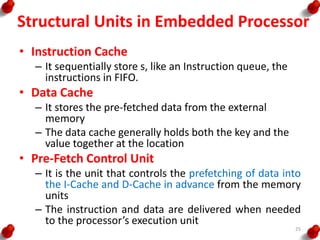

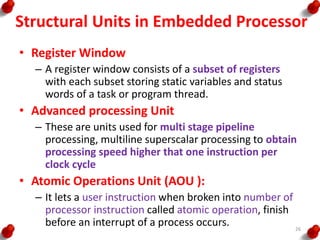

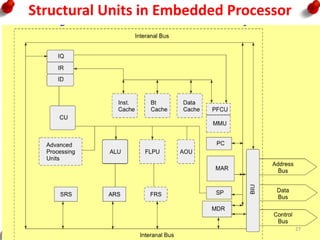

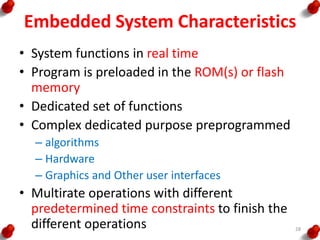

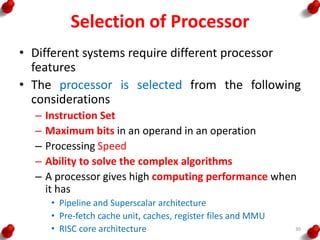

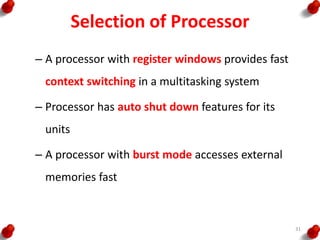

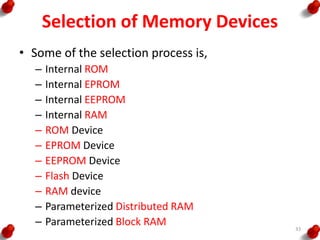

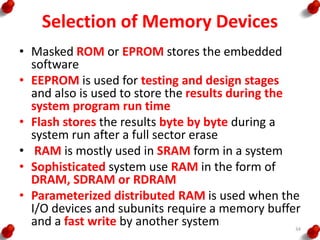

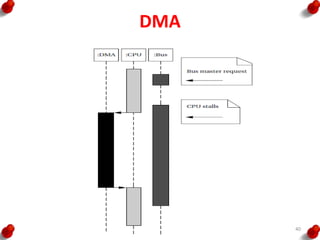

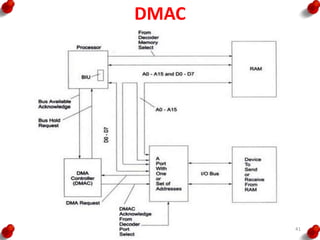

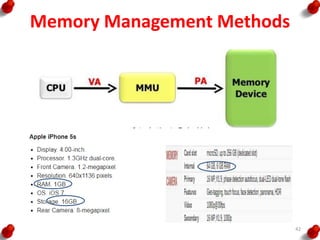

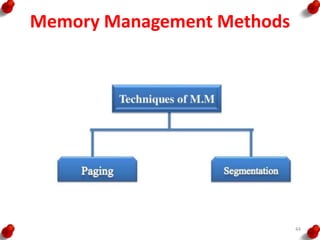

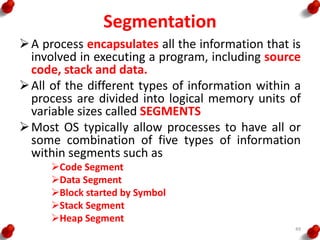

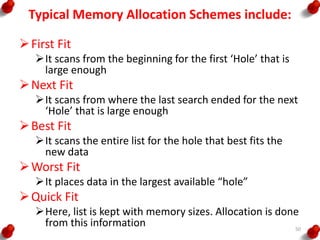

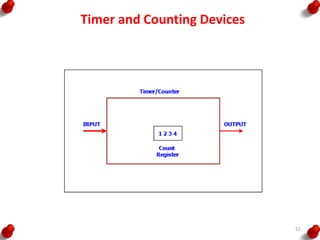

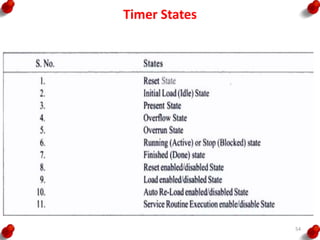

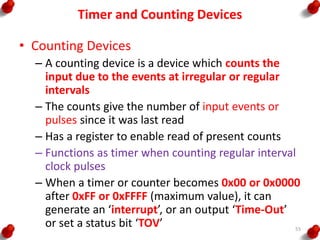

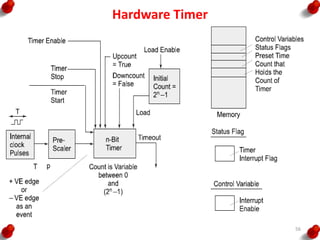

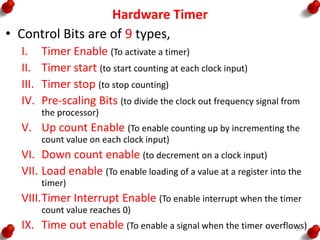

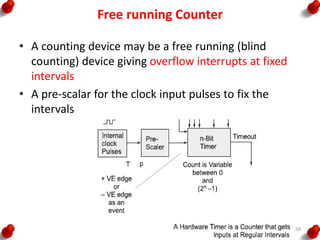

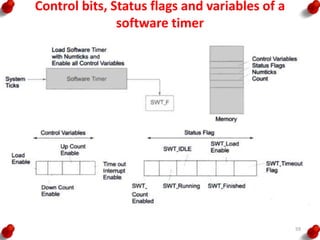

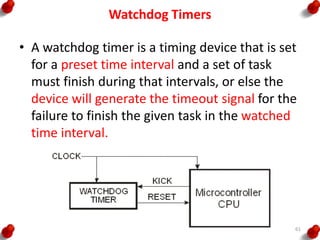

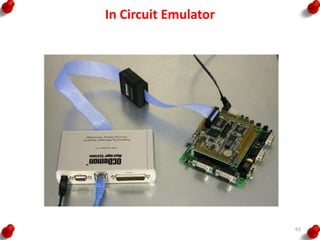

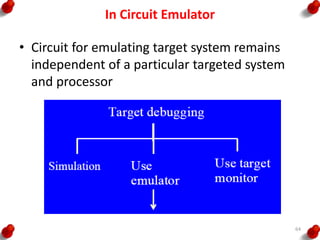

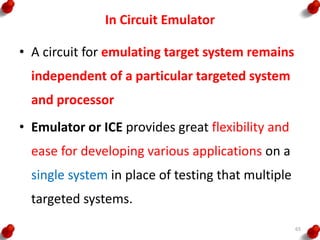

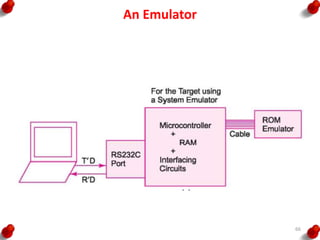

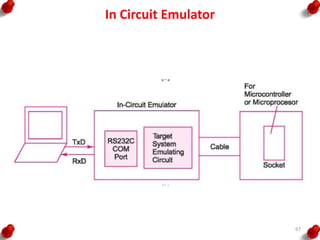

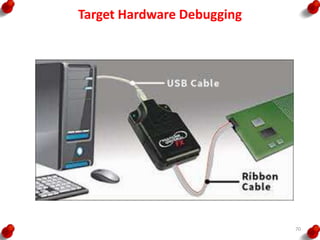

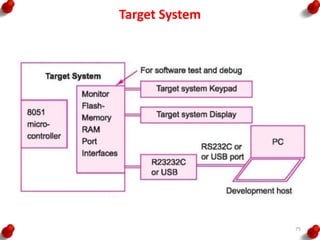

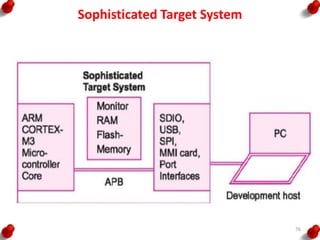

This document provides an introduction to embedded systems, including their components, characteristics, and design process. It discusses the selection of processors and memory devices for embedded systems. It also describes structural units in embedded processors, memory management methods, timer and counting devices, watchdog timers, real-time clocks, and the use of in-circuit emulators for debugging embedded systems.