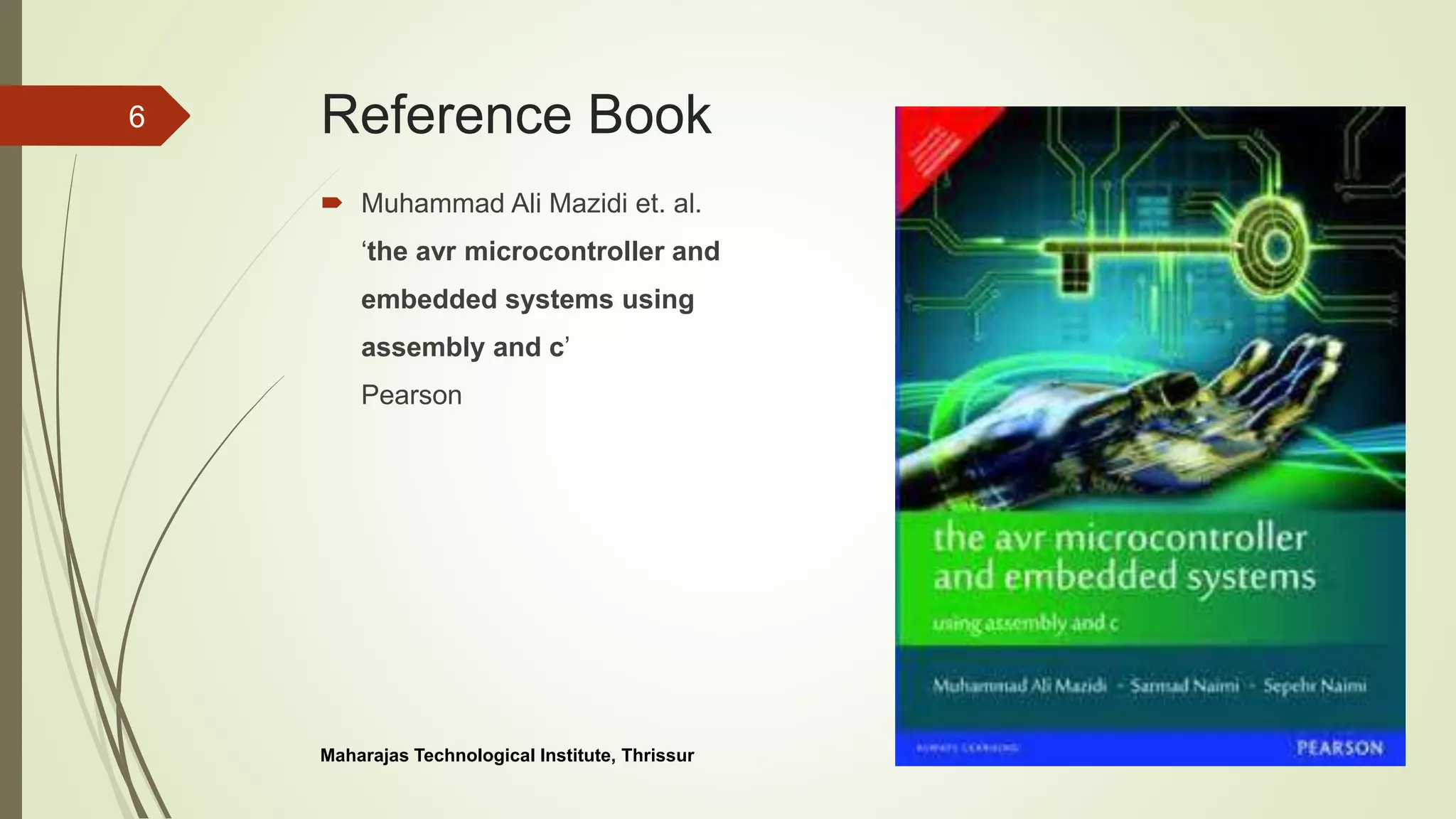

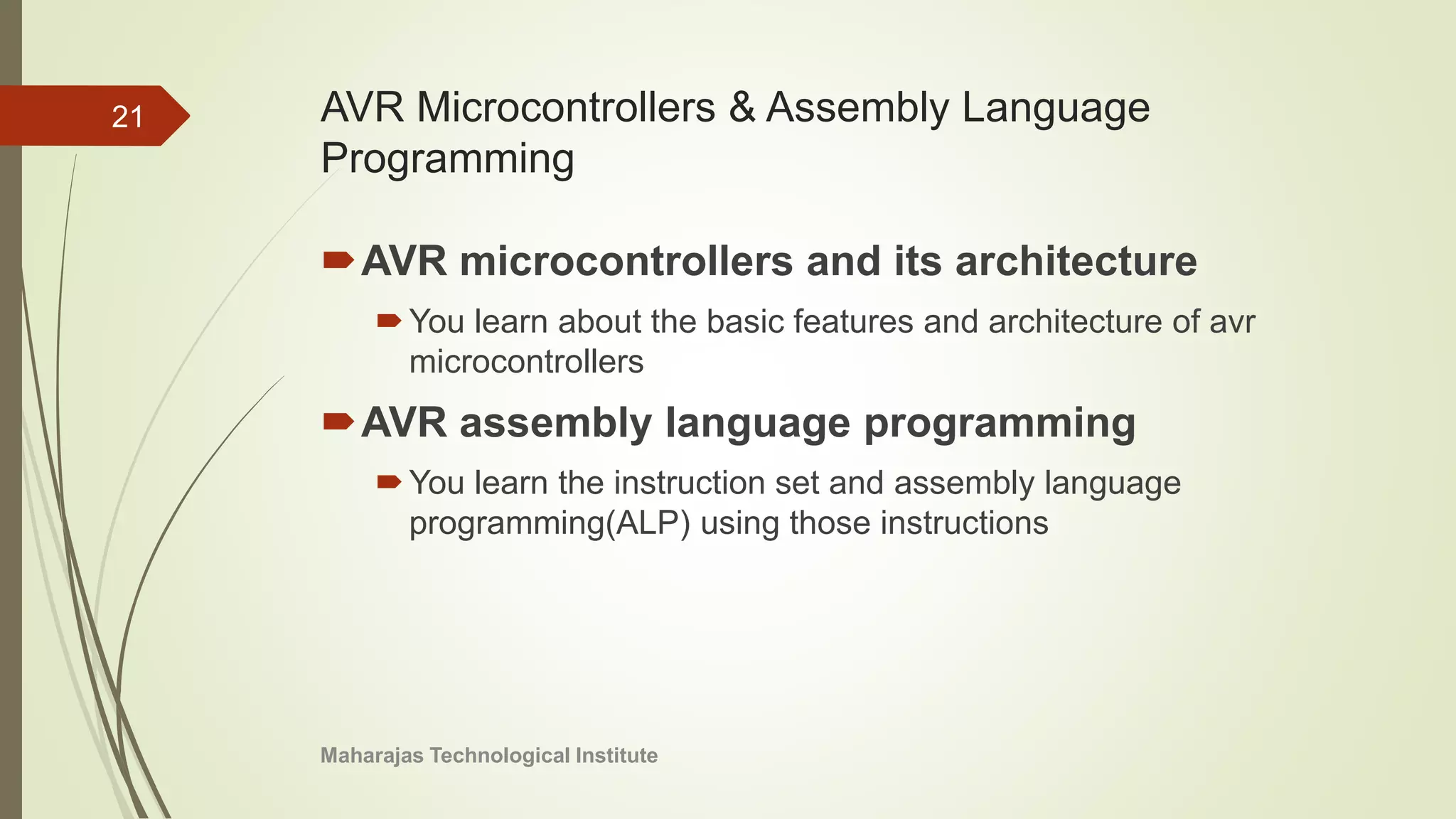

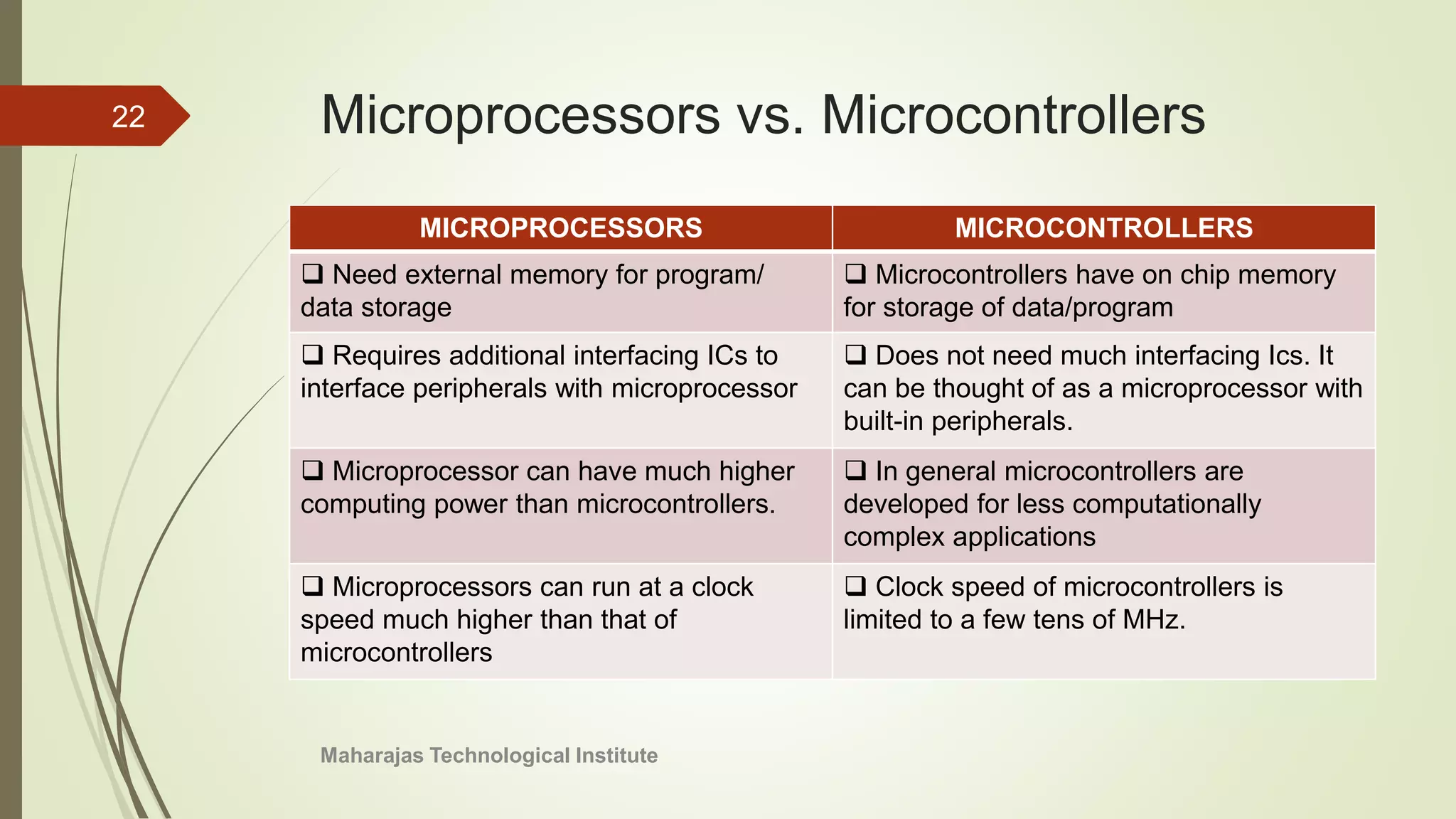

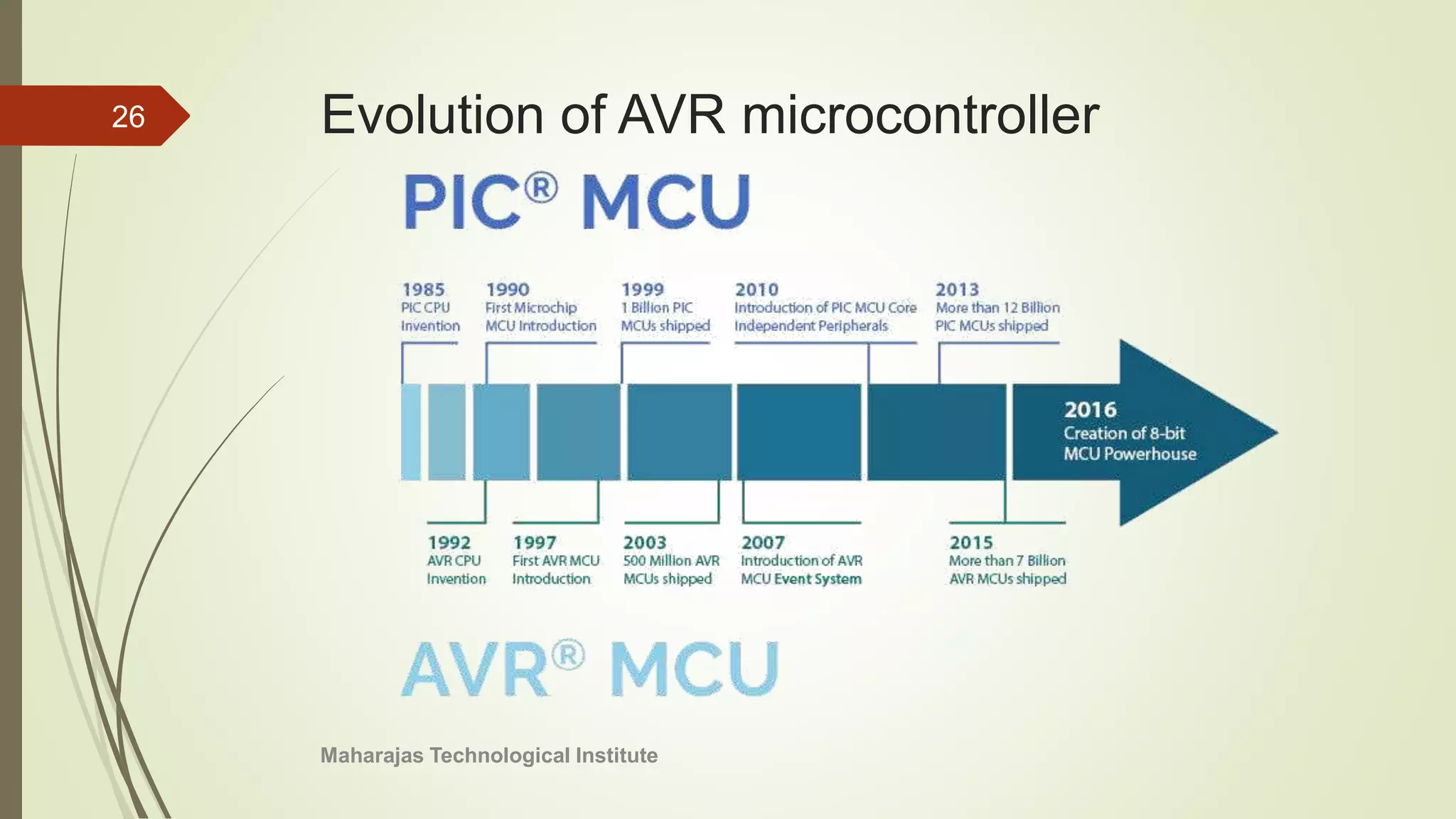

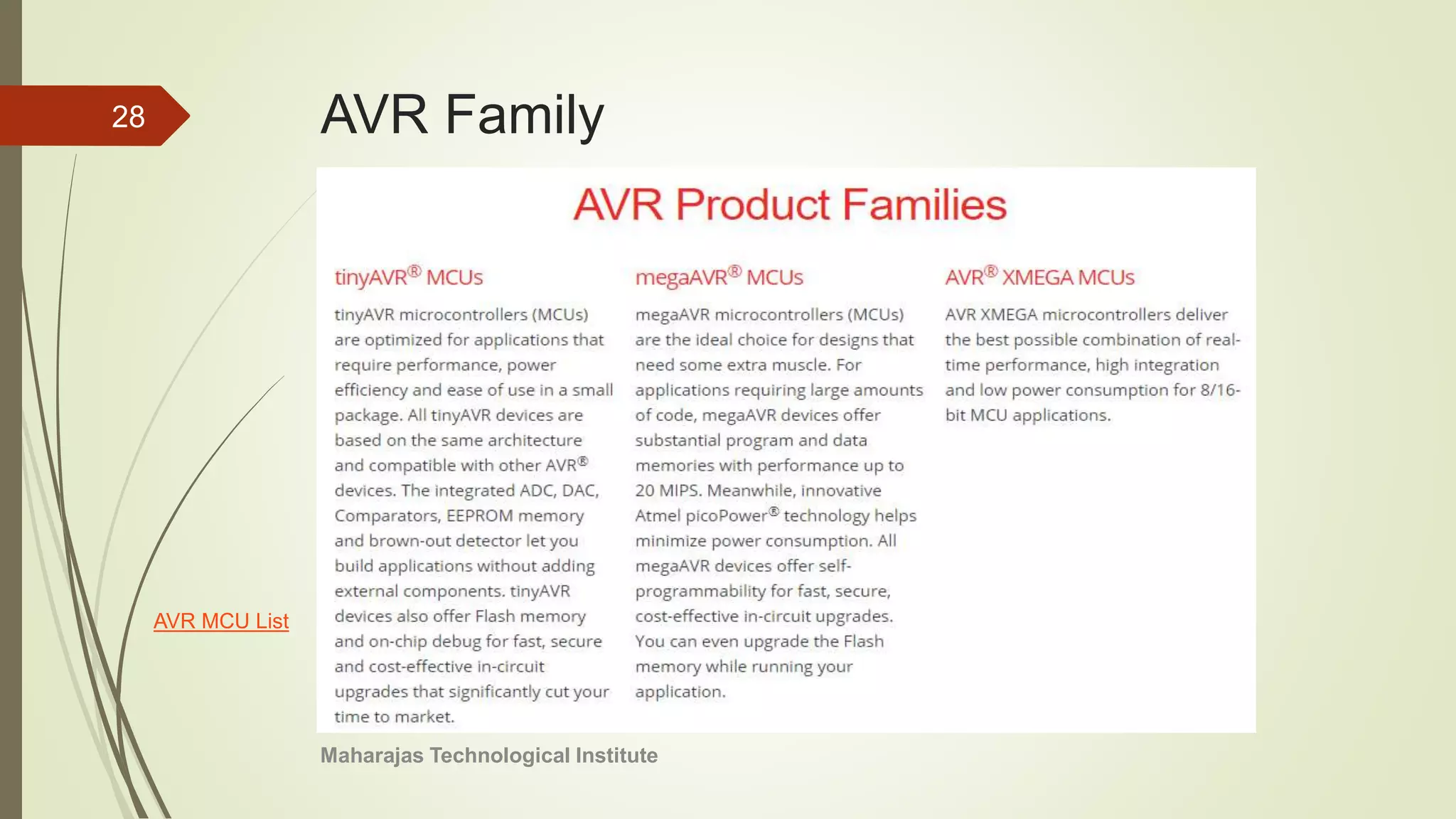

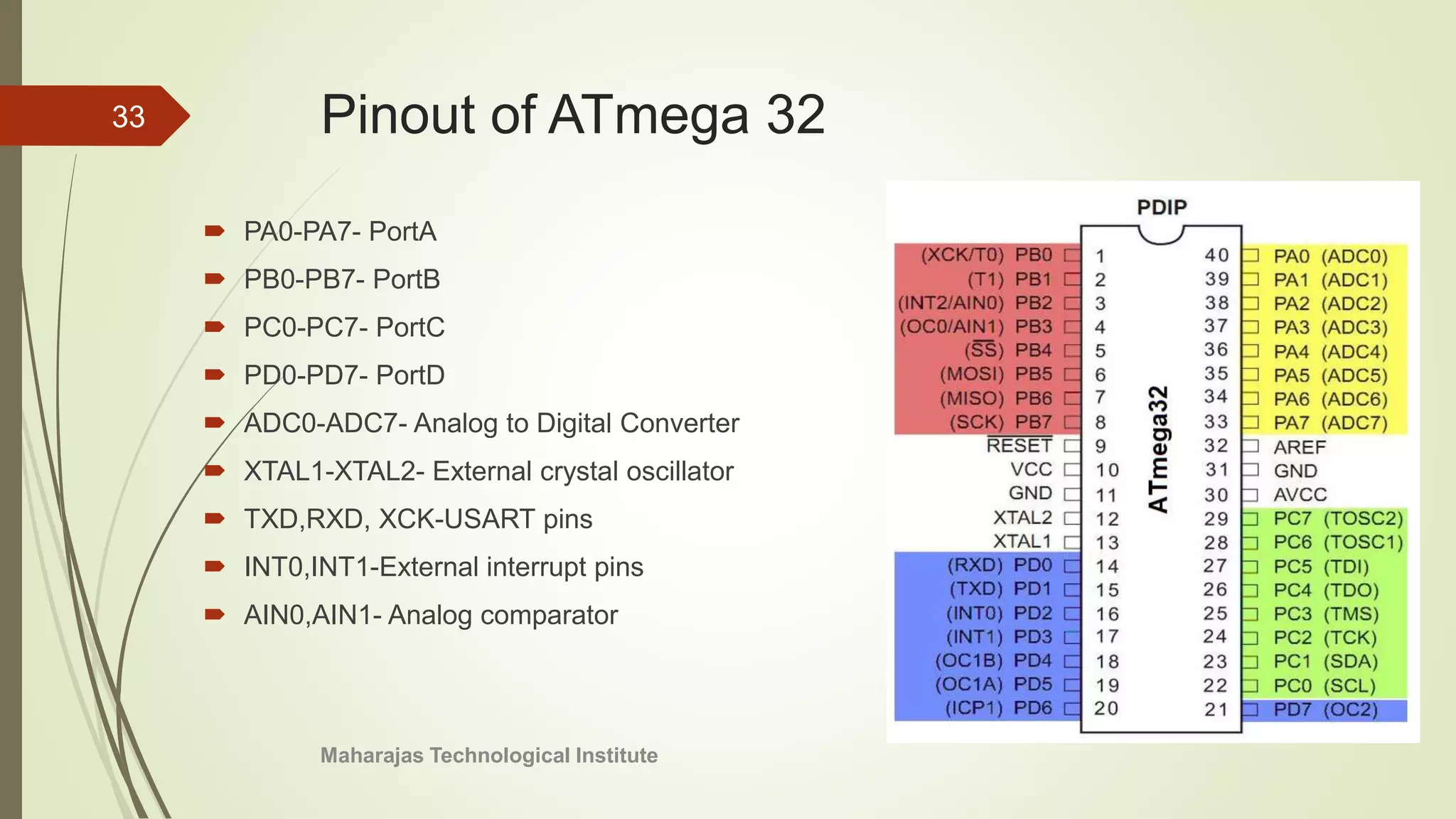

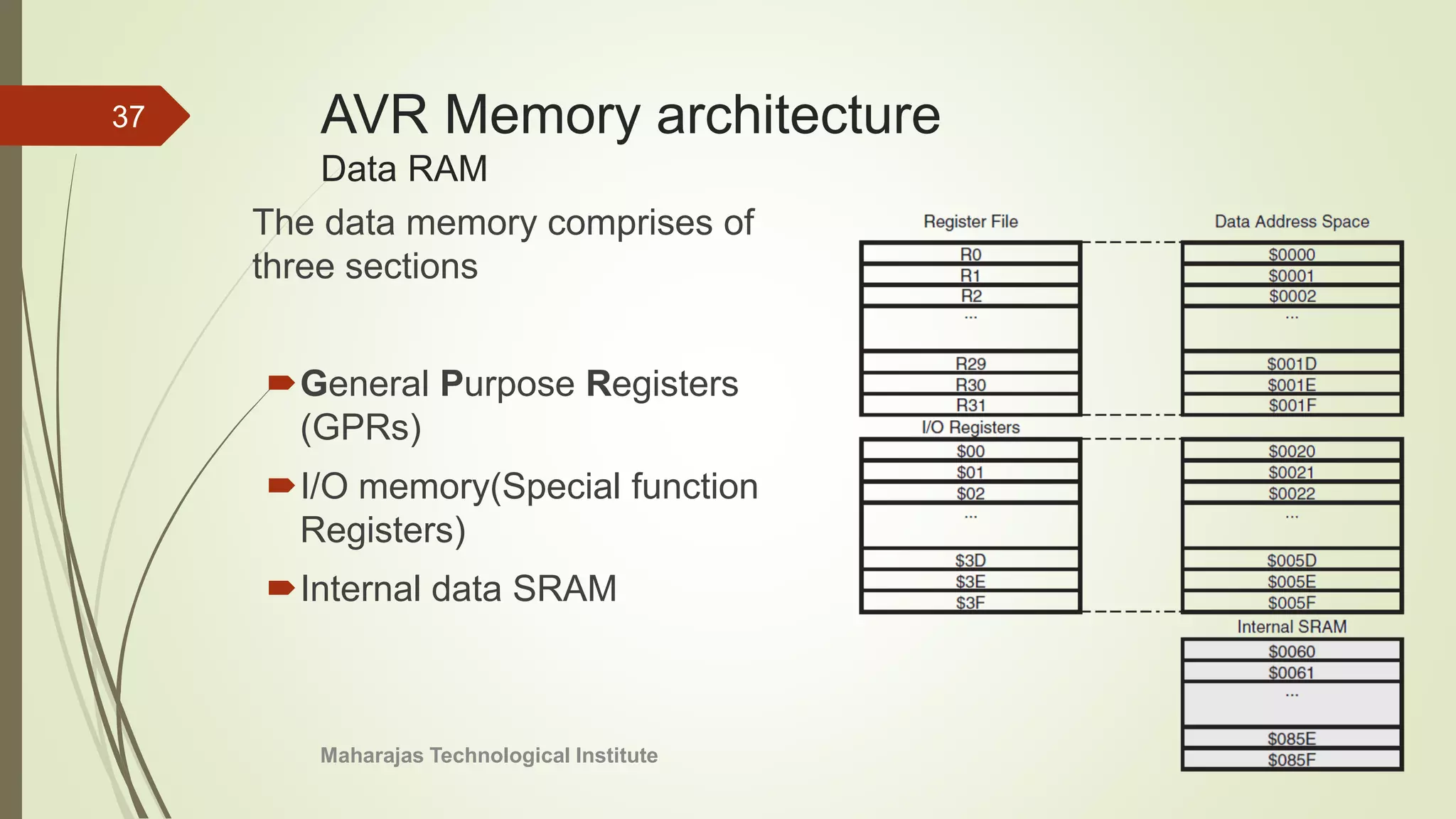

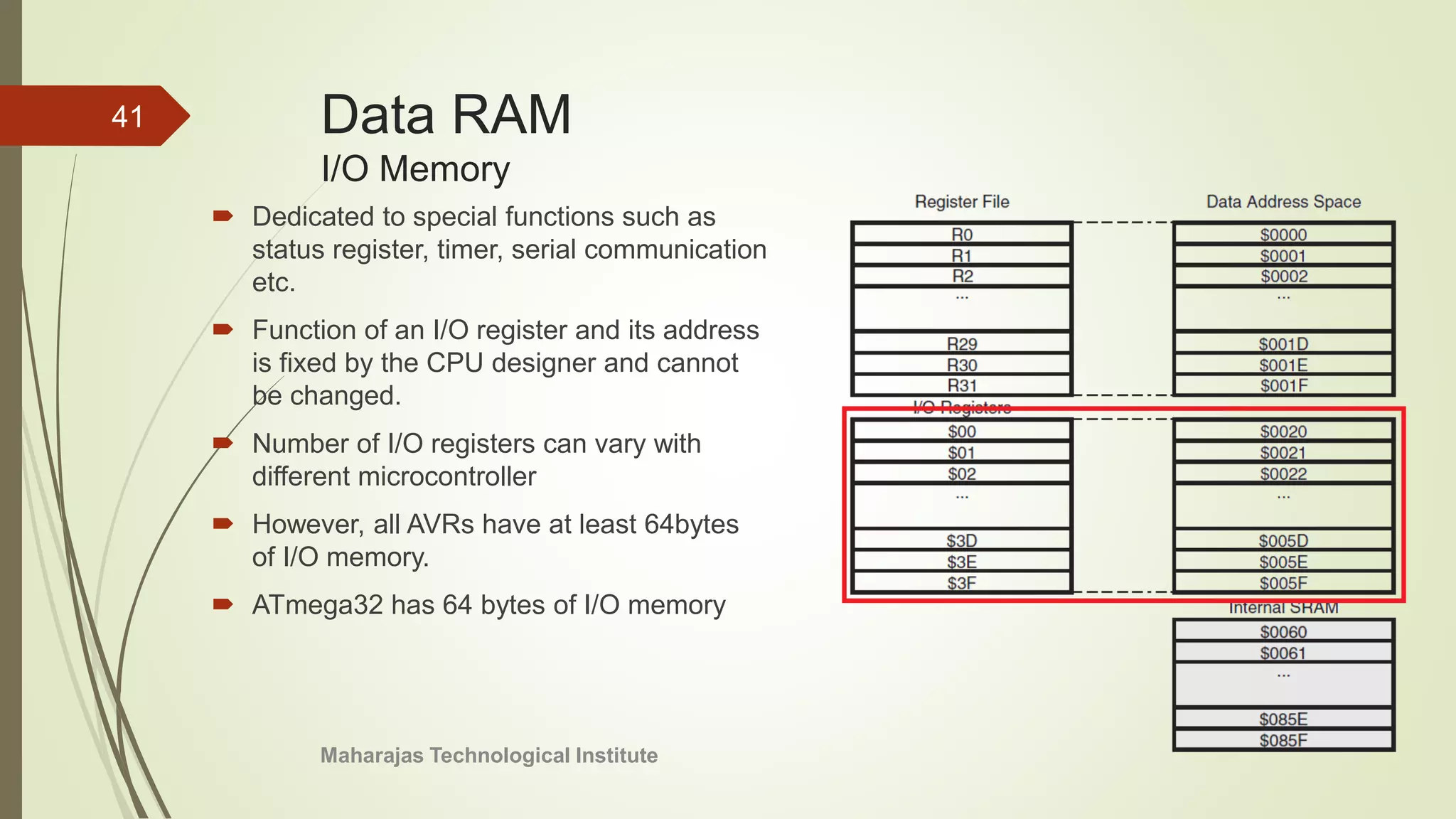

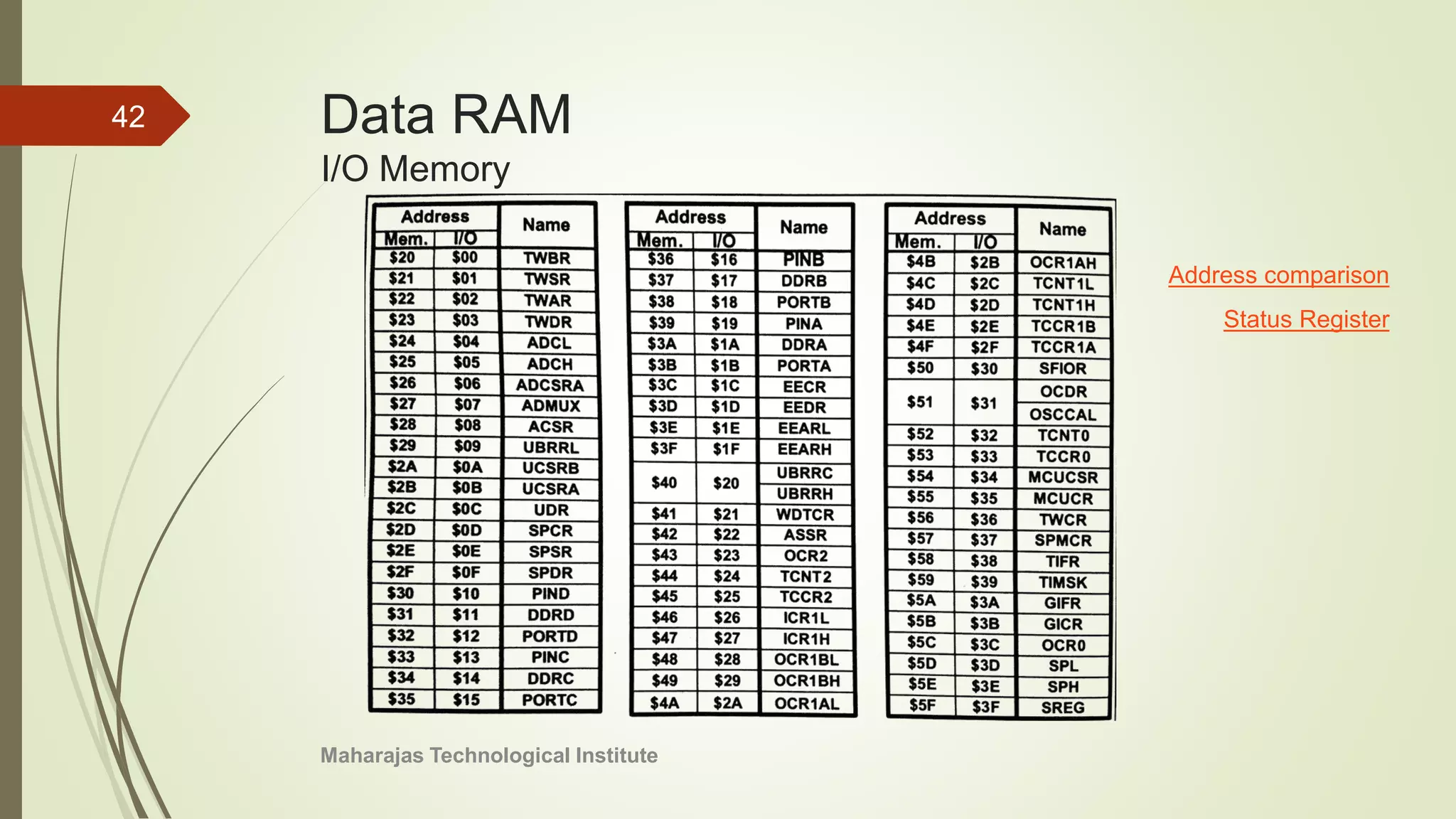

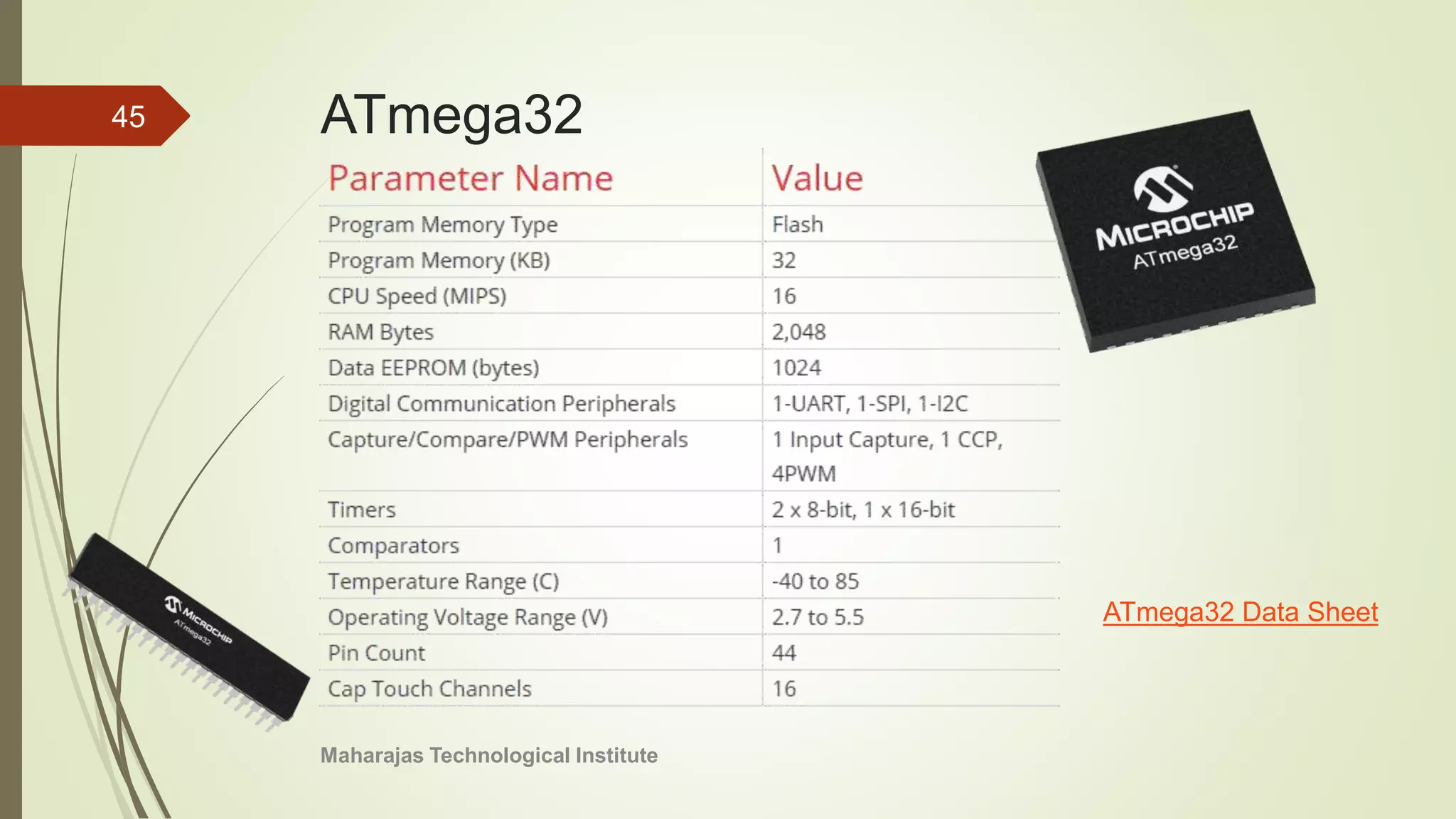

This document provides information about an embedded systems course offered at Maharajas Technological Institute. It includes details like the course code, credits, syllabus modules covering AVR microcontrollers and programming in assembly and C languages. It also discusses concepts like microcontrollers, AVR architecture, memory organization and instruction set of AVR microcontrollers. Examples are given of assembly language instructions like MOV, LDI, STS etc. and applications of embedded systems in various domains.