This document discusses modeling system behaviors and properties. It addresses:

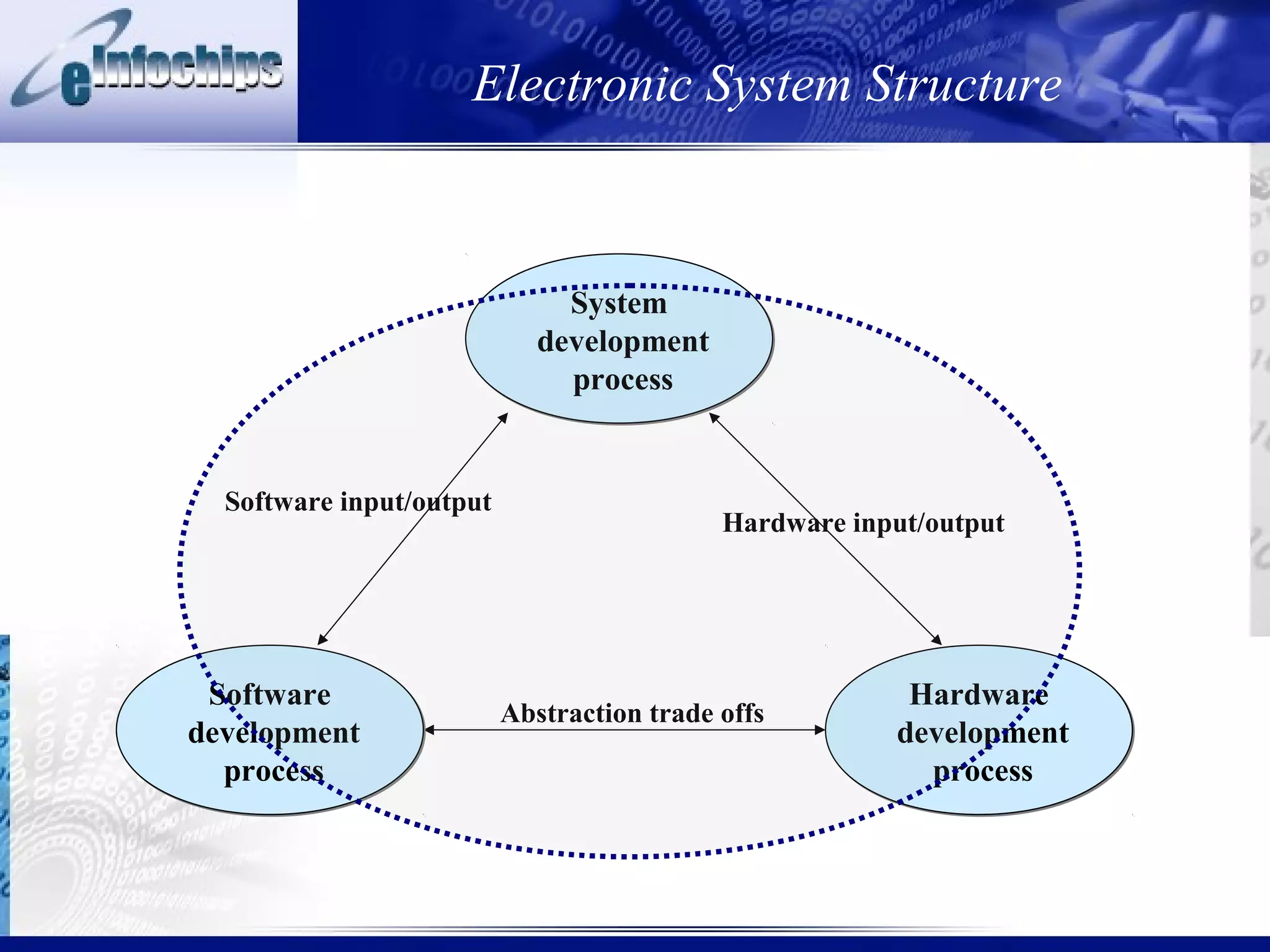

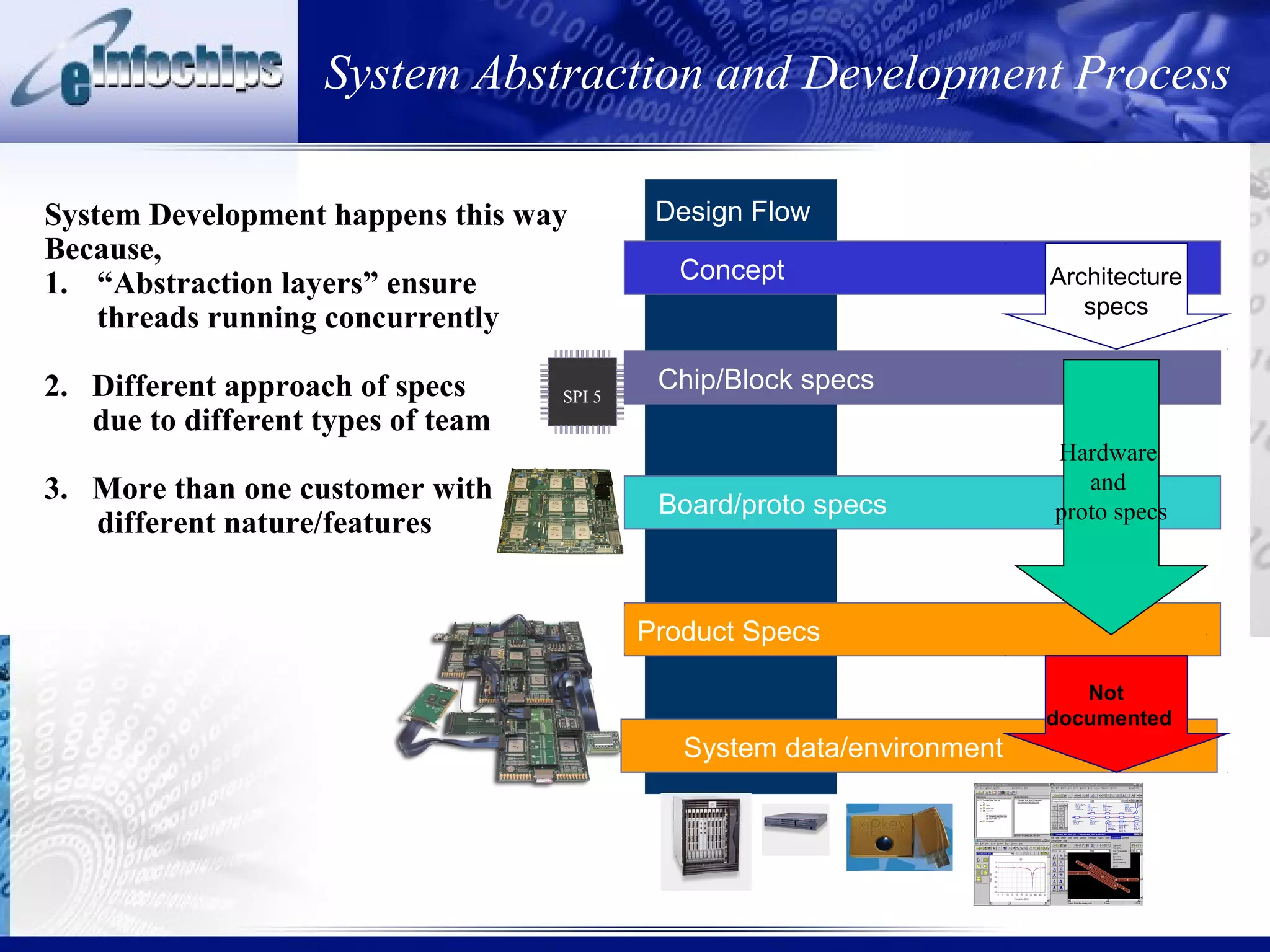

1) System development involves different abstraction layers to allow concurrent work between software and hardware teams with different inputs and outputs.

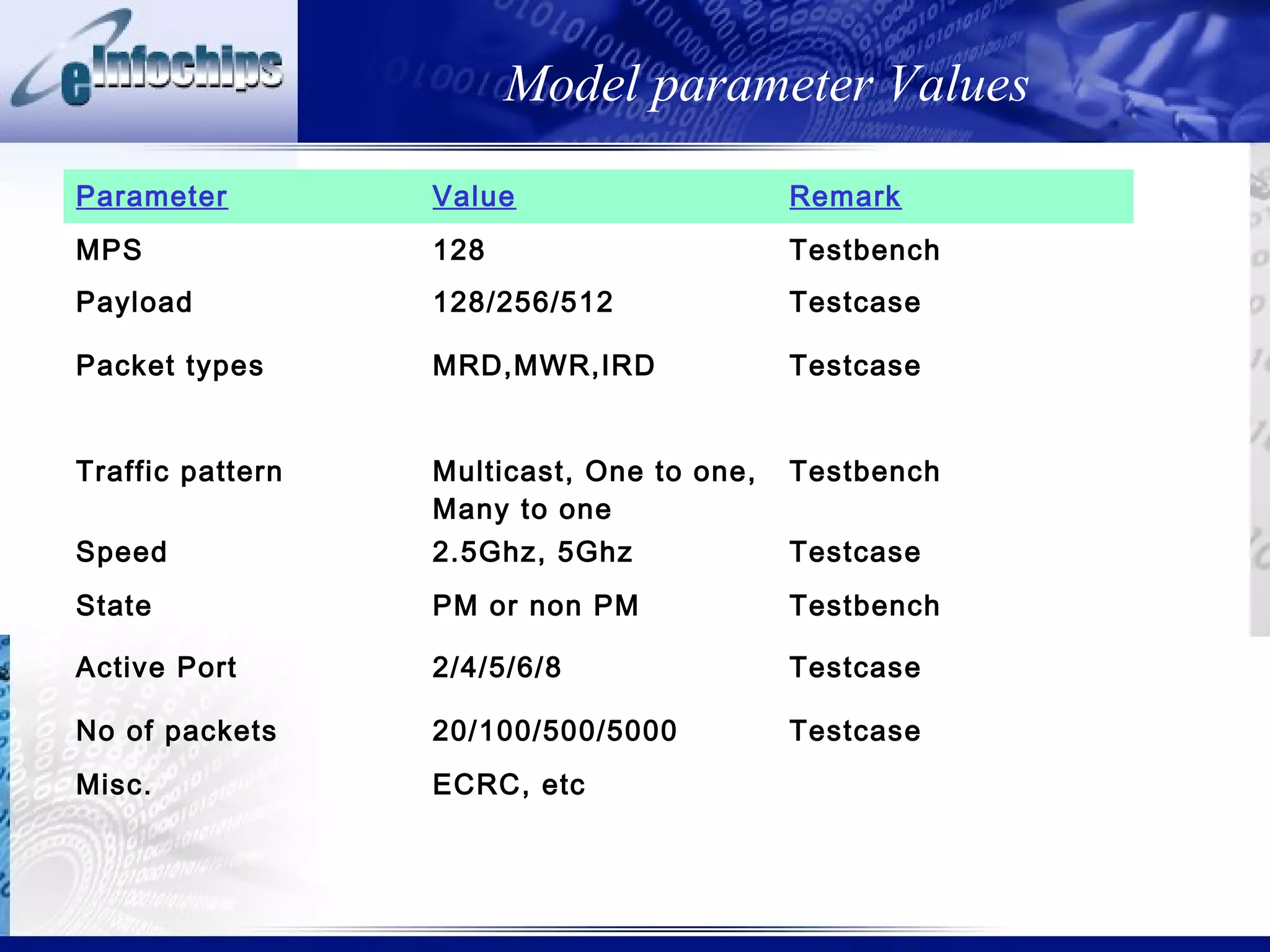

2) Modeling must account for multiple customers with varying requirements.

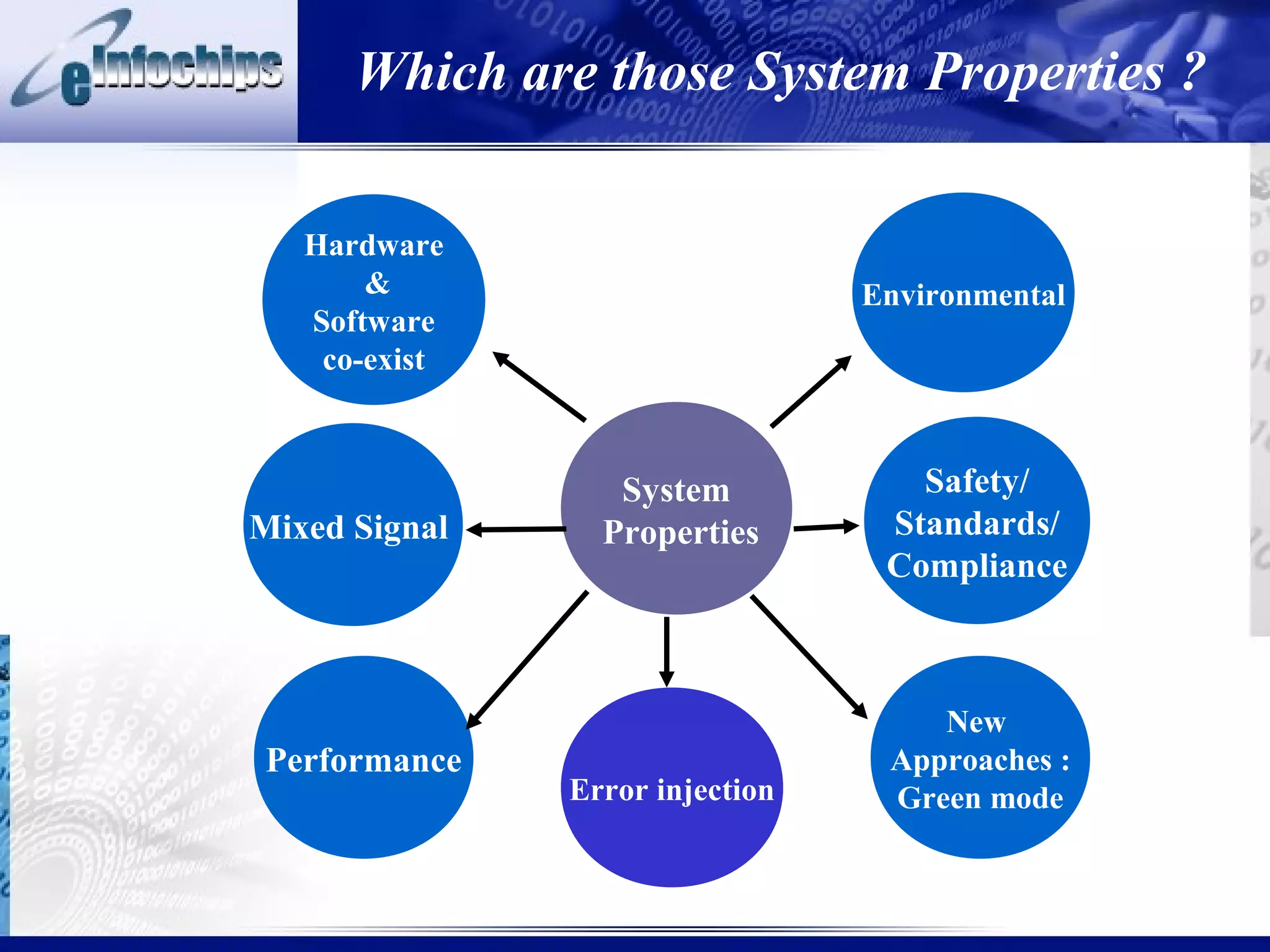

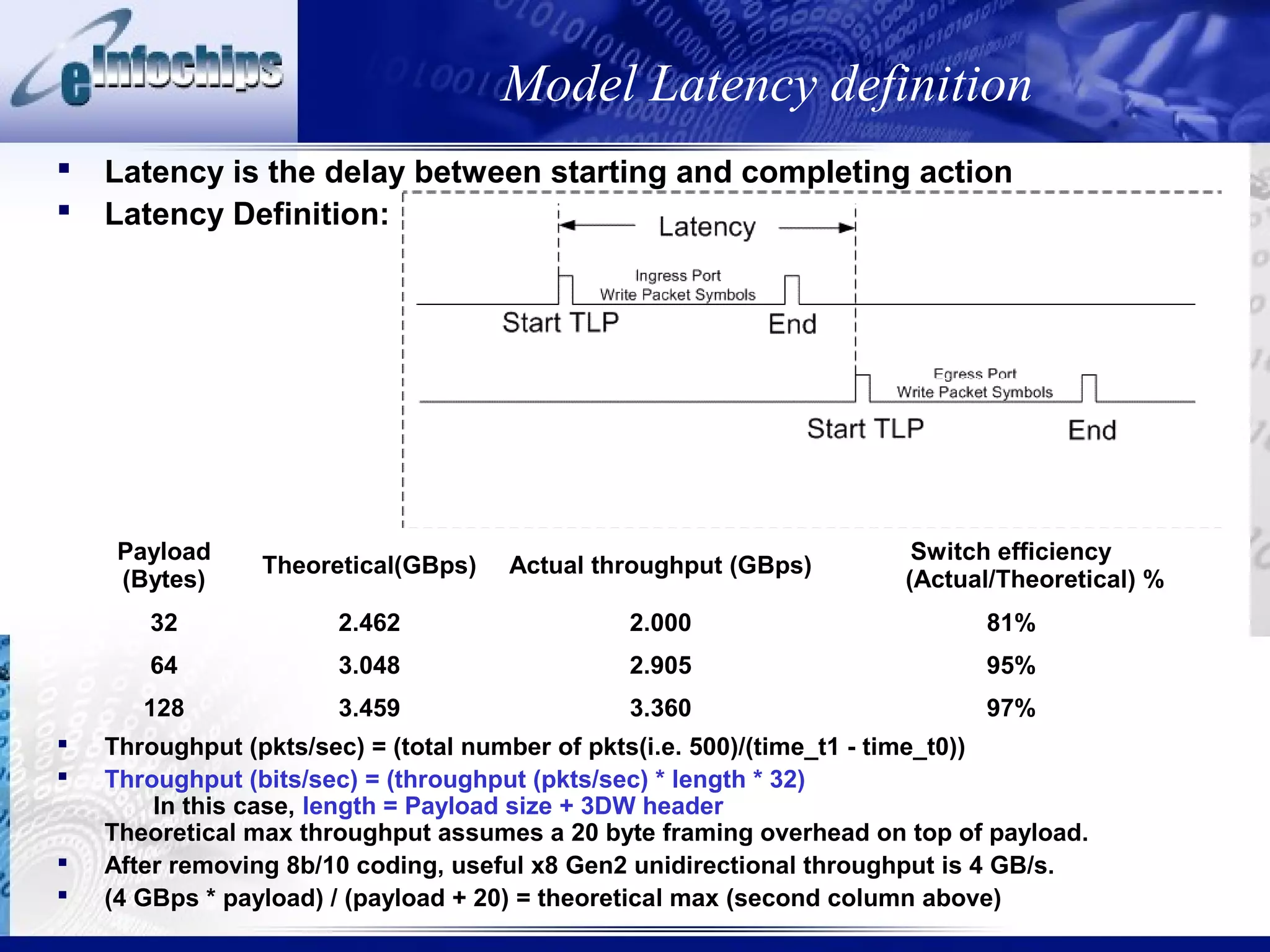

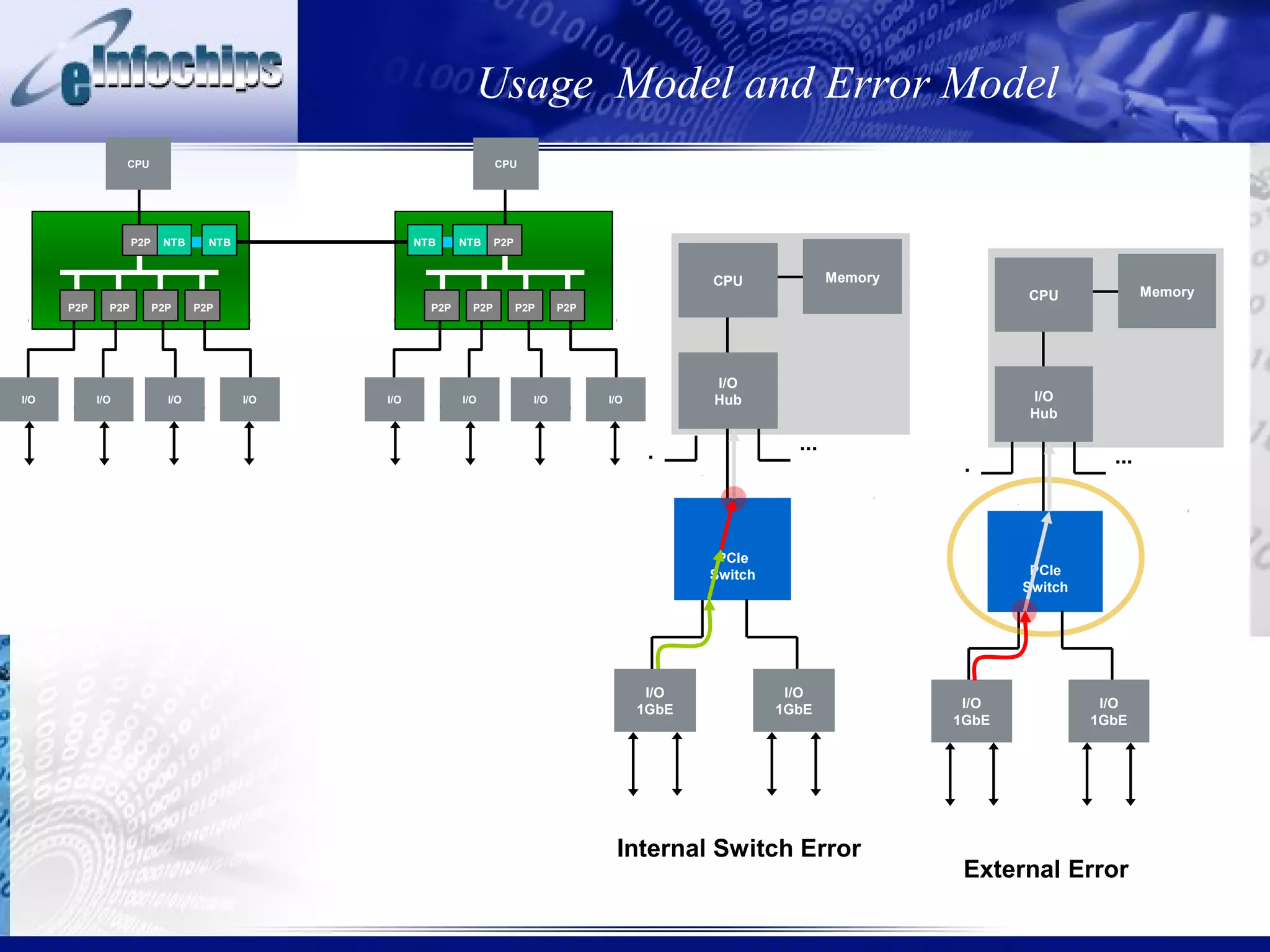

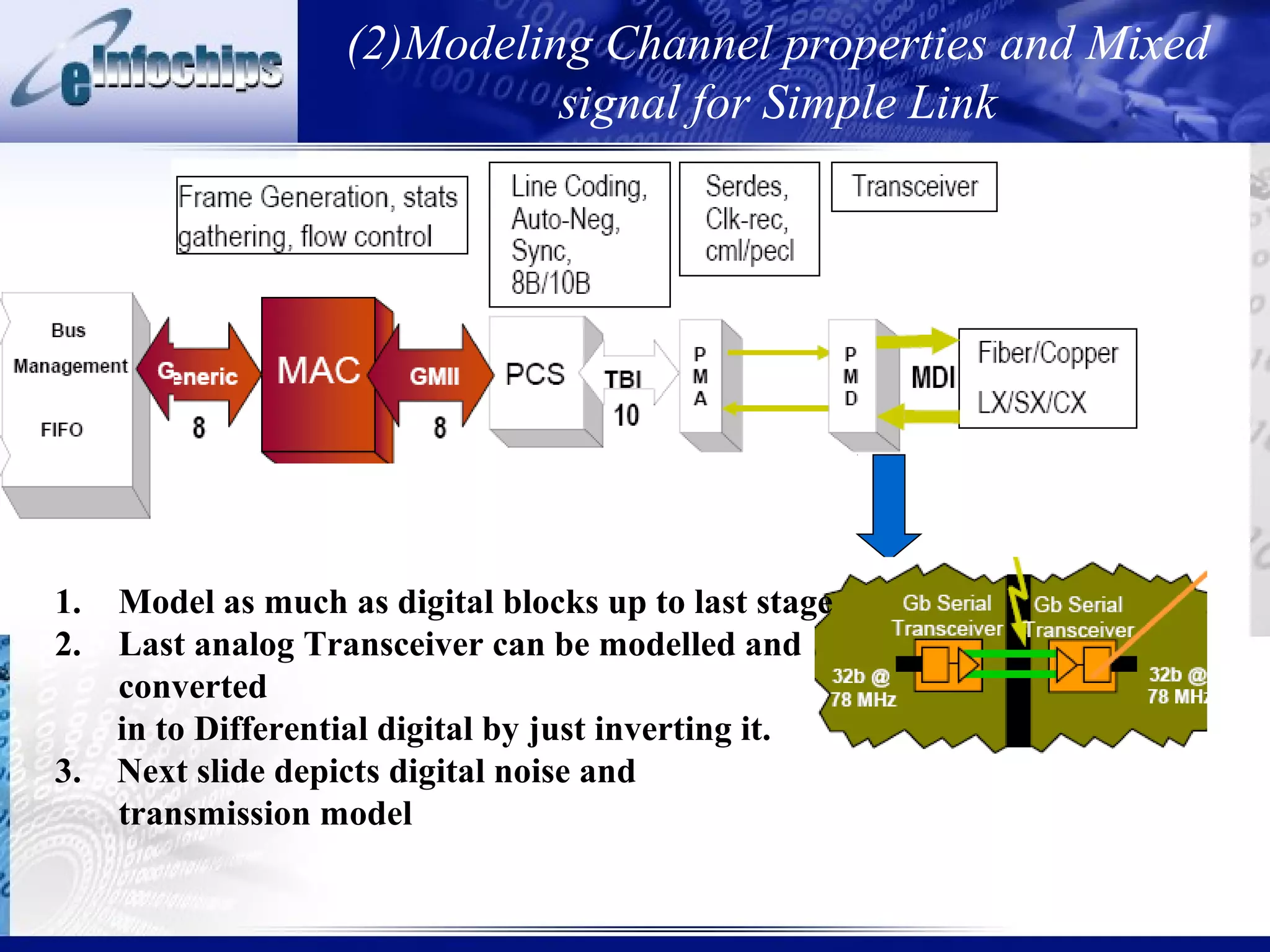

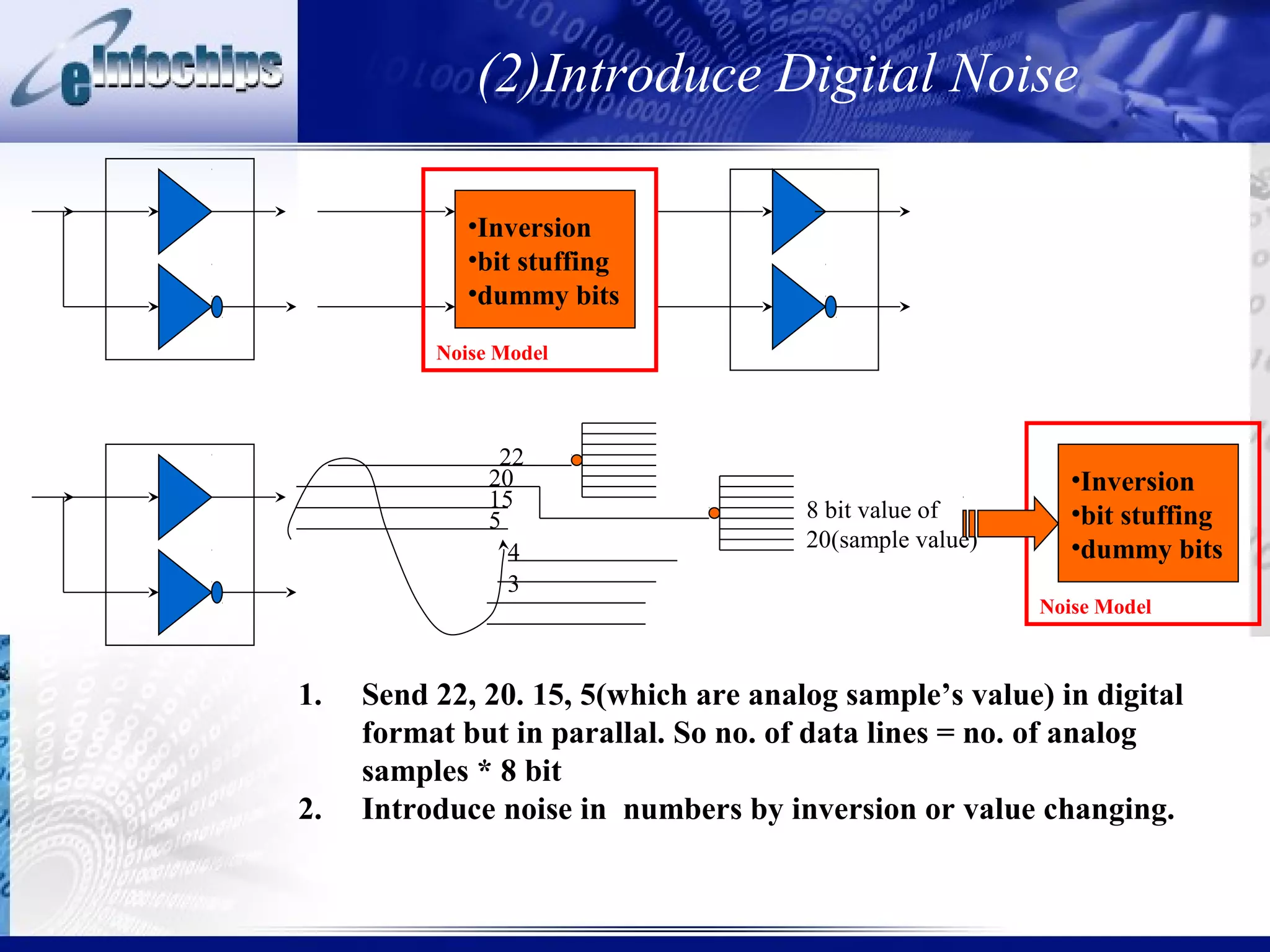

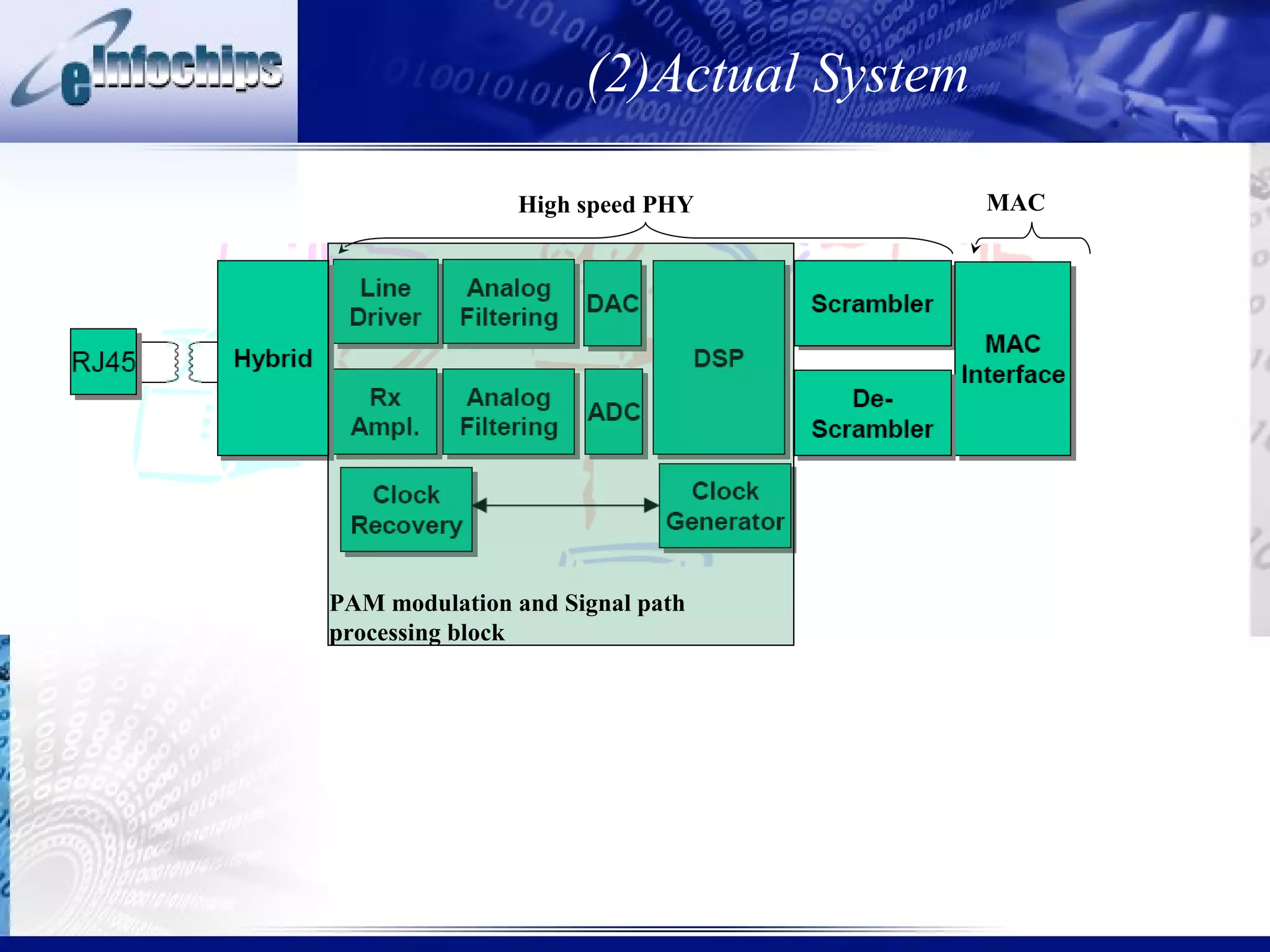

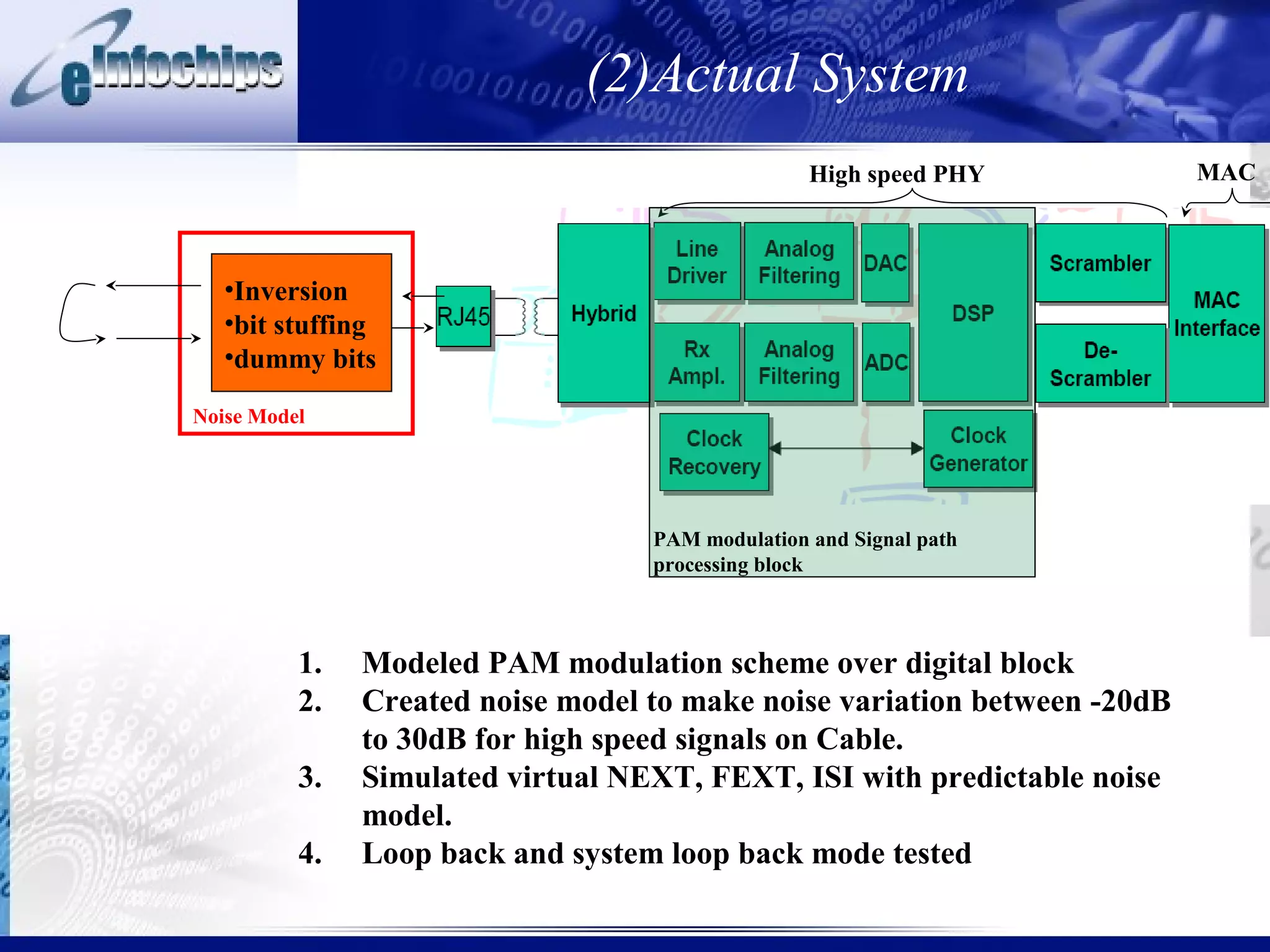

3) Important system properties to model include mixed signal behavior, safety standards, performance, and error injection.