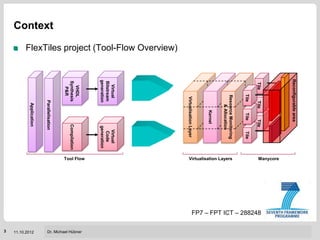

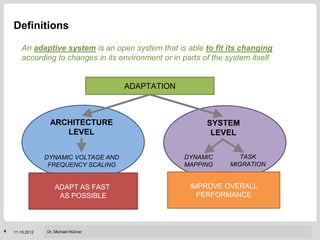

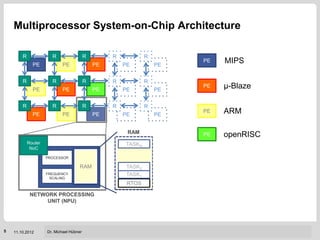

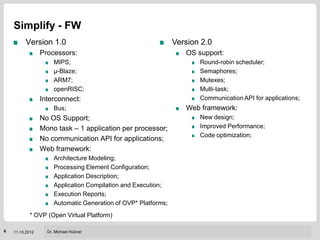

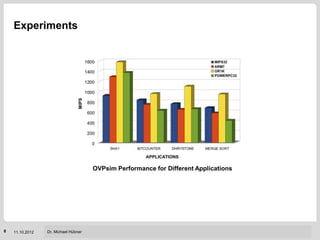

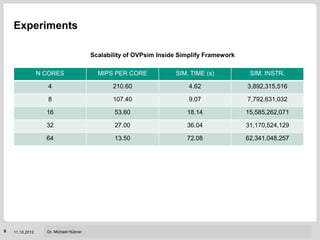

The document discusses Simplify, a framework for enabling fast functional simulation of multiprocessor system-on-chips (MPSoCs). Simplify uses an abstract MPSoC platform model to allow for easy modeling of MPSoC architectures and fast behavioral simulation. It integrates an operating system and supports tasks migration and communication between processors. Experimental results show that Simplify achieves scalable simulation performance and allows for online design, simulation, and debugging of MPSoCs.