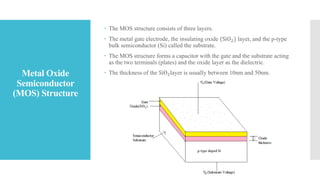

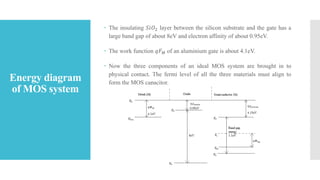

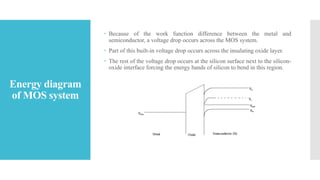

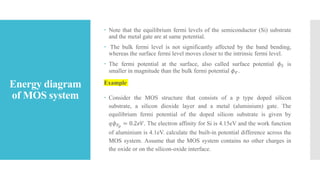

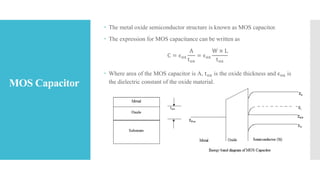

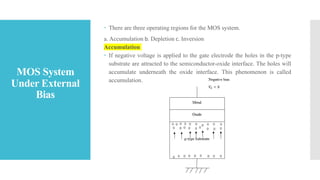

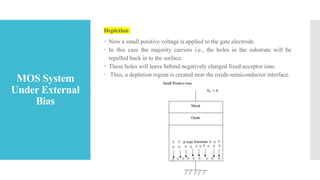

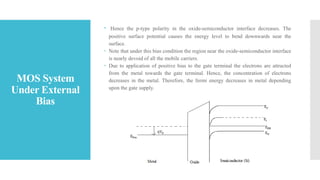

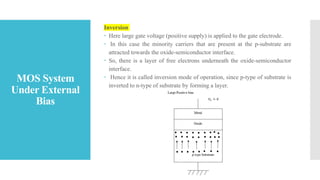

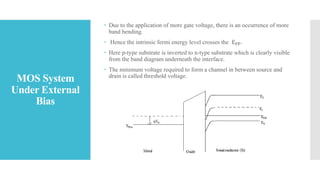

The document summarizes the structure and operation of a metal-oxide-semiconductor (MOS) transistor. It consists of three layers - a metal gate electrode, insulating silicon dioxide layer, and a silicon substrate. The MOS structure forms a capacitor. Applying different biases to the gate electrode puts the device in one of three operating modes: accumulation, depletion, or inversion. In accumulation, holes are attracted to the interface. In depletion, holes are repelled, leaving an uncharged region. In inversion, electrons are attracted, inverting the conductivity type at the interface.