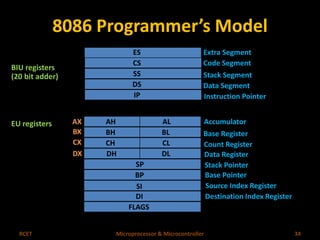

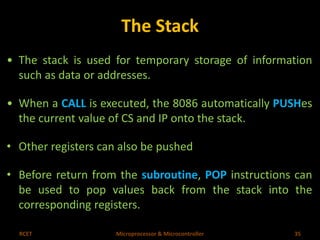

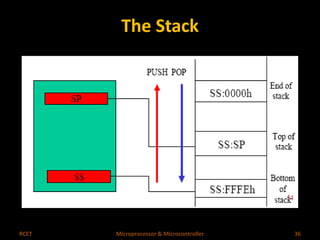

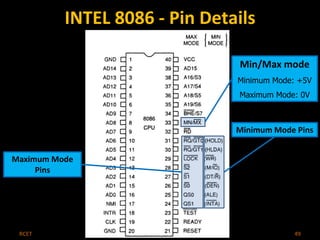

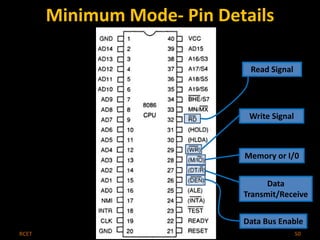

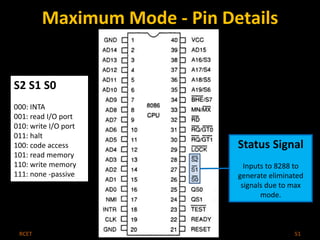

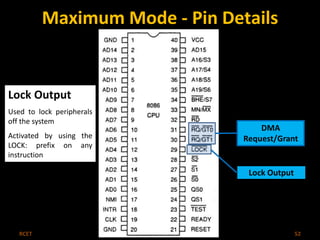

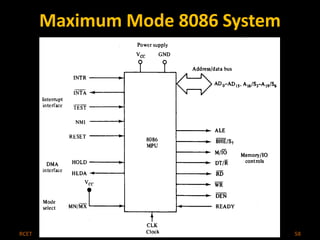

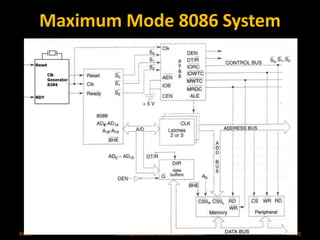

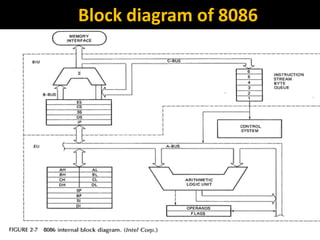

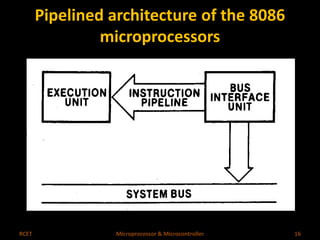

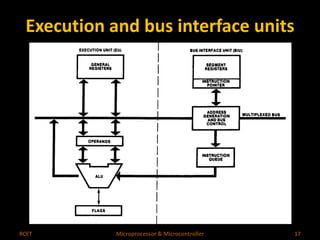

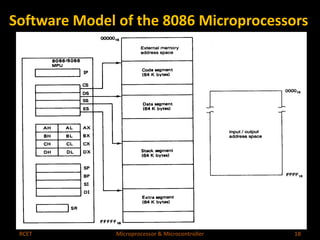

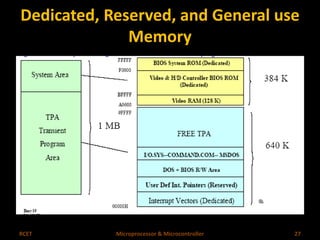

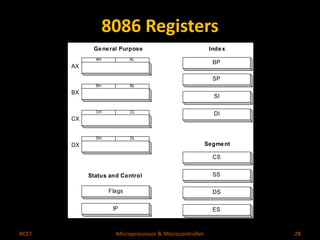

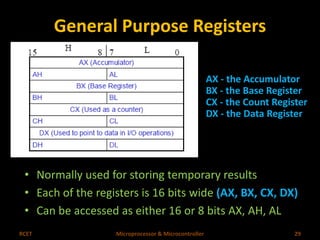

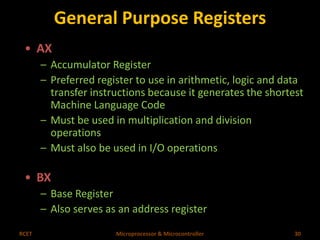

This document provides an overview of the Intel 8086 microprocessor. It discusses the software architecture, including memory segmentation, registers, stack, and I/O space. The hardware architecture is also covered, such as the pin details, minimum/maximum mode, and address generation. Programming the 8086 using assembly language is mentioned as well.

![Pointer and Index Registers

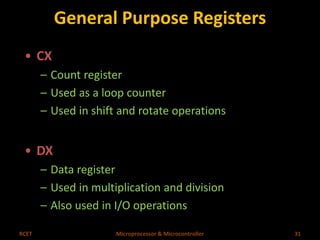

• All 16 bits wide, L/H bytes are not accessible

• Used as memory pointers

– Example: MOV AH, [SI]

• Move the byte stored in memory location whose address is contained in

register SI to register AH

• IP is not under direct control of the programmer

RCET Microprocessor & Microcontroller 32](https://image.slidesharecdn.com/8086module12-work-141214203740-conversion-gate01/85/8086-module-1-2-work-32-320.jpg)