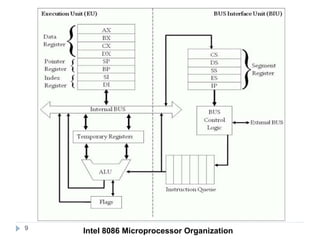

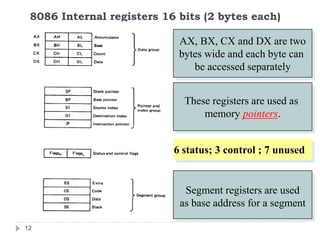

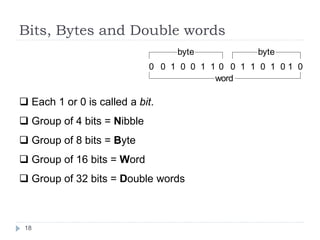

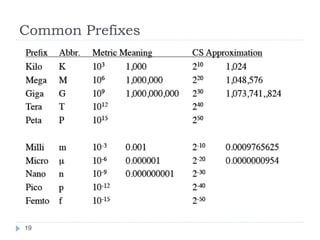

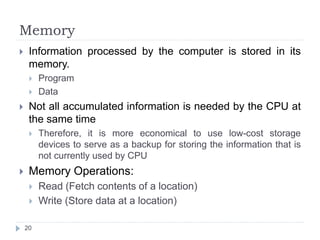

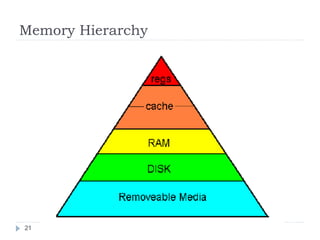

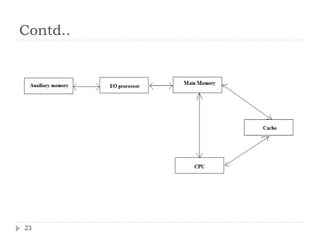

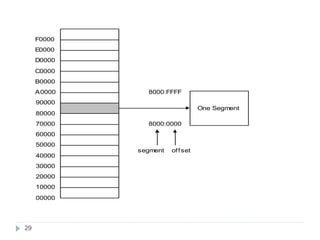

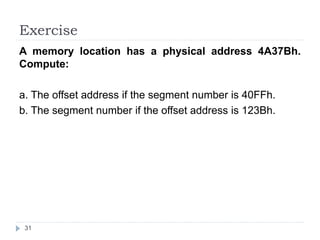

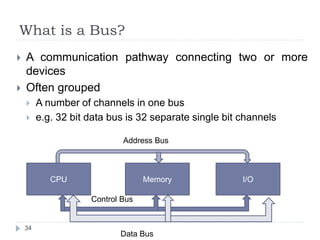

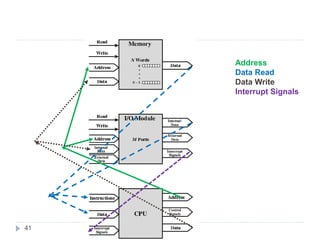

This document provides an overview of computer organization and assembly language concepts including the CPU, registers, memory, and system bus. It summarizes that the CPU contains an execution unit and bus interface unit, uses various registers like general purpose registers and segment registers to store and access data and memory addresses. It describes different types of memory like RAM, ROM, and cache, and how memory is organized into segments and addressed using segment:offset notation. It concludes with an explanation of the system bus that connects the CPU, memory, and I/O devices, and the types of data transfers that occur over the bus.