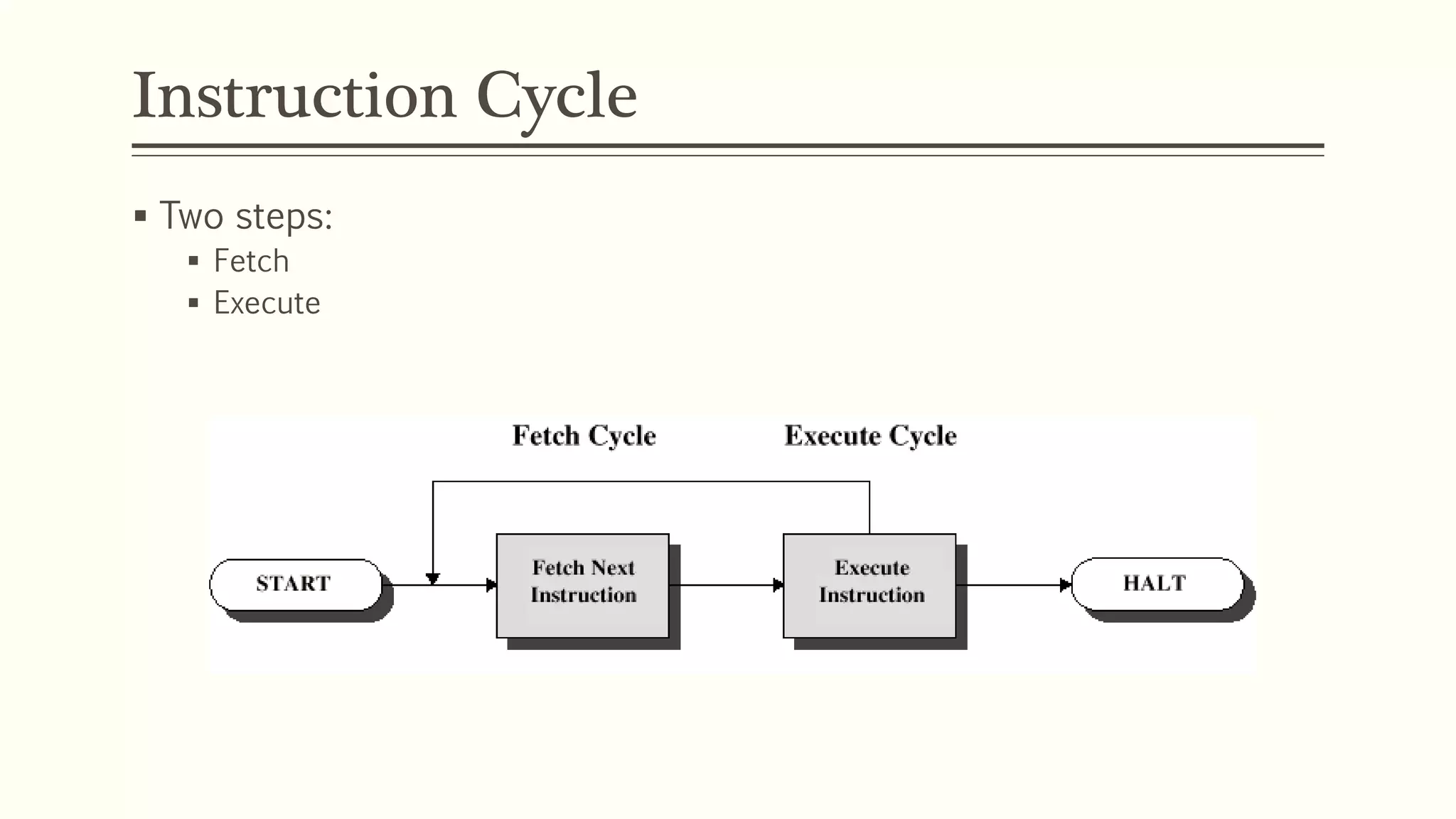

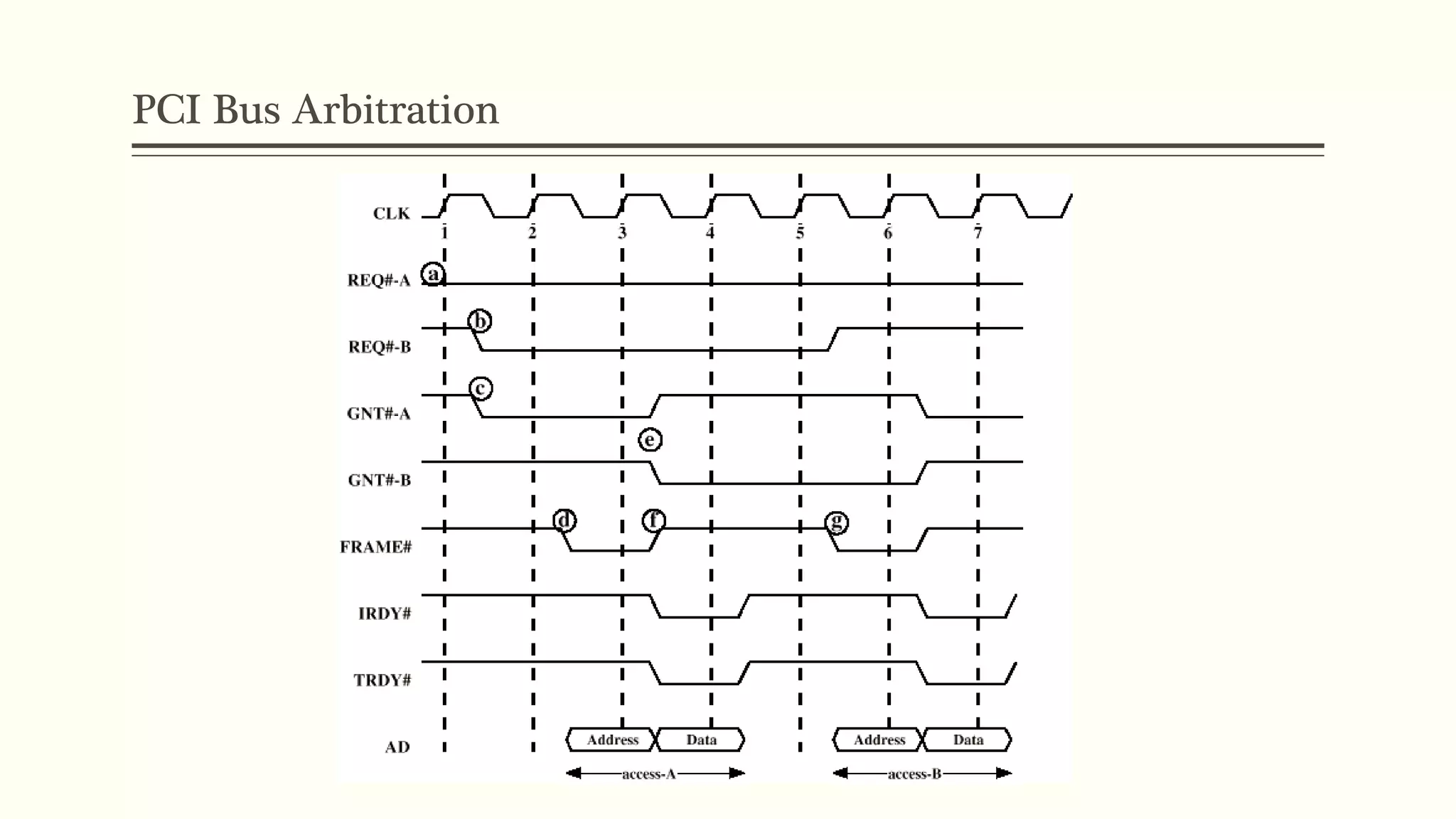

The document discusses the components of computer architecture, focusing on the control unit, arithmetic and logic unit, and system buses essential for data and instruction flow. It describes the instruction cycle, fetch and execute processes, and various types of buses, including data, address, and control buses, essential for performance and interconnection. Additionally, it provides details about PCI bus architecture and its functionalities for device communication and transaction management.